Vivado下set_multicycle_path的使用说明

vivado下多周期路径约束(set_multicycle_path)的使用,set_multicycle_path一般在如下情况下使用,源时钟和目的时钟来自同一个MMCM、PLL等同一个IP核,或者源时钟和目的时钟是同一个时钟。只要两个时钟间可进行静态时序分析就可以。在这种情况下,即使不加set_multicycle_path的约束,只要时序分析能过,也是没有问题的,添加set_multicycle_path的作用是为了防止约束过紧,从而侵占了本应该让位其他逻辑的布局、布线资源,还有可能造成其它关键路径的时序违例或建立时间裕量变小的情况,这在资源利用率很高时尤为突出。多周期路径约束的好处在于使布局、布线工具优先考虑其它关键路径。 下面摘抄了一篇比较好的文章介绍。

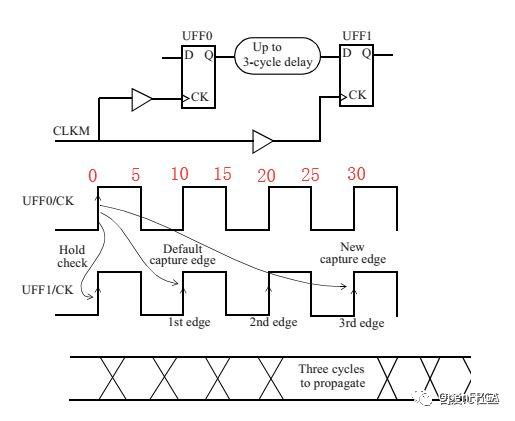

通常情况下,两个同步的reg进行timing check时,组合逻辑的delay必须在一个时钟周期内到达,才能满足setup的时序。但在某些情况下,从一个寄存器输出到另外一个寄存器的data 端需要不止一个cycle的时间,而且又不影响逻辑的功能。此时,我们可以将这样的path约束为multicycle path。图1所示为一个3cycle的multicycle path的电路结构图和波形图。

因此,我们可以用下面的命令来定义约束:

create_clock -name CLKM -period 10 [get_ports CLKM]

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

setup检查:

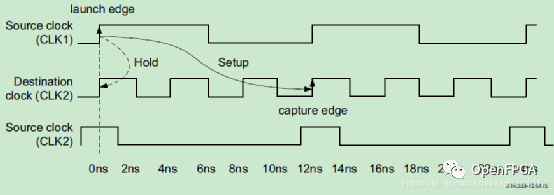

默认情况下,当UFF0/CK作为launch clock时(T=0ns时),在T=10ns时UFF1/CK采集到前一级过来的数据。

图1 multicycle path下的 setup时序检查

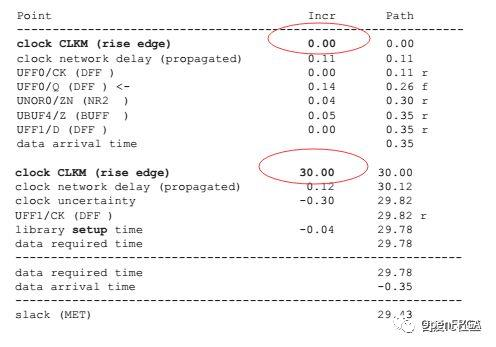

但是当我们通过以上的命令设置了3个cycle的multicycle path的约束之后,launch clk的沿推到了T=30ns。因此,两个寄存器之间那段组合逻辑的delay要求就放松到了近三个时间cycle。这种情况下setup是比较容易满足的。对应的setup 检查时序报告如下图2所示。

图2 setup检查时序报告

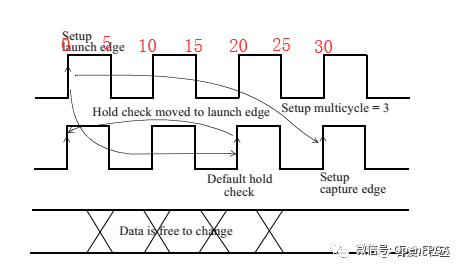

hold检查:

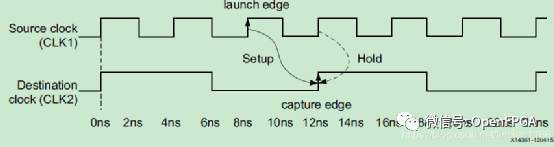

默认情况下,hold检查的沿应该是在T=20ns时刻(较setup capture edge早一个cycle)。这种检查机制好不好呢?显然不好。为什么呢?(可以自己画波形,其实波形已经在图3中了)。从图中看到这样的hold 检查方式,会导致hold可能过度悲观,很难满足hold time的要求。

图3 multicycle path下的 hold时序检查

因此,我们需要像单cycle check的情况一样,即hold检查的沿应该和launch clk的edge一致(T=0时刻)。这样我们的hold time check比较容易满足,也比较科学。那么如何实现这种想法呢?我们引进了如下约束命令:

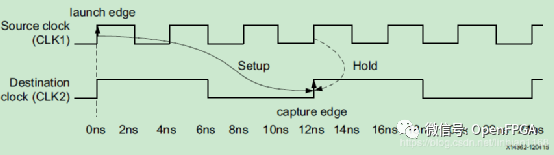

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

这里面的数字“2”是指将默认的hold check edge往前推2个时钟周期,即从原来的T=20ns时刻往前移到T=0ns时刻。对应的hold时序检查报告如下图3所示。

图4 hold检查时序报告

因此,在我们给设计写约束文件时(定义multicycle path时),需要同时定义如下命令:

set_multicycle_path N -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

set_multicycle_path N-1 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

如果只定义了-setup 3 而没有定义-hold时,工具hold check时, 默认的 clock edge为capture edge(setup timing check时)前一个cycle的那个edge。

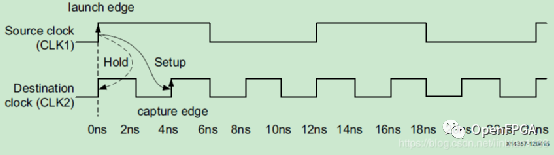

上面的例子是两个寄存器是被同一个CLK所驱动的。下面分析一下在两个不同时钟主频的情况下使用set_multicycle_path的情况。可以分为三种情况:

(1)从慢时钟到快时钟的同步跨时钟路径

图5 思考题波形图

set_multicycle_path N -setup -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

(2)由快时钟域到慢时钟域

set_multicycle_path N -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -from [get_clocks CLK1] -to [get_clocks CLK2]

(3)两个时钟存在相移

此种情况用如下约束

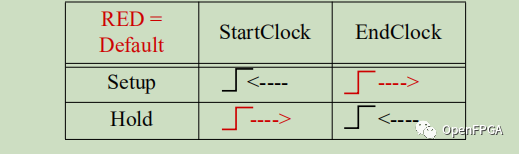

setup or hold和start or end时钟的对应关系如下

看完本文有收获?请转发分享给更多人

NOW现在行动!

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程【Vivado使用误区与进阶】总结篇【Vivado那些事】Vivado下头文件使用注意事项【Vivado那些事】Vivado中常用的快捷键(一)F4键【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

HDL Designer Series(HDS)介绍

SystemVerilog数字系统设计_夏宇闻 PDF

Verilog 里面,always,assign和always@(*)区别

FPGA上如何求32个输入的最大值和次大值:分治一文读懂TCP/IP!《RISC-V on T-Core》学习笔记新年愿望是什么?先送大家一波开发软件谈谈FPGA(入门)学习的两种方式ZYNQ-迷恋ZYNQ-FPGA开发板资源分享

零基础入门FPGA,如何学习?

黑金全部开发板资料(FPGA+ZYNQ)分享

点击上方字体即可跳转阅读哟

点个在看 你最 好看

439

439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?