接口综合类型

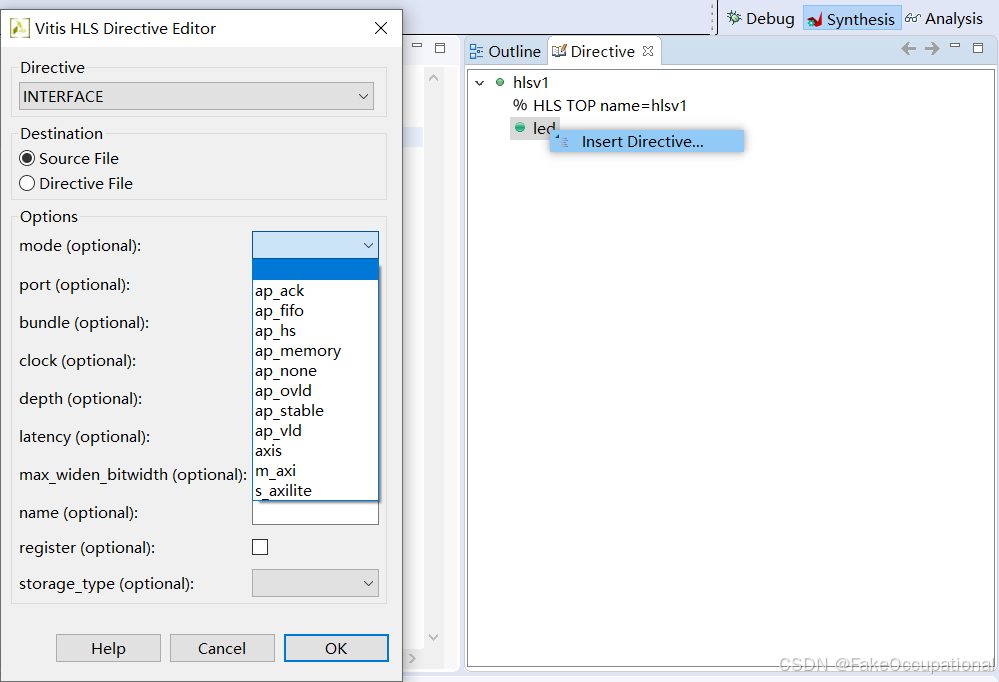

- 在 Vitis HLS(High-Level Synthesis)中,接口类型用于指定模块的控制信号和通信方式,从而影响硬件实现时的控制逻辑、时序以及数据传输方式。Vitis HLS 使用以下接口类型

ap_clk,ap_fifo,ap_hs ,ap_memory,ap_none,ap_ovld,ap_stable,ap_vld,axis,m_axi和s_axilite来指定 RTL IP 是否使用模块级握手信号实现。

ap_none

- 最简单的接口,没有与之关联的控制信号。

ap_stable

- ap_none类似的协议,它不涉及其他控制信号或相关硬件。 ap_stable 适用于不经常更改的 inputs,即除了 reset(重置)之外通常保持稳定的 inputs。

ap_ovld

- 将

参数对应成参数_i和参数_o,输入参数参数_i为ap_none,输出参数参数_o带有vaild指示,即输出数据是否有效的指示信号led_o_ap_vld。

代码效果

static int counter = 0;

void hlsv1(ap_int<1> * led) {

#pragma HLS INTERFACE ap_ovld port=led

#pragma HLS INTERFACE ap_ctrl_none port=return

counter= counter+ 1;

if (counter < MAX_COUNT) {

*led = *led;

} {

*led = 1;

}

}

⇓ \Downarrow ⇓

module hlsv1 (

ap_clk,

ap_rst,

led,

led_ap_vld

);

parameter ap_ST_fsm_state1 = 1'd1;

input ap_clk;

input ap_rst;

output [0:0] led;

output led_ap_vld;

ap_vld

- 具有关联有效信号的输入和输出数据。

代码效果

static int counter = 0;

void hlsv1(ap_int<1> * led) {

#pragma HLS INTERFACE ap_vld port=led

#pragma HLS INTERFACE ap_ctrl_none port=return

counter= counter+ 1;

if (counter < MAX_COUNT) {

*led = *led;

} {

*led = 1;

}

}

⇓ \Downarrow ⇓

module hlsv1 (

ap_clk,

ap_rst,

ap_start,

ap_done,

ap_idle,

ap_ready,

led_i,

led_o,

led_i_ap_vld,

led_o_ap_vld

);

parameter ap_ST_fsm_state1 = 3'd1;

parameter ap_ST_fsm_state2 = 3'd2;

parameter ap_ST_fsm_state3 = 3'd4;

input ap_clk;

input ap_rst;

input ap_start;

output ap_done;

output ap_idle;

output ap_ready;

input [0:0] led_i;

output [0:0] led_o;

input led_i_ap_vld;

output led_o_ap_vld;

ap_ack

- 此协议对输入和输出端口的行为不同。对于 inputs,添加了一个 output acknowledge port,添加输出应答ack信号。它用于表示当前模块已经处理并确认接收或输出了信号

代码效果

// LED控制函数

void hlsv1(ap_uint<1> led) {

#pragma HLS INTERFACE ap_ack port=led

#pragma HLS INTERFACE ap_ctrl_none port=return

}

⇓ \Downarrow ⇓

module hlsv1 (

ap_clk,

ap_rst,

led,

led_ap_ack

);

parameter ap_ST_fsm_state1 = 1'd1;

input ap_clk;

input ap_rst;

input [0:0] led;

output led_ap_ack; // 1位输出确认信号,ack 为 1表示接收到有效输入信号led

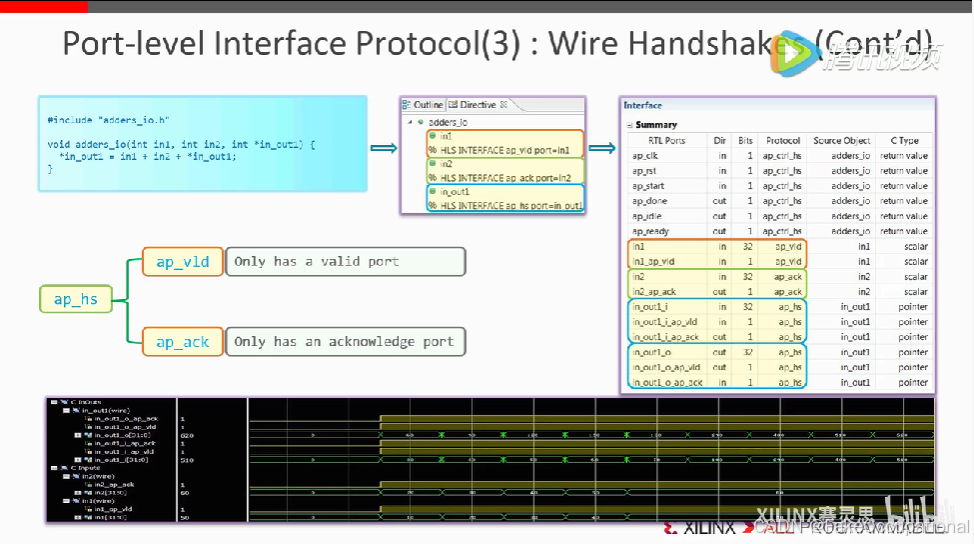

ap_hs

ap_hs包含ap_ack、ap_vld的组合功能。用于输入和输出端口,并促进数据生产者和消费者之间的双向握手过程。是一种传递数据的可靠方法,无需在外部确保 timing 。

代码效果

void hlsv(ap_uint<1> *led_o){

#pragma HLS INTERFACE ap_hs port=led_o

}

⇓ \Downarrow ⇓

module hlsv (

ap_clk,

ap_rst,

ap_start,

ap_done,

ap_idle,

ap_ready,

led_o_i,

led_o_o,

led_o_i_ap_vld,

led_o_i_ap_ack,

led_o_o_ap_vld,

led_o_o_ap_ack

);

parameter ap_ST_fsm_state1 = 5'd1;

parameter ap_ST_fsm_pp0_stage0 = 5'd2;

parameter ap_ST_fsm_pp0_stage1 = 5'd4;

parameter ap_ST_fsm_pp0_stage2 = 5'd8;

parameter ap_ST_fsm_state6 = 5'd16;

input ap_clk;

input ap_rst;

input ap_start;

output ap_done;

output ap_idle;

output ap_ready;

input [0:0] led_o_i;

output [0:0] led_o_o;

input led_o_i_ap_vld;

output led_o_i_ap_ack;

output led_o_o_ap_vld;

input led_o_o_ap_ack;

ap_fifo

- ap_fifo将参数对应的接口实现为FIFO缓存。

- 注意:参数应为指针类型。

代码效果

void hlsv1(ap_uint<1> *led) {

#pragma HLS INTERFACE ap_fifo port=led

#pragma HLS INTERFACE ap_ctrl_none port=return

}

⇓ \Downarrow ⇓

module hlsv1 (

ap_clk,

ap_rst,

led_dout,

led_empty_n,

led_read

);

parameter ap_ST_fsm_state1 = 1'd1;

input ap_clk;

input ap_rst;

input [511:0] led_dout;

input led_empty_n;

output led_read;

5469

5469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?