详细布局

详细放置将设计从初始全局放置带到完全放置的设计,通常从最大的结构(用作良好的锚)开始,一直到最小的。细节放置过程从放置大型宏开始,例如多列URAM、块RAM和DSP块阵列,然后是LUTRAM阵列宏,以及较小的宏,如用户定义的XDC宏。迭代逻辑布局以优化线路长度、时序和拥塞LUT-FF对被封装到具有额外约束的CLB中,这些约束在CLB必须共享公共控制集。

布局后优化

在分配完所有逻辑位置后,Post Placement Optimization执行最终改善时间安排和拥堵的步骤。其中包括改进关键路径布局复制,以及可选的BUFG插入阶段。在BUFG复制阶段,BUFG驱动跨越多个SLR的网络将为每个SLR接收它们自己的BUFG驱动程序。优化将在放置或布线冲突的情况下跳过,这些约束将阻止复制或定时降级。在BUFG插入阶段,放置器可以路由高扇出net,以释放结构路由资源。高扇形网(扇形>UltraScale和UltraScale+为1000,Versal为扇出>1000)驱动控制信号对于该优化考虑大于1.0ns的松弛。负载分为临界载荷和高正松弛载荷。高正松弛负载通过BUFGCE,放置在离原始驾驶员最近的可用场地,而关键负载仍然连接到原始驱动器。只有在没有时序退化。如果优化需要网表编辑,也会跳过优化失败。BUFG Insertion默认情况下处于启用状态,可以使用-no_BUFG_opt选项禁用。

建议:放置后运行report_timing_summary以检查关键路径。路径对于非常大的负设置松弛,可能需要逻辑重组、物理优化或布图规划以实现定时关闭。

地点设计

place_design命令在设计上运行放置。与其他实施方式一样命令,place_design本质上是可重入的。对于局部放置的设计,Vivadoplacer使用现有的放置作为起点,而不是从头开始。

place_design示例脚本将设计放入内存中。然后写一个设计完成放置后的检查点,生成时间摘要报告,并写入报告到指定的文件。

使用指令

指令为place_design命令提供了不同的行为模式。只有一个一次可以指定指令。指令选项与具有的其他选项不兼容-no_fanout_opt、-no_bufg_opt、-quiet和-verbose除外。使用-指导选项,探索您的设计的不同放置选项。

Placer指令

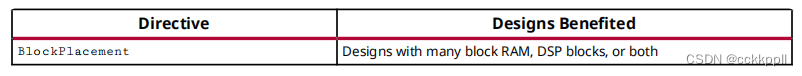

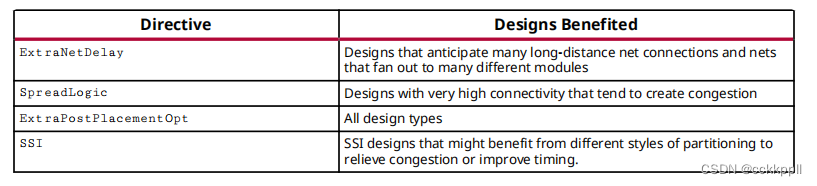

因为放置通常对整体设计性能影响最大,所以Placer具有所有命令中最多的指令。下表显示了哪些指令可能受益于哪种类型的设计。

可用指令

•探索:在细节布局和布局后优化方面投入更多精力。

•WLDrivenBlockPlacement:RAM和DSP块的线长驱动放置。以(权力)否决定时驱动的放置,通过指示放置器将连接到的距离最小化以及来自块。该指令可以改善RAM和DSP块之间的定时。

•EarlyBlockPlacement:RAM和DSP块的定时驱动放置。RAM和DSP块位置在放置过程的早期确定,并用作放置的锚点剩下的逻辑。

•ExtraNetDelay_high:增加高扇出和长距离网络的估计延迟。这指令可以改进关键路径的定时,这些路径在place_design之后满足定时但失败由于过于乐观的估计延迟,route_design中的定时。悲观情绪有两个层次支持:高和低。ExtraNetDelay_high应用了最高级别的悲观情绪。

•ExtraNetDelay_low:增加高扇出和长距离网络的估计延迟。这指令可以改进关键路径的定时,这些路径在place_design之后满足了定时,但是route_design中由于过于乐观的估计延迟而导致的故障定时。两个级别悲观情绪得到支持:高和低。ExtraNetDelay_low应用最低级别的悲观

•SSI_SpreadLogic_high:将逻辑分布在SSI设备中,以避免造成拥塞区域。支持两个级别:高和低。SpreadLogic_high达到最高级别传播。

•SSI_SpreadLogic_low:将逻辑分布在SSI设备中,以避免造成拥塞区域。支持两个级别:高和低。SpreadLogic_low实现了最低级别的传播。

•AltSpreadLogic_high:将逻辑扩展到整个设备,以避免造成拥塞区域。支持三个级别:高、中、低。AltSpreadLogic_high实现最高水平的传播。

•AltSpreadLogic_mediaum:将逻辑扩展到整个设备,以避免造成拥塞区域。支持三个级别:高、中、低。AltSpreadLogic_mediaum实现名义上的传播水平。

•AltSpreadLogic_low:将逻辑扩展到整个设备,以避免创建拥塞区域。支持三个级别:高、中、低。AltSpreadLogic_low实现最小传播水平。

•ExtraPostPlacementOpt:放置者在放置后优化方面付出的努力更大。

•ExtraTimingOpt:在后期阶段。

•SSI_SpreadSLLs:在SLR之间进行分区,并为更高的区域分配额外的区域连通性

•SSI_BalanceSLLs:在尝试平衡SLR之间的SLL时,在SLR之间进行分区。

•SSI_BalanceSLR:在SLR之间进行分区,以平衡SLR之间的单元数量。

•SSI_HighUtilSLR:强制放置程序尝试在每个SLR中更紧密地放置逻辑。

•运行时间优化:运行最少的迭代,用更高的设计性能换取更快的运行时间

•快速:绝对、最快的运行时间,非定时驱动,执行法律设计。

•默认:使用默认设置运行place_design。

•RQS:指示place_design选择report_qor_advancement指定的指令战略建议。要求在调用此指令。

自动指令

当结束具有挑战性的设计时,用户可能会选择运行许多不同的place_design指令,以便选择最佳计时结果。自动指令使用机器学习预测要运行的最佳指令。用户可以通过仅运行这些指令而受益而不是“可用指令”中列出的全部指令。

指令的机器学习预测有一定的误差。因此建议运行3个Auto_n指令并获得最佳结果。预测的指令是等效于“可用指令”中提到的指令,因此运行auto没有任何好处除此之外的指令。该工具选择的指令会在日志文件中报告。一消息示例如下:

要启用该功能,请设置place_design-directive<value>,其中value为:

•Auto_1:高性能预测指令

•Auto_2:第二好预测指令

•Auto_3:第三好预测指令

本文介绍了FPGA设计中的详细布局策略,从大到小的结构开始,逐步细化到LUTRAM和用户宏,同时强调了PostPlacementOptimization的优化步骤,包括关键路径优化、BUFG插入等,以及推荐在放置后进行关键路径检查。文章还讨论了place_design命令及其多种指令选项,如线长驱动、定时驱动放置等,以提升设计性能。

本文介绍了FPGA设计中的详细布局策略,从大到小的结构开始,逐步细化到LUTRAM和用户宏,同时强调了PostPlacementOptimization的优化步骤,包括关键路径优化、BUFG插入等,以及推荐在放置后进行关键路径检查。文章还讨论了place_design命令及其多种指令选项,如线长驱动、定时驱动放置等,以提升设计性能。

3418

3418

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?