平台:vivado21018.3,modelsim 10.6c

芯片:xc7k325tffg900-2 (active)

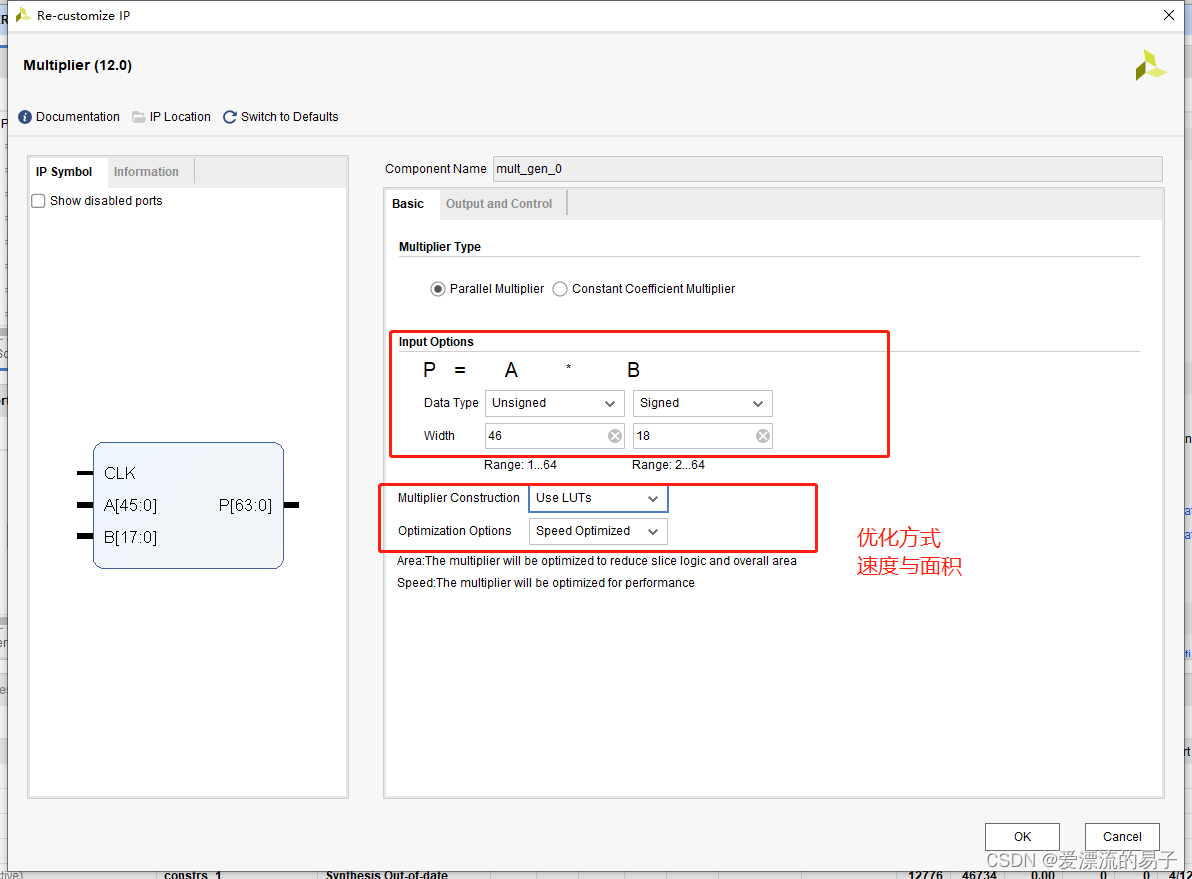

IP介绍乘法器,支持1到64位宽的输入和1到128位宽的输出。可以输入有符号和无符号数据。支持两种模式:

并行乘法器,用户自己输入A,B两个数据,乘法器输出计算结果。

常系数乘法器,用户输入一个数据,乘以用户定义的一个常数值。

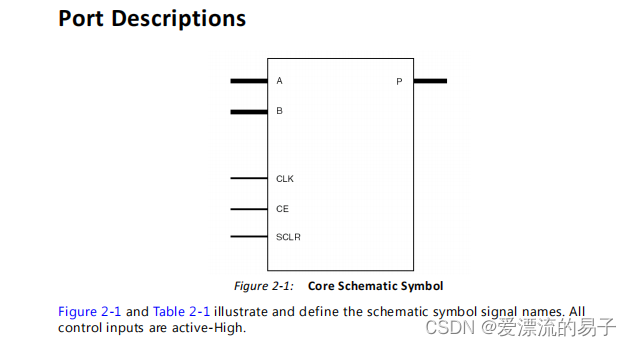

端口说明

| 信号 | 描述 | 详细 |

| A[N-1:0] | Input | 输入A |

| B[N-1:0] | Input | 输入B |

| CLK | Input | 时钟输入 |

| CE | Input | 时钟使能 高有效 |

| SCLR | Input | 同步清除 高有效 |

| P[X:Y] | Output | 计算结果 |

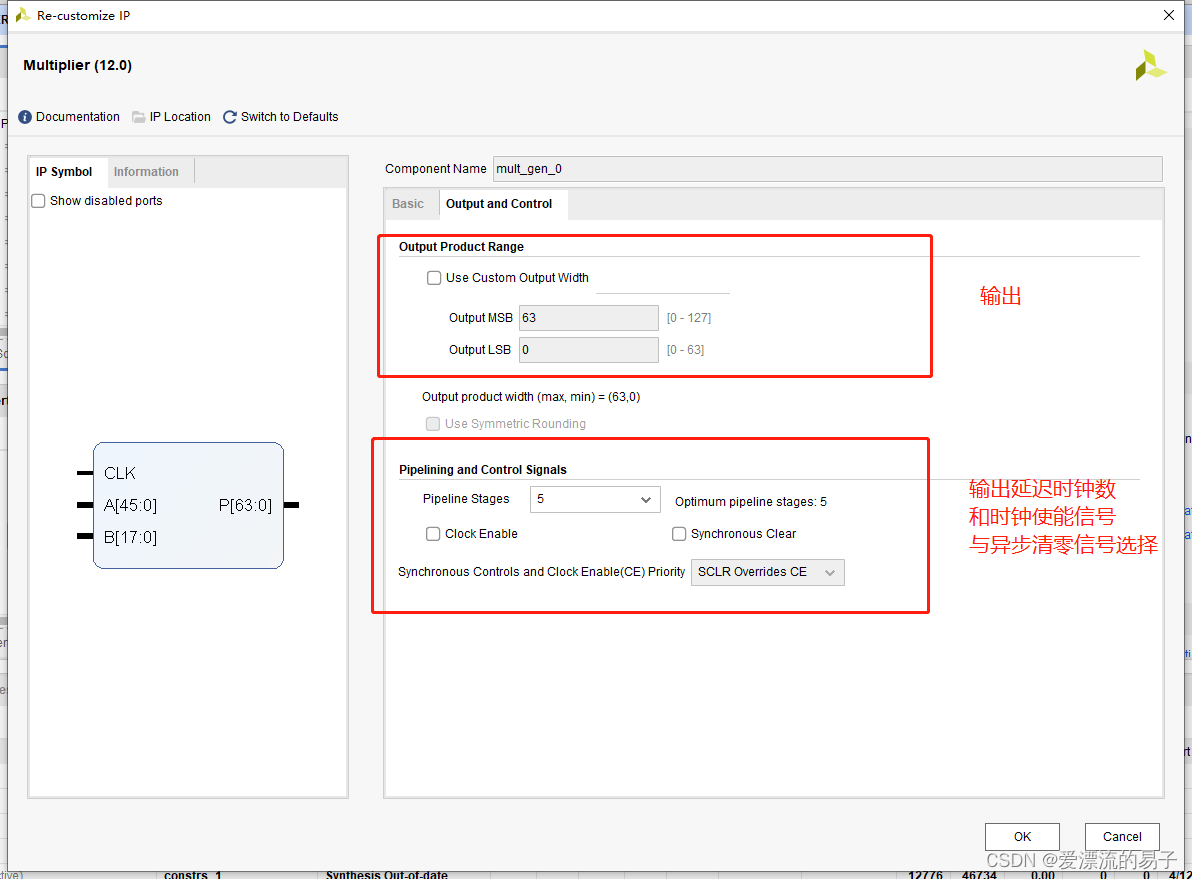

配置界面

配置界面如上图所示

配置界面如上图所示

速度优化使用乘法器原语来提高性能,面积优化使用mixture of slice和原语混合降低对DSP slice的使用。当两个输入操作数据都为无符号,且两个输入操作数都小于16位时,区域优化最有效。

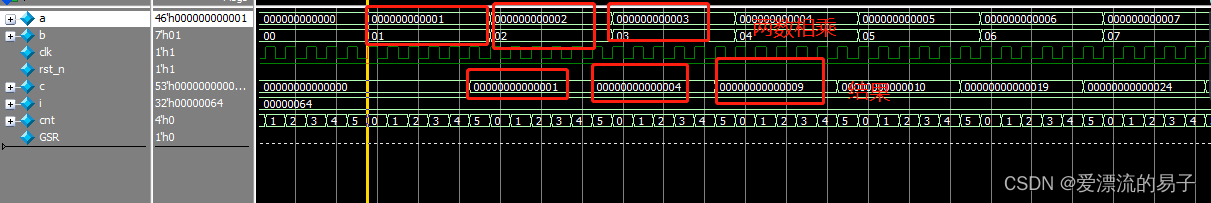

仿真tb,可以看到,在设置为延迟5个时钟周期后,计算结果保存在上。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/04/12 14:26:54

// Design Name:

// Module Name: mult_gen_0_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module mult_gen_0_tb;

reg [45:0] a;

reg [ 6:0] b;

reg clk;

reg rst_n;

wire [52:0] c;

mult_gen_0 u_mult_gen_0 (

.CLK (clk ),// input wire CLK

.A (a ),// input wire [45 : 0] A

.B (b ),// input wire [6 : 0] B

.P (c )// output wire [52 : 0] P

);

//------------------------------------------------------

//复位参数

//------------------------------------------------------

integer i;

//设置复位参数

initial

begin

$display("[%t] : reset begin...", $realtime);

rst_n = 0;

for( i=0 ; i<100 ; i=i+1)

begin

@(posedge clk );

end

$display("[%t] : reset stop...", $realtime);

rst_n = 1;

#100;

$finish;

end

initial

begin

clk = 0;

rst_n = 0;

end

reg [3:0] cnt ;

always@(posedge clk )

begin

if(rst_n == 1'b0)

begin

cnt <= 4'h0;

end

else if(cnt == 4'h5)

cnt <= 4'h0;

else

cnt <= cnt + 4'h1;

end

always@(posedge clk )

begin

if(rst_n == 1'b0)

begin

a <= 46'h0;

b <= 7'h0;

end

else if(cnt == 4'h5)

begin

a <= a + 46'h1;

b <= b + 7'h1;

end

else

begin

a <= a;

b <= b;

end

end

always#5 clk = ~clk;

endmodule

3316

3316

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?