与 PCB 传输线相关的损耗构成了高速仿真/设计和信号完整性领域的一个重要话题。传统上,数字设计不会受到与传输线效应相关的问题的影响。

较低频率

在较低频率下,信号保持在数据表征范围内,系统按设计运行。但随着系统速度的提高,对系统的高频影响意味着不仅要考虑数字属性,还要考虑系统内的模拟效应。一些最大的设计挑战围绕着 I/O 信号传输,其中传输线效应会对发送的数据产生重大影响。

较低的速度

在低速时,频率响应对信号的影响很小,除非传输介质特别长。然而,随着速度的提高,高频效应占据了上风,即使是最短的线路也可能出现振铃、串扰、反射和接地反弹等问题,严重阻碍信号的响应,从而破坏信号的完整性。实际上,这些问题可以通过良好的设计技术和遵循简单的布局指南来克服。

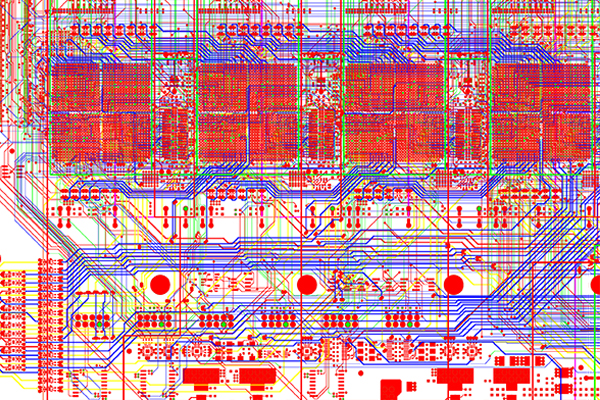

描述信号完整性的印刷电路板原理图

电路设计过程中的 PCB 考虑因素

以下是许多不同来源(如 Texas Instruments)发布的一些指南,这些指南涉及高速信号(如时钟信号及其路由),并为设计人员提供了重要一致性的回顾。因为很多事情都会影响传输线,所以可能会出现 EMI 问题。为了减少这些问题,良好的 PCB 设计很重要,通过一些简单的设计规则,PCB 设计人员可以最大限度地减少这些问题。

- 系统中最高频率和最快上升时间是多少?

- sink 和 source 的输入和输出的电气规格是什么?

- 是否有敏感的信号需要布线——例如,考虑控制阻抗、端接、走线上的传播延迟(时钟分配、总线等)?

- 微带线是否足以满足敏感信号,还是必须使用带状线技术?

- 存在多少种不同的电源电压?每个电源电压是否需要自己的电源平面,或者是否可以拆分它们?

- 使用系统的功能组创建图表 - 例如,发射器路径、接收器路径、模拟信号、数字信号等。

- 至少两个独立的官能团之间是否存在任何互连?请特别照顾他们。考虑返回电流和与其他走线的串扰。

- 与 PCB 制造商澄清走线的最小宽度、间隔和高度。两层之间的最小距离是多少?

- 最小钻孔和过孔的要求如何?

- 是否可以使用盲孔和埋孔?

走线、过孔和其他 PCB 元件

- 迹线中的直角会引起更多的辐射。在拐角区域,电容增加,特性阻抗发生变化。这种阻抗变化会导致反射。

- 避免在走线中出现直角弯曲,并尝试至少使用两个 45° 角对其进行布线。为了最大限度地减少任何阻抗变化,最佳布线是圆形弯曲。

- 将高速信号(例如时钟信号)与低速信号分开,将数字信号与模拟信号分开;同样,位置很重要。

- 为了最大限度地减少一层上两个信号之间的串扰,以及相邻层之间的串扰,请将它们彼此成 90° 布线。

- 在大多数 routings中,使用 via 是必不可少的。但是设计师在使用它们时必须小心。它们增加了额外的电感和电容,并且由于特性阻抗的变化而发生反射。过孔也会增加走线长度。

- 避免差分走线中的过孔。

印刷电路板结构

所需的印刷电路板结构(构建)取决于设计中使用的元件封装、所需的信号走线密度和阻抗匹配要求。对于高速板,必须使用具有埋地和电源平面的多层 PCB。实心铜层允许设计人员保持器件接地和电源连接较短。此外,接地层为高速信号提供低电感返回路径。

PCB 层压板选择

如今,FR-4 PCB 层压板材料已广泛应用于电子行业。FR-4 材料是大多数数字设计的经济解决方案,只要板载频率可以保持在 2.5-3 GHz 范围以下即可。在高速下,数字信号可能会受到其移动的印刷电路板层压板参数的影响。

专用高速层压板(如 Rogers RO4350)在高频下比 FR 4 具有更好的性能。与使用 FR-4 材料相比,使用正确的材料可以帮助设计师更容易、更可靠地实现其设计目标。使用非 FR-4 材料时,最大的权衡是层压板的成本差异很大。

首先,通过印刷电路板传播的信号的速度取决于印刷电路板的介电常数。例如,当信号频率超过 5 GHz 时,FR-4 的典型介电常数(约 4.7)下降到接近 4。然而,罗杰斯 RO4350 材料的相对介电常数在 0 到 15 GHz 范围内是恒定的(大约 3.5)。如果印刷电路板的介电常数随频率变化,则信号的不同频率分量将具有不同的速度。这意味着,这些组件将在不同的时间达到负载。因此,这将导致数字信号失真。

其次,印刷电路板材料引起的信号损失随着频率的增加而增加。同样,数字信号的每个谐波将根据该操作频率进行衰减。信号分量损耗的增加将增加数字信号的失真。

印刷电路板布局通常是影响电子系统电磁兼容性的最重要因素。根据“设计规则”列表自动布线或布局的电路板通常不会在第一次通过时满足电磁兼容性要求;使用这些板的产品更可能需要昂贵的修复,例如电缆和屏蔽外壳上的铁氧体。花时间确保组件放置正确,走线布线最佳,通常可以使产品按时、按预算满足所有电磁兼容性和信号完整性要求。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?