刚刚开始学习Zynq 7000的时候,看到别人问ILA的问题时,说是集成逻辑分析仪,我觉得这是一个好东西,我一定要学会它。

我是买了黑金的AX7010, 后来换成AC7010,开始学习Zynq 7000的,当然他的平台是Vivado 2015.4 。我一步步按照黑金的教程学习,基本掌握了Zynq 7000的开发过程,但教程只是简单提到了仿真和逻辑分析仪。所以我不断寻找Vivado 下如何仿真以及逻辑分析仪的使用。一直不得要领,出不来。我好希望有一个教人走一遍的入门教程。经过十多天的苦苦思考和资料寻找,测试,前几天,测试出来了Vivado 下的仿真,我就积极地和大家分享了,见我的仿真入门一文。今天我又把集成逻辑分析仪的波形调出来了,我又把他分享给大家。新鲜出炉,有些理解不一定都好,但还是足以带你走一遍。

本文主要参考了xilinx 的ug908-vivado-programming-debugging.pdf,还有http://blog.chinaaet.com/kevinc/p/5100050249 (Vivado中使用逻辑分析仪ILA)。

此文还有2个续集,针对不同的情况:

Vivado的集成逻辑分析仪ILA 在有sdk 下的应用入门

源代码和工程下载地址: 链接:http://pan.baidu.com/s/1pL4yCR5 密码:ki9s

1: 建立工程并准备文件

打开Vivado, 并新建一个工程,取名dividerIla ,类型(type),选择RTL Projecct,Default Part 根据你的硬件平台选择。这个一定要选择正确,因为需要下载并运行的。我的平台是AC7010, 选择的是xc7z010clg400-1。

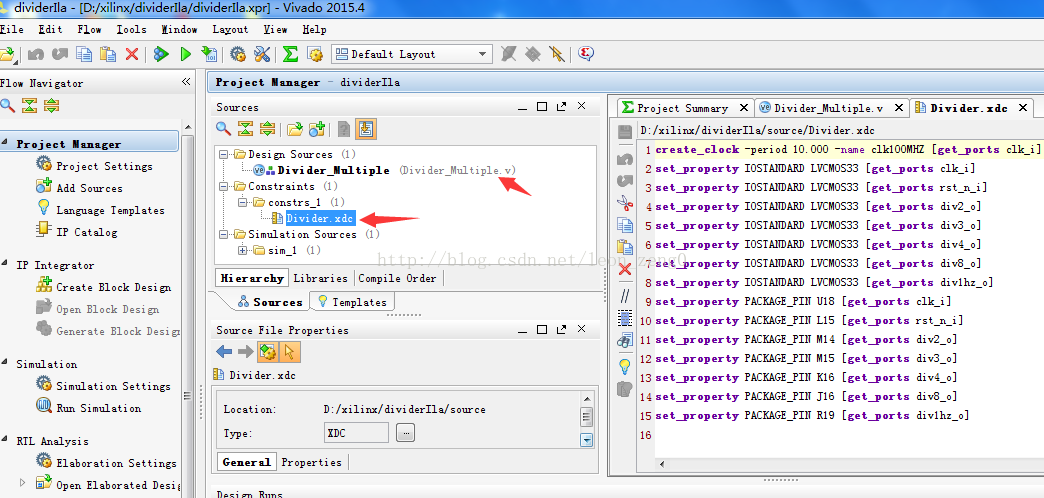

接下来是添加下载的源程序文件:Divider_Multiple.v 到Design Sources 下, Divider.xdc 到 Constarnts下。最后的效果如下图,其操作过程不详述,如果操作不来,请去查看我写的 Vivado 下的仿真入门一文,那有详细图示。

这里特别注意,如果你的硬件平台不一样,你需要修改Divider.xdc文件。这里分配硬件的管脚,需要与你的硬件一致,特别是clk_i, div1hz_o。 clk_i 是时钟输入脚,我的硬件是U18, div1hz_o 是led 闪灯控制,我的是R19, rst_n_i 是复位脚,我的是L15(其实没有使用)。

在这一步的时候,如果你综合(Synthesis), 执行(Implementation),产生比特流(Genrate Bitstream), 并下载 运行,应该看到你的一个LED 在一闪一闪的。这就是说,如果硬件平台不一致,你

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7003

7003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?