在SV中$monitor的使用格式与$display相同,语义上有所不同,$display是将双引号中的参数列表内容打印出来,而$monitor是在参数列表发生改变的时候,将参数列表内容打印出来。

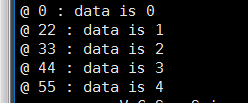

如果同时使用两个$monitor函数,那么会发生冲突

module Mon;

bit[7:0] addr;

bit[7:0] data;

initial begin

for(int i=0;i<5;i++) begin

#10ns;

addr = i;

data = i;

end

end

initial begin

$monitor("@ %0t : addr is %0h",$time,addr);

$monitor("@ %0t : data is %0h",$time,data);

end

endmodule输出如下:只输出第二个$monitor的结果

这样的话,需要改写成:

initial begin

$monitor("@ %0t :addr is %0h\udata is %0t",$time,addr,data);

end

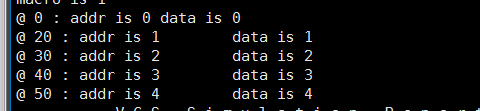

在使用$monitor进行打印的时候,要加上-timescale=1ns/1n的编译选项,否则打印有问题,如下所示,

只输出了最后一个值,并且方针时间也有问题。

![]()

本文介绍了SV中$monitor和$display的区别,强调$monitor在参数变化时才输出的特点。示例展示了当两个$monitor同时使用时,如何解决冲突,以及正确的使用格式。还提到了$monitor配合-timescale选项的重要性,否则可能造成输出错误。

本文介绍了SV中$monitor和$display的区别,强调$monitor在参数变化时才输出的特点。示例展示了当两个$monitor同时使用时,如何解决冲突,以及正确的使用格式。还提到了$monitor配合-timescale选项的重要性,否则可能造成输出错误。

3642

3642

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?