4 DDR5 SDRAM命令描述和操作-10

4.10 低功耗模式

DDR5的低功耗模式对于DDR系列来说是新的,因为它不再具有用于控制进入和退出的CKE引脚。相反,PDE/PDX的移动是基于命令触发的,由CS_n引脚触发。一旦进入低功耗模式,CS_n起到类似于历史上的CKE引脚的作用,等待其从高电平转变为低电平(伴随着命令)。在PDE模式下,应在每个边沿上进行采样。

4.10.1 低功耗模式的进入和退出

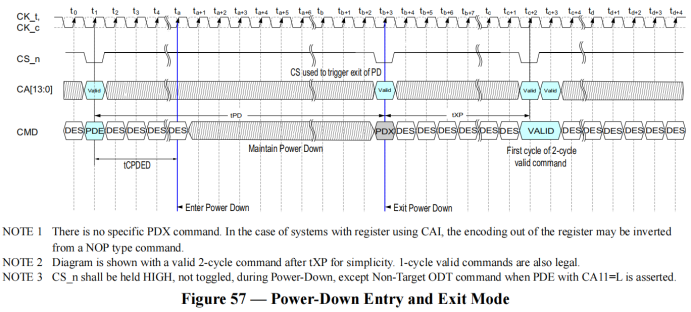

当命令被注册时,进入低功耗模式。与自刷新模式不同,在低功耗模式下,CS_n不会持续保持低电平。时序图在图57中显示了进入和退出低功耗模式的详细信息。

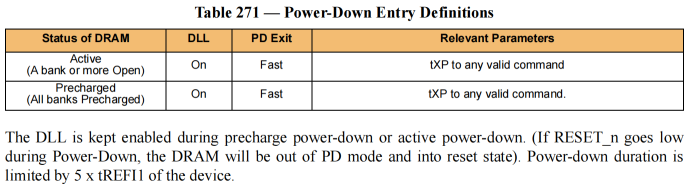

当进入低功耗模式时,DLL应处于锁定状态,以实现最快的断电退出时序。只要DRAM控制器符合SDRAM规格,SDRAM设计将提供所有AC和DC时序、电压规格以及正确的DLL操作。

在低功耗模式下,如果所有bank在进行中的命令完成后关闭,设备将处于预充电低功耗模式;如果在进行中的命令完成后仍有任何bank开启,设备将处于主动低功耗模式。

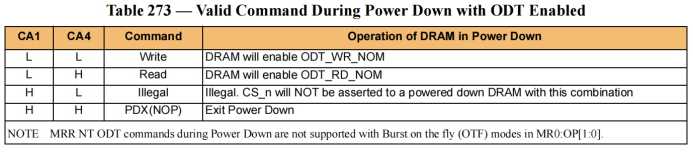

进入低功耗模式将关闭输入和输出缓冲器,但保留CK_t、CK_c、CS_n和RESET_n信号。如果在PDE命令期间CA11=L,则CA1和CA4也将被排除在外,从而允许适当的非目标SDRAM通过并解码NT ODT命令(即,SDRAM将监视利用CA1和CA4的NT ODT命令,并且如果注册了有效的NT ODT命令,将不会退出断电状态)。如果在PDE命令期间CA11=H,则只有经CS_n识别的PDX命令在低功耗模式下被认为是合法的。如果在PDE命令期间CA11=L,则只有经CS_n识别的NT ODT命令和PDX命令在低功耗模式下被认为是合法的。有关更多信息,请参考表241。

低功耗模式下的MRR NT ODT命令不支持在MR0:OP[1:0]中使用Burst on the fly (OTF)模式。

当启用ODT控制(CA11=L)的情况下进入低功耗模式时,DRAM将在整个断电过程中继续接受NT终止命令,包括进入和退出过程。在进入低功耗模式时,在tCPDED周期内,DRAM将从解码所有CA总线命令位切换到仅解码CA1和CA4。在此期间,在使用完整的RD或WR命令时,当CS_n被触发时,所有CA命令位必须有效,因为DRAM可能仍在解码完整的命令。在tCPDED完成后,只有CA1和CA4需要有效,因为DRAM将忽略其他命令位。在PDX命令之后,对于NT终止命令,所有CA命令位也必须有效,因为DRAM将过渡到解码所有命令位。仅在tCPDED完成和tXP之间的时间段中,CA13:5、3:2和0不需要有效。

注1:没有具体的PDX命令。在使用CAI的寄存器系统中,从寄存器中解码出来的编码可能与NOP类型命令相反。

注2:图中显示了在tXP之后的有效的2个周期的命令,为了简化起见,也可以使用1个周期的有效命令。

注3:在断电模式下,除非通过PDE和CA11=L来触发非目标ODT命令,否则CS_n应保持高电平而不切换。

在预充电断电或主动断电期间,DLL保持启用状态。(如果在断电期间RESET_n信号变低,则DRAM将退出断电模式并进入复位状态)。断电持续时间受设备的5倍tREFI1限制。

注1:在进行行激活、预充电、自动预充电或刷新等操作时,可以发送断电命令,但直到这些操作完成之前,IDD规范不会生效。

注2:tWR以纳秒为单位定义,为了计算tWRPDEN,需要将tWR/tCK向上取整。

注3:RD/WR/MRR以时钟周期为单位,根据MR6中的编程值确定。

注4:当在PDE命令期间CA11=H时,RD/WR/MRR可以指代目标命令和非目标命令。

注5:tMPD_delay是所有MPC命令的有效时序参数,但对于以下情况除外:

a)进入CS训练模式、进入CA训练模式、PDA枚举ID程序模式,因为这些MPC命令不支持断电模式。

b)应用VrefCA、VrefCS和RTT_CA/CS/CK,因为该MPC命令需要等待VrefCA_time/VREFCS_time。

1658

1658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?