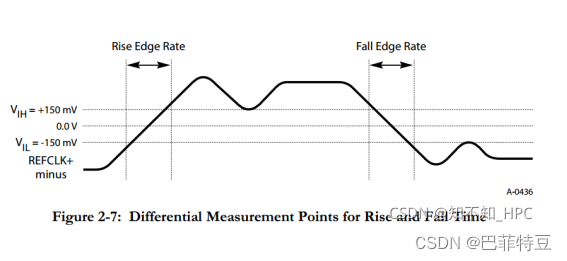

1、Rising Edge Rate & Falling Edge Rate

0.6V/ns ≤ t ≤ 4V/ns 。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:VIL = -150mV,VIH = +150mV,以差分波形交叉0点位置为中心的300mV窗口。介于测量区间-150mV ~ +150mV内的波形必须单调。

2、VIH & VIL

Differential Input High Voltage:VIH ≥ +150mV 。

Differential Input Low Voltage:VIL ≤ -150mV 。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:示波器cursor。

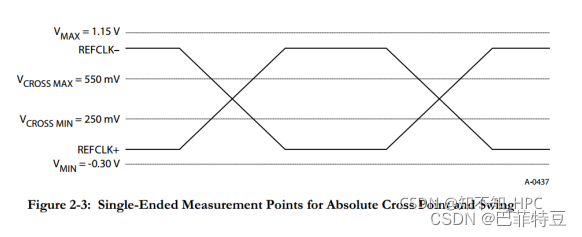

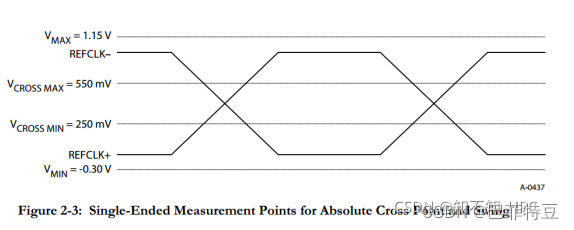

3、 VCROSS,Absolute crossing point voltage

+250mV ≤ VCROSS ≤ +550mV 。

1)测试对象:单端波形。

2)测试方法:REFCLK+上升沿与REFCLK-下降沿瞬时电压值相等的交叉点。

3)所有交叉点必须在+250mV ~ +550mV区间内。统计结果?

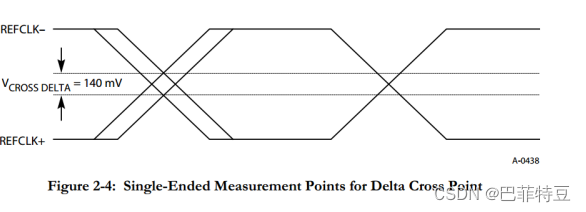

4、VCROSS DELTA,Variation of VCROSS over all rising clock edges

VCROSS DELTA ≤ +140mV 。

1)测试对象:单端波形。

2)测试方法:大量周期波形叠加,每个周期的REFCLK+上升沿与REFCLK-下降沿瞬时电压值相等的交叉点叠加后得出的统计区域。

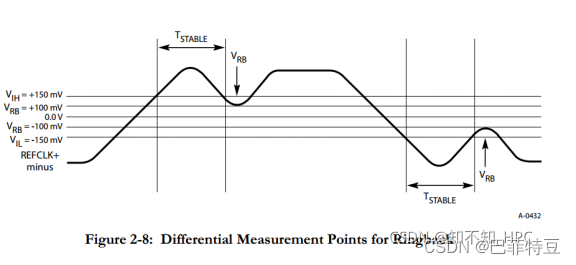

5、VRB & TSTABLE

VRB ,Ring-back Voltage Margin 。

TSTABLE ,Time before VRB is allowed 。

-100mV ≤ VRB ≤ +100mV 。

TSTABLE ≥ 500ps 。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:VRB :以0V位置为中心上下各100mV阈值,VRB 不得低于这个阈值限制;TSTABLE :上升沿或下降沿之后,波形必须保持在±150mV阈值外500ps以上。

6、TPERIOD AVG ,Average Clock Period Accuracy

-300ppm ≤ TPERIOD AVG ≤ +300ppm,非展频时钟。

-300ppm ≤ TPERIOD AVG ≤ +2800ppm,展频时钟。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:频率计。测试窗口设置为100ms或更大。

7、TPERIOD ABS ,Absolute Period (including Jitter and Spread Spectrum modulation)

9.847ns ≤ TPERIOD ABS ≤ 10.203ns 。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:绝对最小、最大瞬时周期,包含cycle to cycle jitter、相对PPM公差、展频调制。

8、TCCJITTER ,Cycle to Cycle jitter

TCCJITTER ≤ 150ps 。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:示波器,cycle to cycle jitter测试项。

9、VMAX & VMIN

VMAX ,Absolute Max input voltage 。

VMIN ,Absolute Min input voltage 。

VMAX ≤ +1.15V 。

VMIN ≥ -0.3V 。

1)测试对象:单端波形。

2)测试方法:波形的绝对最大、最小瞬时电压值,包含上冲(overshoot)和下冲(undershoot)在内。示波器统计测量一段时间内的VMAX & VMIN 。

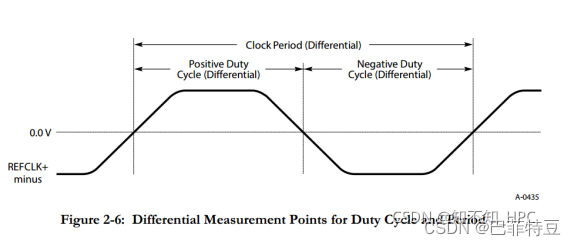

10、Duty Cycle

40% ≤ Duty Cycle ≤ 60% 。

1)测试对象:差分波形(REFCLK+减REFCLK-)。

2)测试方法:示波器统计测量一段时间内的Duty Cycle 。

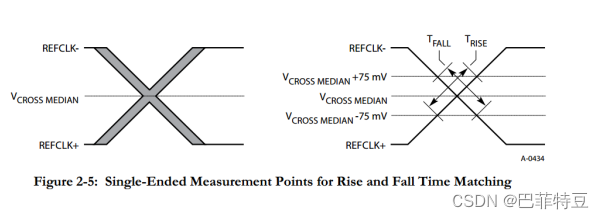

11、Rise-Fall Matching

Rise-Fall Matching,Rising edge rate (REFCLK+) to falling edge rate (REFCLK-) matching 。

Rise-Fall Matching ≤ 20% 。

1)测试对象:单端波形REFCLK+的上升沿、REFCLK-的下降沿。

2)测试方法:以REFCLK+和REFCLK-的中心交叉点为中心的±75mV的窗口内。在这个窗口内,REFCLK+的上升沿斜率与REFCLK-的下降斜率的差值最大不能超过两个斜率中较小斜率的20% 。

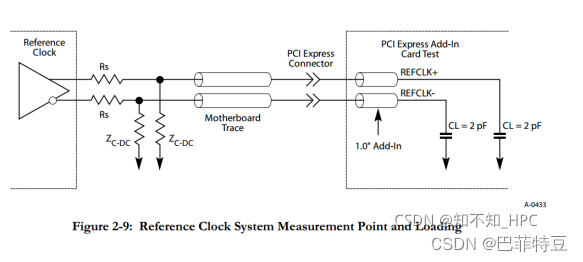

12、ZC-DC

ZC-DC ,Clock source DC impedance 。

40Ω≤ ZC-DC ≤ 60Ω 。

1)测试对象:单端波形。

2)测试方法:System board compliance measurements must use the test load card described in Figure 2-9. REFCLK+ and REFCLK- are to be measured at the load capacitors CL. Single ended probes must be used for measurements requiring single ended measurements. Either single ended probes with math or differential probe can be used for differential measurements. Test load CL = 2 pF.

414

414

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?