一、实现

1.下载安装Logsim 数字逻辑仿真软件。(从附件下载,先安装Java运行环境JDK,再运行Logsim)

2.在Logsim中设计一个1bit半加器电路,确保运算测试正确后,保存为子电路,文件名为half_adder.

3.在完成1bit半加器电路基础上,实现一个1bit全加器电路,保存为子电路,文件名为full_adder.

4.理解全加器和二进制补码的原理,用Logsim设计实现一个4位二进制数的补码器电路,要求:当输入一个4位二进制数后,补码电路将输出对应的4位二进制补码。

二、简单说明

1.补码原理

- 正数与原码相同;

- 负数的补码,将其原码除符号位外的所有位取反(0变1,1变0,符号位为1不变)后加1。 同一个数字在不同的补码表示形式中是不同的。比如10进制数值-15的二进制原码是10001111,其补码在8位二进制中是11110001,然而在16位二进制补码表示中,不足位数要用符号位补全,也就是1111111111110001。

2.步骤

因为正数和负数的补码运算规则不一样,取决与输入二进制数的最高位(符号位)。从简单入手,你可以先只考虑输入为负数情况的补码运算。

补码运算中有一个加1运算,需要用全加器实现。 4位全加器可以用4个1位(bit)全加器级联得到。

当你的负数补码器电路设计完成后,你可以在输入端口中输入任意一个4位的原码,仿真器会自动将原码转换成补码,并输出到输出端口中。例如,如果输入端口中输入了原码1010,输出端口中将会输出补码1110。

然后,你再继续考虑输入即有正数又可能是负数的情况下,如何完善补码器电路

三、四位全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

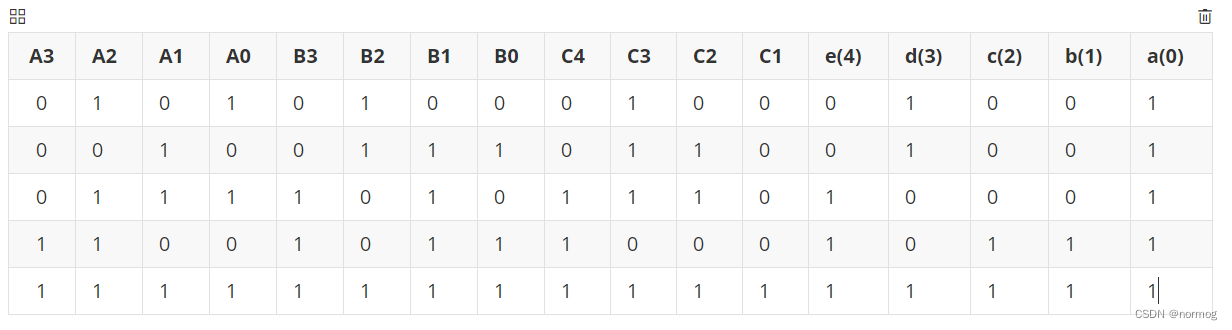

- 其真值表

- 四位全加器

6745

6745

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?