有时候,我们会发现一个问题,举个最简单的例子:比如将两个信号进行简单的异或运算。该逻辑运算,我们可以使用 assign 数据流建模完成,也可以使用always 组合逻辑过程赋值语句实现。那仿真工具在对它进行调度的时候,有什么区别吗?

不慌,今天,我们举个例子,来验证这一点。

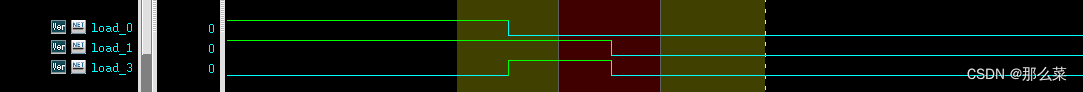

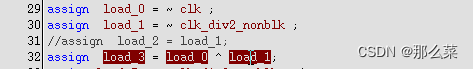

请看如下一段截取的断码片段,

分析:

load_3 : load_0 更新在active region, 而 load_2 更新在 NBA region, 那么 当执行语句

assign load_3 = load_0 ^ load_2 ;

load_3 发生在 Active region 和 NBA region。

而对于同样的该逻辑实现,如果是用always 关键实现,如下:

always @(*) begin

订阅专栏 解锁全文

订阅专栏 解锁全文

858

858

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?