HDL 人员开发利器-TerosHDL(开源 IDE)

https://terostechnology.github.io/terosHDLdoc/about/about.html

TerosHDL是啥

TerosHDL 的目标是为 HDL 开发人员提供一个开源 IDE,该 IDE 具有软件开发人员常用的功能。IDE 包含一堆工具,其中最重要的是VSCode 插件。一些工具是由Teros Technology组织开发的,而另一些则来自开源项目。所有工具都组织在不同的后端,并通过插件暴露给 GUI。

安装

安装 VSCode

https 😕/code.visualstudio.com/

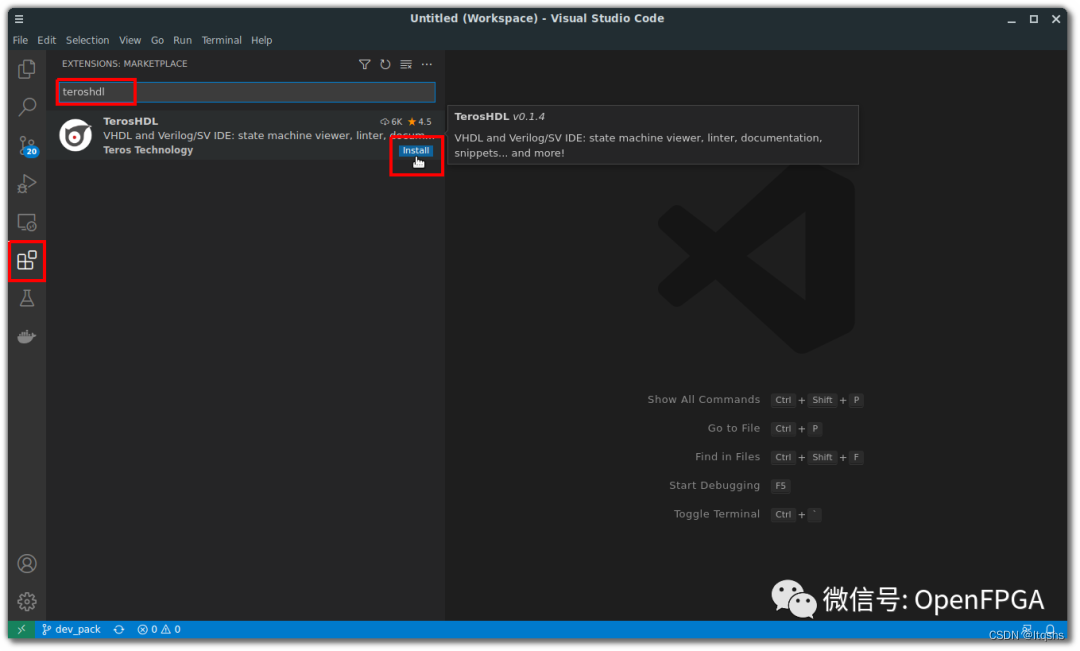

在扩展中搜索TerosHDLinside VSCode 并单击安装按钮:

安装其他:

python

安装过程略。

make

正常安装,不用修改,安装完毕后将下面路径(make的安装路径)加入到系统环境中。

C:\Program Files (x86)\GnuWin32\bin

安装系统下TerosHDL

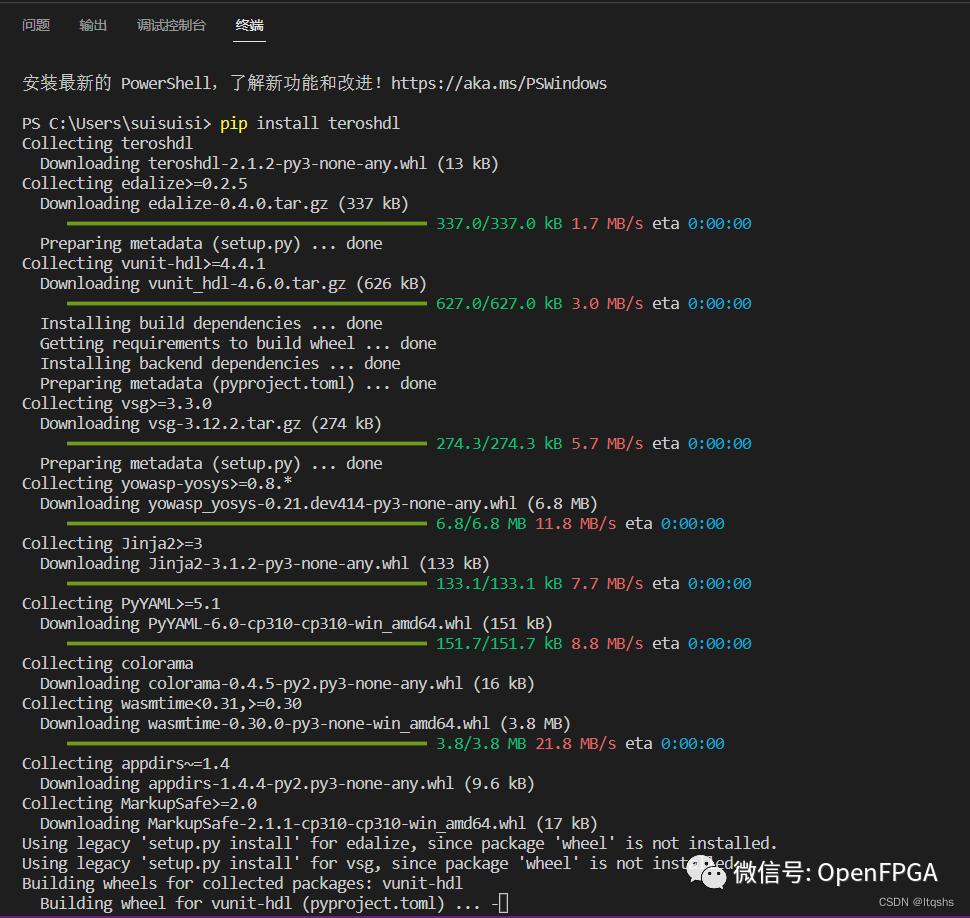

在vscode中点击左侧TerosHDL,在终端输入:

pip install teroshdl

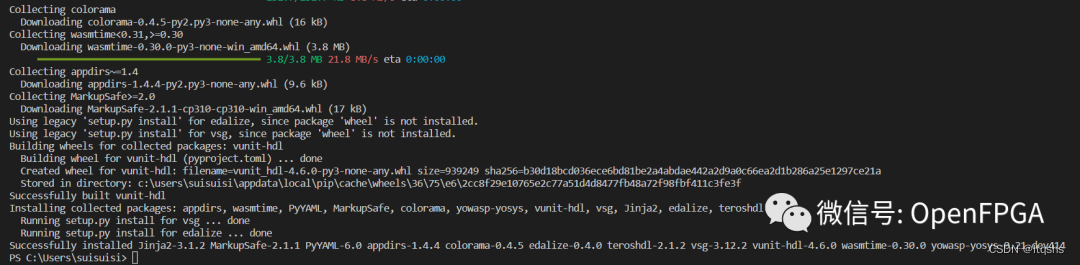

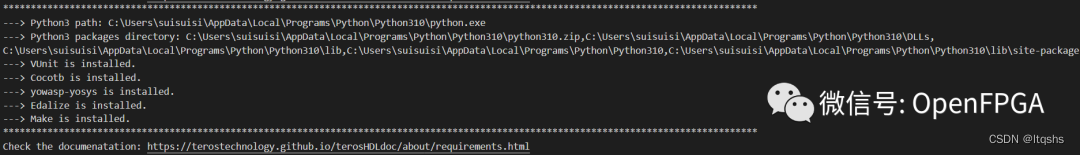

完成后如下:

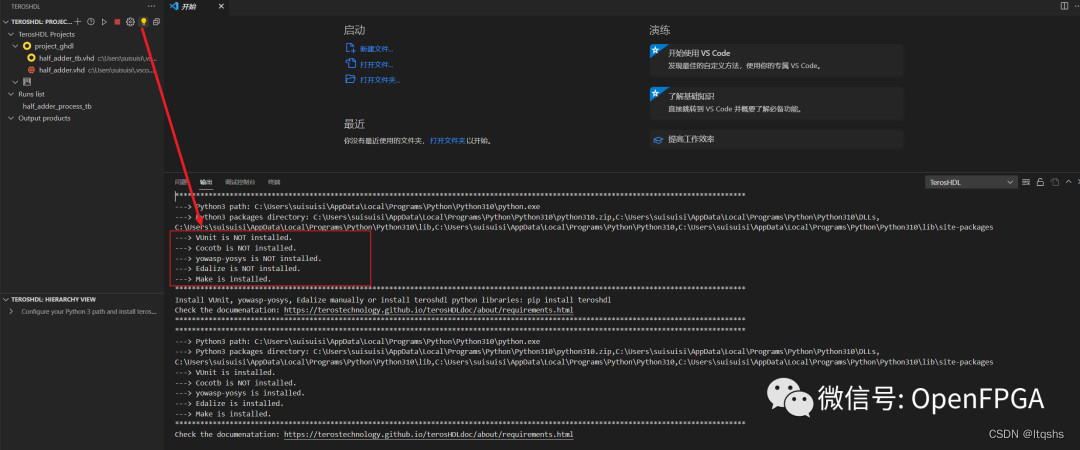

检查缺少的环境

按照下图检查一下TerosHDL还缺少什么环境,自己按照需求按照即可。

完成后如下:

实例演示

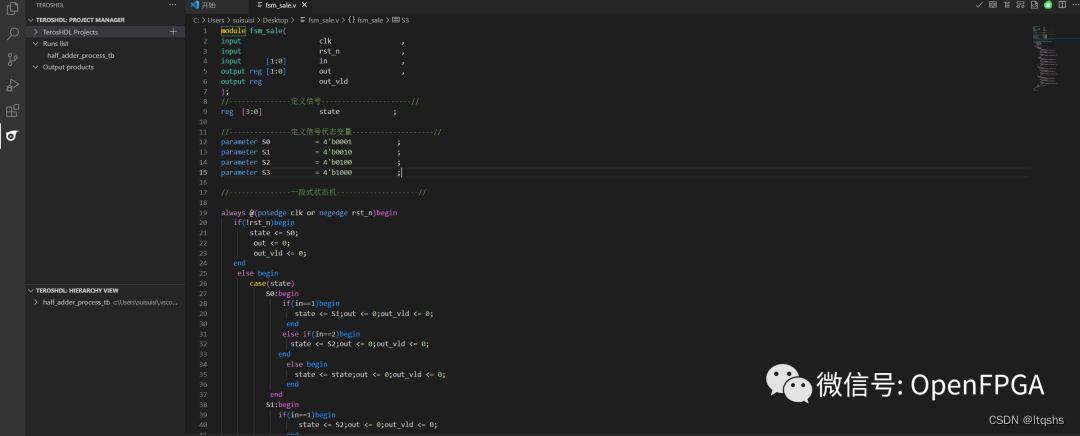

我们新建一个状态机的.v文件,具体如下:

module fsm_sale(

input clk ,

input rst_n ,

input [1:0] in ,

output reg [1:0] out ,

output reg out_vld

);

//---------------定义信号----------------------//

reg [3:0] state ;

//---------------定义信号状态变量--------------------//

parameter S0 = 4'b0001 ;

parameter S1 = 4'b0010 ;

parameter S2 = 4'b0100 ;

parameter S3 = 4'b1000 ;

//---------------一段式状态机--------------------//

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

state <= S0;

out <= 0;

out_vld <= 0;

end

else begin

case(state)

S0:begin

if(in==1)begin

state <= S1;out <= 0;out_vld <= 0;

end

else if(in==2)begin

state <= S2;out <= 0;out_vld <= 0;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

S1:begin

if(in==1)begin

state <= S2;out <= 0;out_vld <= 0;

end

else if(in==2)begin

state <= S3;out <= 0;out_vld <= 0;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

S2:begin

if(in==1)begin

state <= S3;out <= 0;out_vld <= 0;

end

else if(in==2)begin

state <= S0;out <= 0;out_vld <=1;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

S3:begin

if(in==1)begin

state <= S0;out <= 0;out_vld <=1;

end

else if(in==2)begin

state <= S0;out <= 1;out_vld <=1;

end

else begin

state <= state;out <= 0;out_vld <= 0;

end

end

default:state <= S0;

endcase

end

end

endmodule

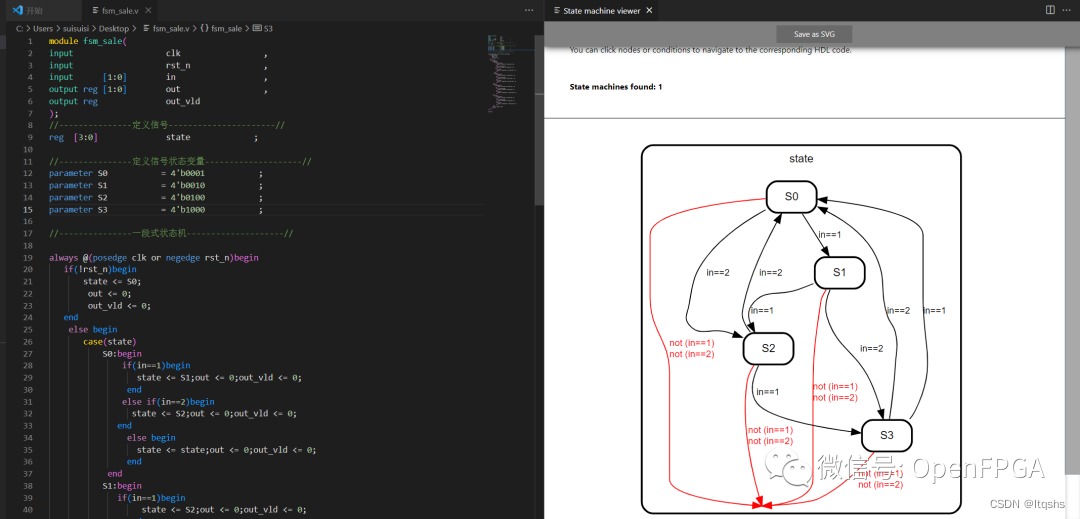

使用VSCode打开:

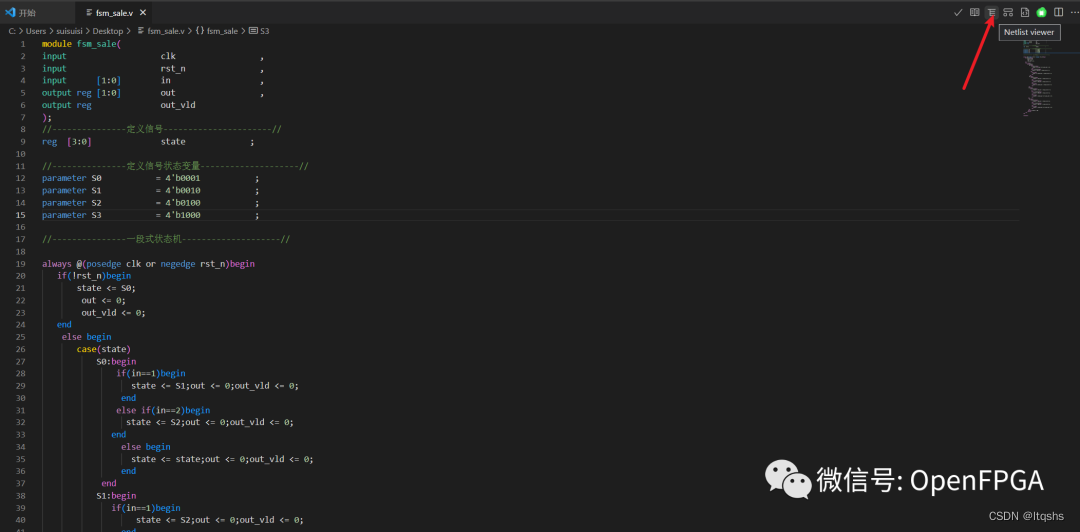

点击右上角的编译按钮,等待一会:

点击查看网表:

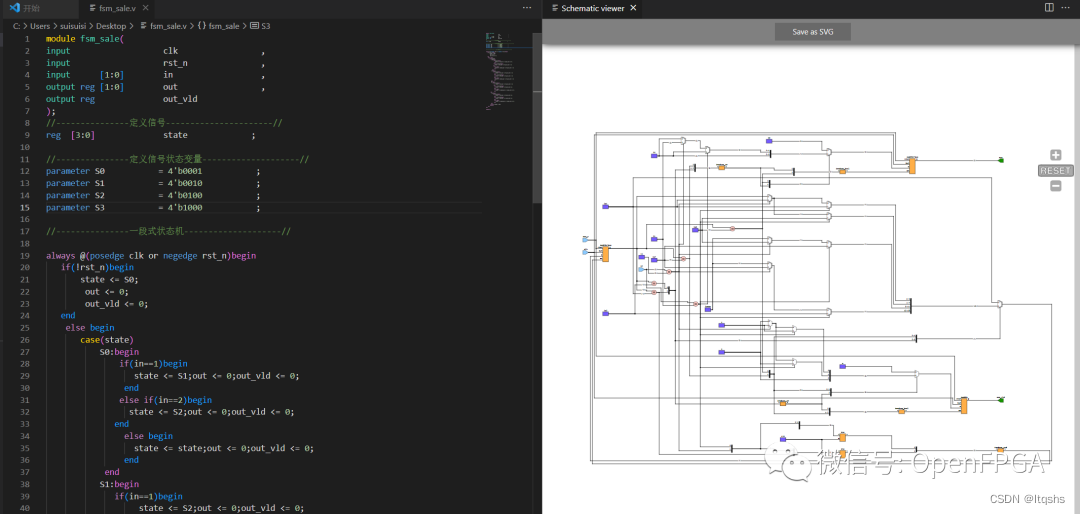

就能看到电路综合出来的网表:

点击旁边的查看状态机就能看到状态机流程图:

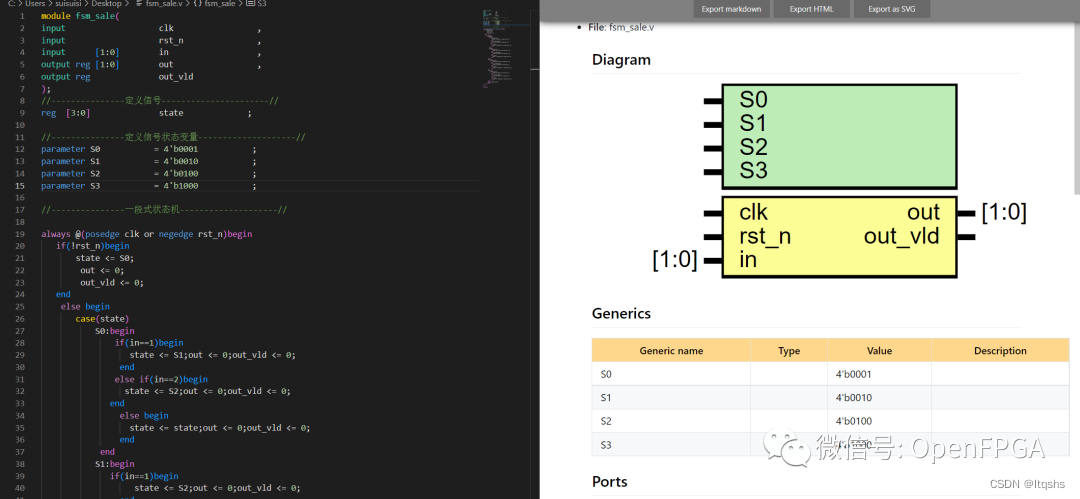

点击module文档说明,就能看到这个项目/文件自动生成的说明文档(极其中意的功能):

导出来的文档如下:

Entity: fsm_sale

File: fsm_sale.v

Diagram

Generics

Ports

Signals

Processes

unnamed: ( @(posedge clk or negedge rst_n) )

Type: always

State machines

总结

作为一个开源的IDE,功能比较完整,其中仿真部分没演示,大家可以自行探索,真的极其适合初学者,安装过程不复杂,都是常规的应用,下面给出来上面需要的安装文件。

https://github.com/suisuisi/teroshdl

其实我最中意的还是文档功能,对于维护HDL真的超级方便。

最后就是TerosHDL使用视频教程

336

336

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?