Quartus 联合 Modelsim

这里使用的版本是:

-

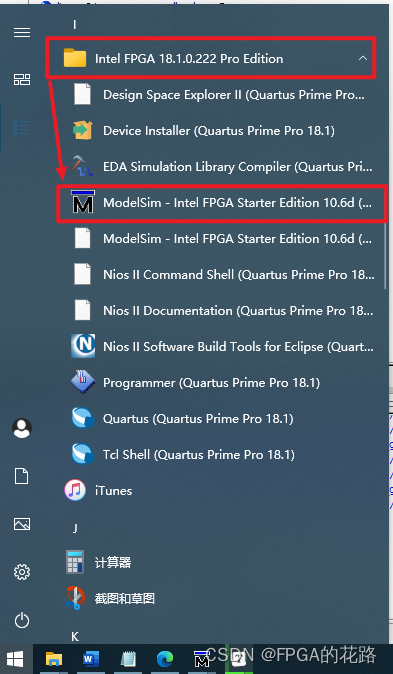

Quartus Prime 18.1.0.222 Pro Edition

-

Modelsim - INTEL FPGA STARTER EDITION 10.6d

由于直接使用quartus安装时自带的modelsim,所以不需要单独进行Altera库的安装,直接新建工程即可仿真

注:quartus pro版本与modelsim目前所知道最简单的仿真方法就是使用quartus安装时下载的modelsim进行独立仿真,操作步骤如下:

新建工程

- 在电脑上新建个文件夹,用来存放modelsim工程

- 从windows开始菜单里打开modelsim软件

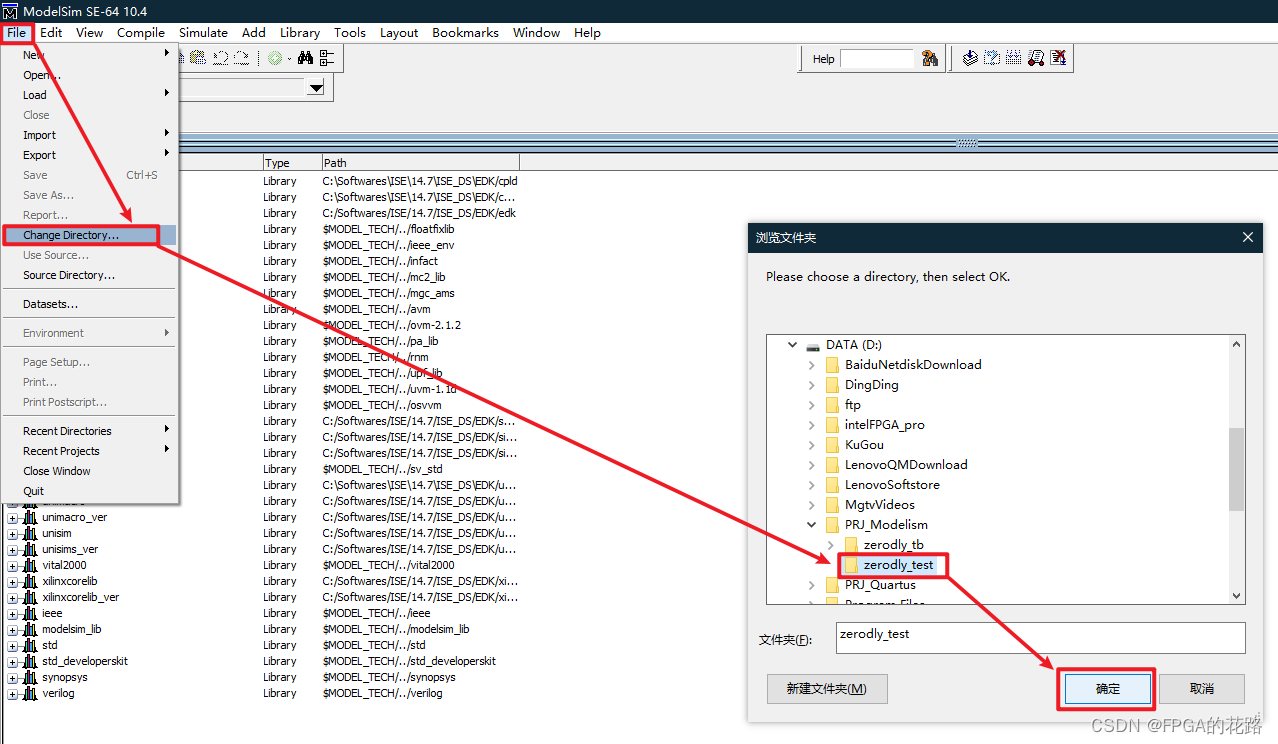

- 更改modelsim目录到新建的文件夹下

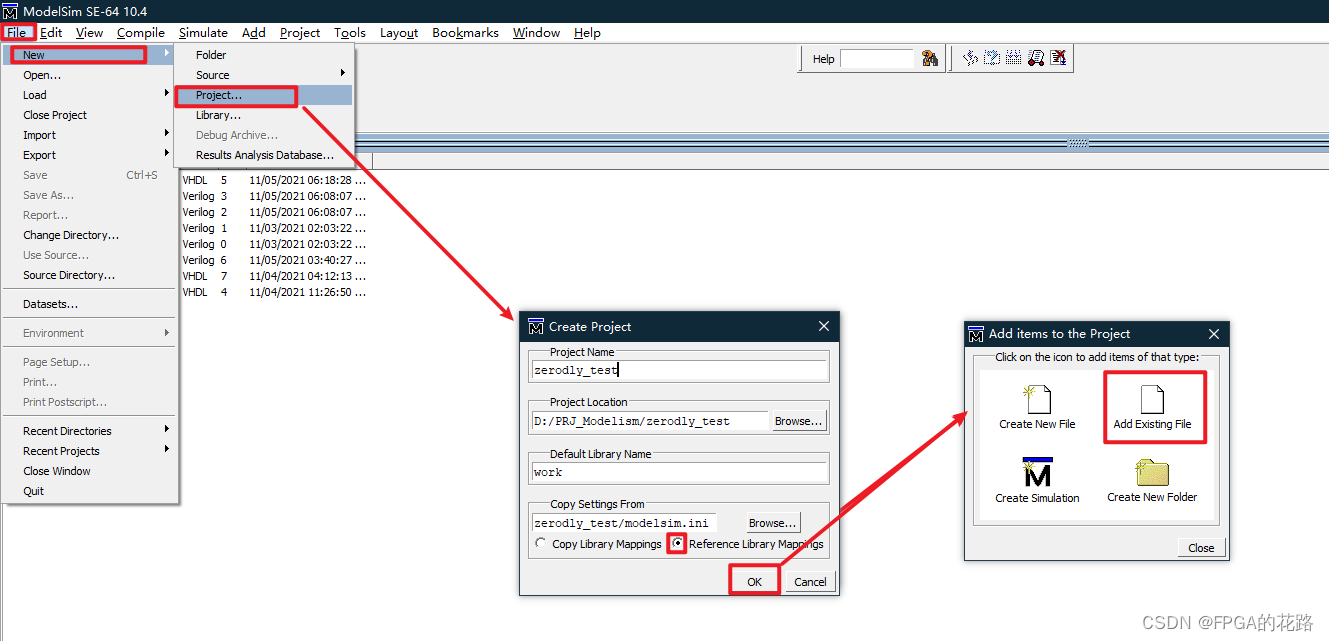

- 新建工程,点击 Add Existing File(添加所有要仿真的文件)

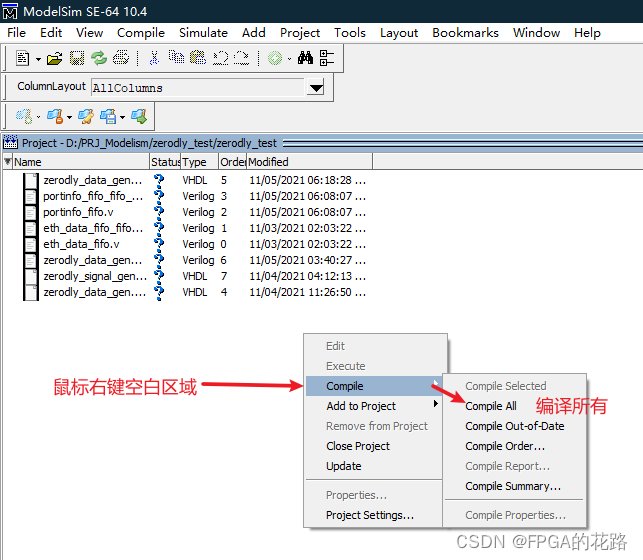

- 编译所有

- 然后在命令行窗口输入下面语句,其中将 work.zerodly_data_gen_tb 改为 work.+ 你要仿真的文件名

vsim -L work -L cyclone10gx_ver -L altera_ver -L lpm_ver -L sgate_ver -L altera_mf_ver -L altera_lnsim_ver -L twentynm_ver -L twentynm_hssi_ver -L twentynm_hip_ver -t ps -novopt work.top_scaler_tb -t ns

- 添加要观察的信号到波形窗口,命令行输入 view wave,命令行输入run 1 ns,即可观察波形

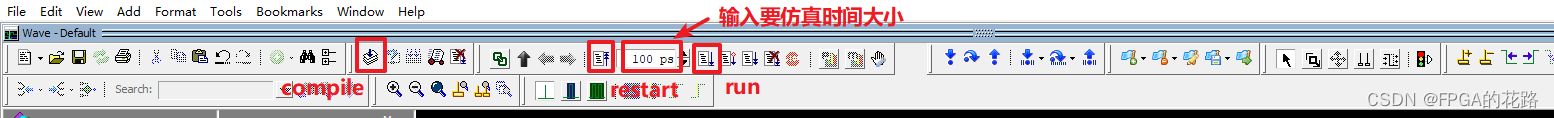

- 每次修改代码,直接compile更改的文件 -> restart -> run

- 可以保存波形窗口格式,下次仿真直接加载 .do文件,然后restart -> run即可,不用再重新添加信号

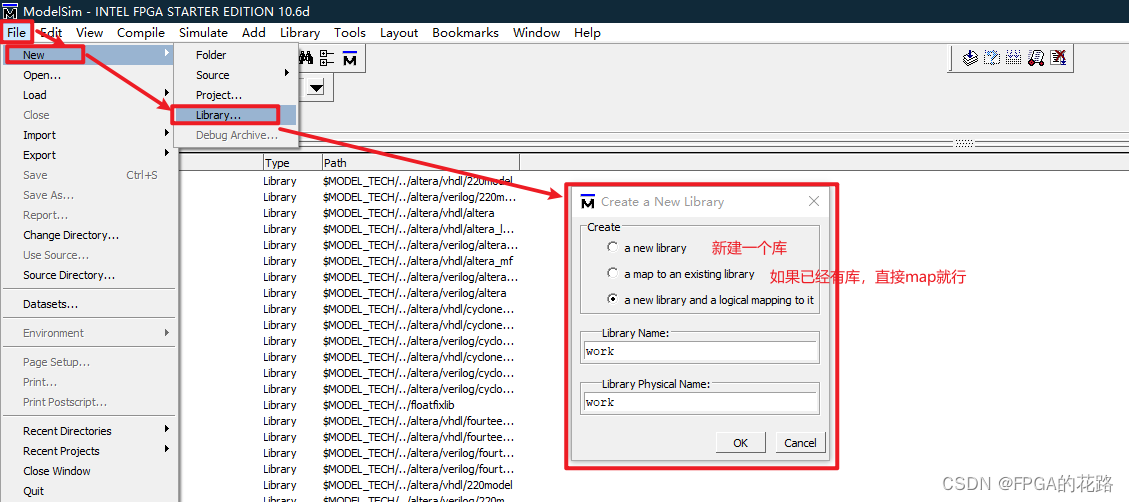

仿真已有工程

File -> Library -> a map to an existing library -> compile -> 命令行输入 view wave -> load do文件 -> run

Vivado 联合 Modelsim

这里使用的版本是:

- Vivado 2019.1

- Modelsim SE-64 2020.4

Modelsim 安装

- 复制MentorKG.exe,mgls64.dll以及patch64_dll.bat这三个文件到Modelsim安装目录的win64文件夹下,如E:\modeltech64_2020.4\win64

- 双击win64文件夹内粘贴过去的patch64_dll.bat文件,会生成LICENSE.TXT,另存到安装目录

- 设置系统环境变量,变量值为LICENSE.TXT的路径 变量名:LM_LICENSE_FILE 变量值:E:\modeltech64_2020.4\LICENSE.TXT

- 完成

联合 Vivado

-

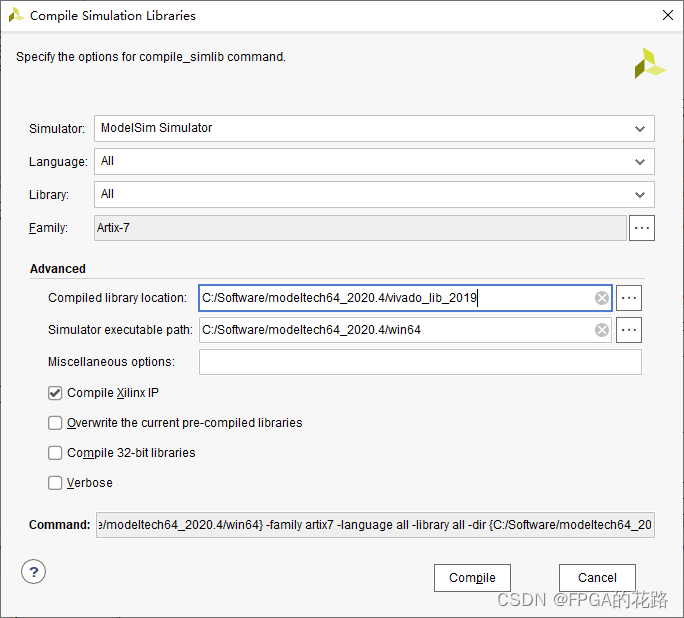

生成库文件

-

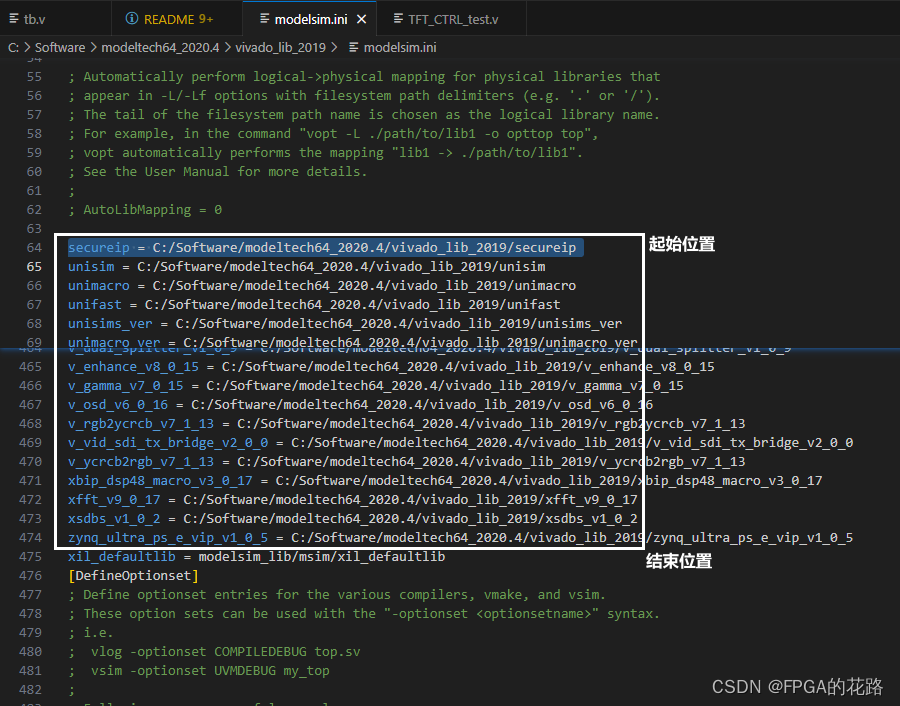

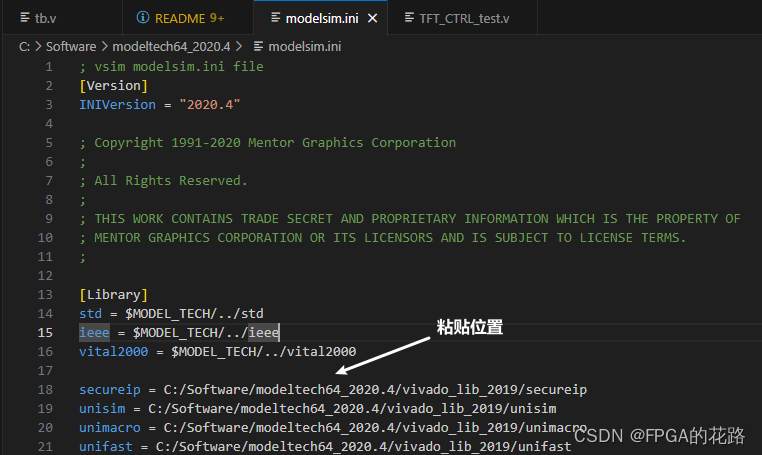

从库文件夹里的 modelsim.ini 文件中复制如下内容

-

将 modelsim 根目录下 modelsim.ini 文件属性只读关闭

-

粘贴刚刚复制的内容到该文件的如下位置,然后保存,勾选只读

-

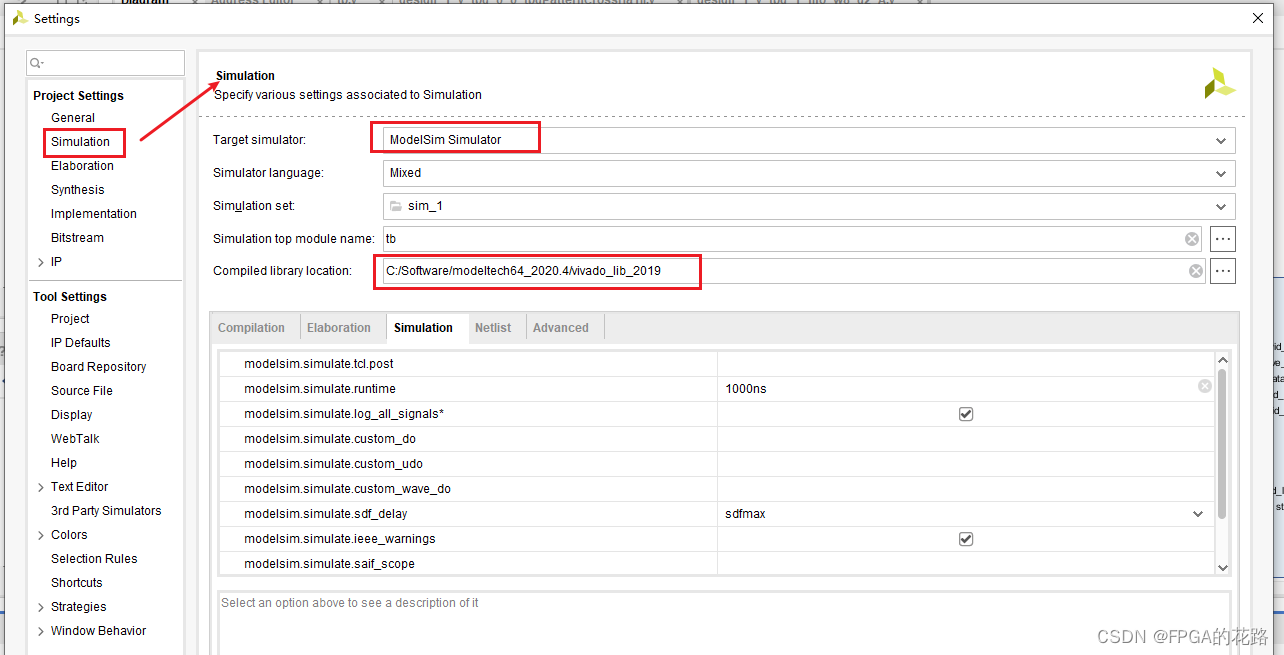

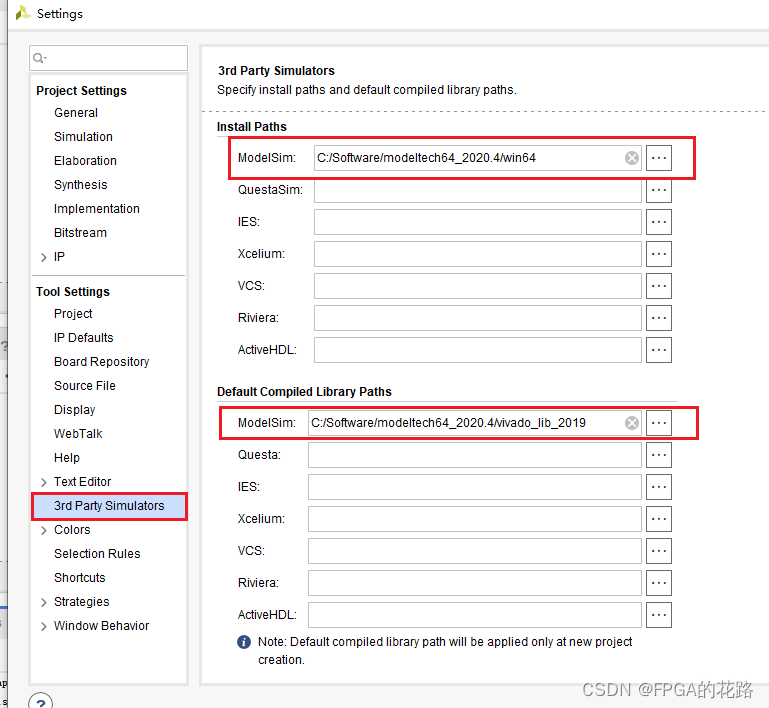

Vivado 设置

-

可以仿真了

Modelsim常见命令

#①退出当前仿真功能,退出当前的工程,跟在modelsim界面的命令行敲入命令的效果一样,之后就可以创建其他的工程

quit -sim

#②清除命令行显示信息

.main clear

#③创建库

vlib ./lib/

vlib ./lib/work_a/

vlib ./lib/design/

vlib ./lib/altera_lib/

#④映射逻辑库到物理目录

vmap base_space ./lib/work_a/

vmap design ./lib/design/

vmap altera_lib ./lib/altera_lib/

#⑤编译Verilog 源代码

vlog -work base_space ./tb_mealy.v

vlog -work design ./../design/*.vo

vlog -work altera_lib ./altera_lib/*.v

#⑥编译完后启动仿真

# -t 运行仿真的时间精度是ns

# -L 是链接库关键字

#......-t 时间单位,表示仿真的时间精度

#代码中-t ns:表示以ns为单位的精度进行仿真

#......首先是 -voptargs=+acc 后面的-L解释:

#由于创建了多个逻辑映射库,而启动仿真的时候的是需要链接库,因此 -L 逻辑映射库1 -L 逻辑映射库2... 就把映射库链接起来。

#映射完库之后,需要启动顶层的测试设计文件,而顶层测试设计文件是在某一个库中,因此是 顶层文件所在的逻辑.顶层文件了。

#后面的意思就是:链接 altera_lib base_space design这三个逻辑库,启动仿真顶层测量逻辑库base_space名字叫tb_mealy的文件

vsim -t ns -voptargs=+acc -L altera_lib -L base_space -L design base_space.tb_mealy

#信号显示成字符的方法

#......创建虚拟的结构体,用来产生虚拟信号。为什么要产生虚拟信号呢?因为在波形上面看111之类的,不知道状态的变化

#因此要在状态机中,可以添加虚拟先后,把4'b0001,显示成S1这里的,方便观看

#语法为:virtual type { {被替换16进制 用来显示的符号} {} {} ...} 结构体名字

#......创建完虚拟类型的结构体类型后,要进行转换显示的信号还需要两步:

#首先进行强制转换:例如 virtual function {(vir_new_signal)tb_mealy/mealy_inst/Curr_st} new_state

#就是 将要显示的 Curr_st信号 用一个类型为虚拟信号类型的 new_state 强制转换代替

#然后在添加波形显示就可以了如: #add wave -color red tb_mealy/mealy_inst/new_state

# -color red 是以什么颜色显示

virtual type {

{01 S1}

{02 S2}

{04 S3}

{08 S4}

{10 S5}

{20 S6}

} vir_new_signal

#⑦添加波形与分割线

add wave -divider {tb_mealy_1}

add wave tb_mealy/*

add wave -divider {mealy}

#顶层/例化的名字/* 其中*号是通配符,匹配所有信号

add wave tb_mealy/mealy_inst/*

#创建一个vir_new_signal 类型的信号,也就是把Currt_st进行类型转换

virtual function {(vir_new_signal)tb_mealy/mealy_inst/Curr_st} new_state

add wave -color red tb_mealy/mealy_inst/new_state

#⑧运行,格式是 run 运行时间

run 1us

vlib 创建 library,如创建名为 work的library的指令为,vlib work

vmap 通过修改modelsim.ini文件,在逻辑库名(如 work)与指定目录之间定义 一个映射。

vmap –del<logical_name> 删除名为 logical_name的映射;

vmap <logical_name>[<path>] 把逻辑库映射到指定的物理库上,若不定义 <path>,此命令返回现有映射。

vencrypt 用于 verilog加密,加密在预处理中进行,所以宏和`指令不做加密处 理,加密后的文件格式被修改为.vp/.svp。加密命令后面需要加上编译命令,如vlog。

vencrypt –d <dirname> 定义加密文件保存的地址;

vencrypt –f <filename> 调用文件,文件中定义多条指令,可以避免重复输入复杂 的指令集,-f可以嵌套调用。

vopt 编译后进行全局优化。

vlog 编译.v文件;

vlog –work <library name> 定义编译映射到的 library;

vlog +define+<macro_name>=<macro_text> 命令行中定义宏的方式,例如 `define one r1可以写为 vlog +define+one=r1;如果定义多个宏,在后面继 续加+<macro_name>=<macro_text>即可;

vlog –L <libname> 搜索指定的资源库提供给预编译模块;也可用在 vsim中;

vlog –v <library_file> 指定一个库文件包含模块和用户数据包协议的定义。在 vlog编译后,编译器用-v来找到并编译引用过但未定义的模块。

vsim 调用 VSIM仿真器。

vsim –l <filename> 将脚本窗口内容保存在指定文件中;

vsim –keepstdout 让仿真器不重复直接访问 stdout stream;

vsim –t 定义仿真时间分辨率;

vsim –novopt 禁止自动运行 vopt;

vsim –voptargs=+acc 规定当自动运行 vopt时,vsim应当跳转至 vopt;其中 +acc最常用,意思是使能 PLI并调试与指定对象相关的指令。

setenv <varname>[<value>] 改变或报告环境变量的现有值,仅用于现有 modelsim模块;

virtual type 在图形界面中将信号值显示为字符串,最高支持64位整形数据。

virtual type –delete<name> 删除之前定义的 virtual type;

virtual type {<list_of_strings>} 添加字符串显示;

virtual function 在图形界面中建立新的信号。方便将需要的信号放在一个波形窗 口查看。

add wave 添加波形。

add wave -divider <divider_name> 在波形列表中添加分类名。

add wave –radix <type> 定义显示进制形式,有 binary, ascii, decimal, octal, hex, symbolic, time, and default。

本文详细介绍了如何使用QuartusPrime18.1.0.222ProEdition与IntelFPGAStarterEdition的Modelsim进行新工程和已有工程的仿真,以及Vivado2019.1与ModelsimSE-64的联合安装和仿真设置。

本文详细介绍了如何使用QuartusPrime18.1.0.222ProEdition与IntelFPGAStarterEdition的Modelsim进行新工程和已有工程的仿真,以及Vivado2019.1与ModelsimSE-64的联合安装和仿真设置。

421

421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?