在大规模的集成电路中,低功耗的设计尤为重要,在谈低功耗设计之前我们必须弄明白芯片的功耗有哪些。

1、动态功耗

SoC的功耗可以分为动态功耗以及静态功耗。所谓动态态功耗即,器件处于开态是所消耗的功耗,一般发生在信号跳变时。静态功耗为器件接通电源,但是没有发生信号跳变时的功耗。在CMOS电路中,静态功耗一般为漏电流导致的。

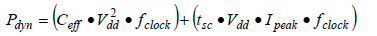

动态功耗主要有:1)信号跳变时对负载电容进行充放电产生的功耗;2)电路内部的电容充电,以及在信号转换过程NMOS与PMOS同时打开时产生的功耗。用公式可以表示为:

降低动态功耗的方法主要有:

1)多电源技术(Multi-Voltage);

2)门控时钟技术(Clock Gating);

3)门级功耗优化。

2、静态功耗

静态功耗主要由漏电流产生,MOS器件的漏电流主要有衬底漏电流(ISUB),栅极漏源(Ig),栅极导致的漏源漏电流(Igd),pn节反偏漏电流(Ires)。

对于减小漏电流产生的静态功耗主要有以下的方法:

1)多阈值电压技术(Multi-VT):在满足性能需求时,尽量使用高阈值电压;

2)门控电压(power gating):在模块不工作时,将模块关闭;

3)可变阈值电压技术(Variable Threshold CMOS (VTCMOS)),采用背栅工艺,调节器件的阈值电压,以达到减小漏电流的目的;

4)self reverse bias(Stack Effect)

5)使用长沟道器件。

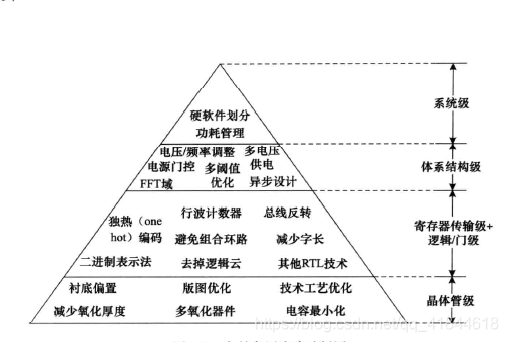

3、不同抽象层次降低功耗方法

如图所示在不同的抽象层次上,可以采用不同的方法降低功耗,并且抽象层次越高,功耗降低越为显著。

2191

2191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?