随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的?

事实上,Vivado 集成设计环境提供了很多辅助工具来协助用户完成时序约束的分析。

本文阐述了如何结合 Timing Constraints 窗口对设计中的约束进行查看及分析,希望为用户的设计调试提供一些思路和方向。

Timing Constraints 窗口的开启

Timing Constraints窗口仅对Synthesized Design或Implemented Design适用。您可以通过以下三种方式之一找到其入口:

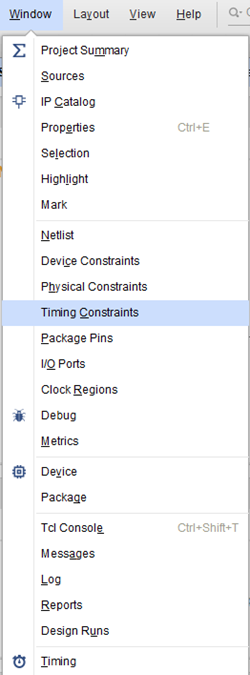

1. Open Synthesized/Implemented Design,选择菜单Windows > Timing Constraints

2. Open Synthesized Design,选择Flow Navigator里Synthesized Design 部分的 Edit Timing Constraints

开发者分享|读懂用好 Vivado Timing Constraints 窗口

最新推荐文章于 2024-04-09 07:43:21 发布

订阅专栏 解锁全文

订阅专栏 解锁全文

1665

1665

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?