含有无关项的序列检测

题目描述

请编写一个序列检测模块,检测输入信号a是否满足011XXX110序列(长度为9位数据,前三位是011,后三位是110,中间三位不做要求),当信号满足该序列,给出指示信号match。

程序的接口信号图如下:

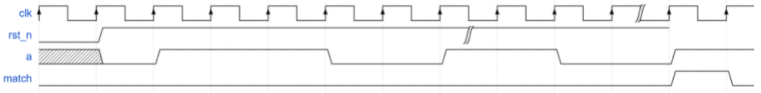

程序的功能时序图如下:

`timescale 1ns/1ns

module sequence_detect(

input clk,

input rst_n,

input a,

output reg match

);

parameter idle = 8'b00000001;

parameter state1 = 8'b00000010;

parameter state2 = 8'b00000100;

parameter state3 = 8'b00001000;

parameter state4 = 8'b00010000;

parameter state5 = 8'b00100000;

parameter state6 = 8'b01000000;

parameter state7 = 8'b10000000;

reg [0:7] c_state,n_state;

reg [0:1] cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

c_state <= idle;

else

c_state <= n_state;

end

always@(*)

begin

case(c_state)

idle:begin

if(a == 0)

n_state = state1;

else

n_state = idle;

end

state1:begin

if(a == 1)

n_state = state2;

else

n_state = state1;

end

state2:begin

if(a == 1)

n_state = state3;

else

n_state = state1;

end

state3:begin

if(cnt == 2)

n_state = state4;

else

n_state = state3;

end

state4:begin

if(a == 1)

n_state = state5;

else

n_state = state1;

end

state5:begin

if(a == 1)

n_state = state6;

else

n_state = state1;

end

state6:begin

if(a == 0)

n_state = state7;

else

n_state = idle;

end

state7:begin

if(a == 1)

n_state = idle;

else

n_state = state1;

end

default:n_state = idle;

endcase

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

cnt <= 2'b0;

else if(c_state == state3 && cnt == 2'd3)

cnt <= 2'b0;

else if(c_state == state3)

cnt <= cnt + 1'b1;

else

cnt <= 2'b0;

end

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

match <= 1'b0;

else if(c_state == state7)

match <= 1'b1;

else

match <= 1'b0;

end

endmodule

8925

8925

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?