SSTL接口电路标准

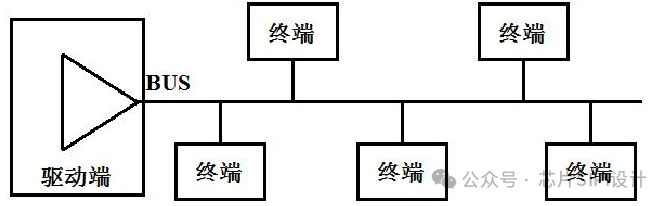

CPU与内存之间的连线,地址、控制线路中是以总线的形式存在着的,即CPU驱动多片颗粒。下图是一种常见的总线示意图。

内存在进入DDRSDRAM时代后,数据传输线速率是时钟线的两倍,即数据速率为双沿采样,即DDR;地址与控制信号在时钟上升沿采样,即仍为单沿采样,即SDR;例如:DDR3-1600,指数据线速率1600MHz,外部时钟线速率为800MHz,地址、控制线仍以时钟上升沿采样,为400MHz。信号速率的提升,带来了信号完整性的问题,而更直接的,即总线终端需采用端接策略。串联的端接不适合多终端拓扑。

下图RS是串联于驱动端的端接电阻,能够有效的抑制因接收端几乎全反射于线路中的电压。但其缺点是,当信号发生逻辑转换时,由于RS的分压作用,在驱动端会出现半波幅度的信号,该信号沿传输线到达接收端,又从接收端反射回驱动端造成信号的延迟,因此串联端接不适合高速电路。图中RTT是并联端接电阻。通过在驱动端并联上拉电阻或下拉电阻或者同时并联上下拉电阻,吸收信号的反射。因此,并联端接是实现数据总线形

式的有效方案。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

612

612

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?