嗯。。。疫情影响各位小伙伴们还好吗。。。博主快炸了,老是担心工作,今年秋招啊。。。

之前一直都是用人家的开发板来直接写逻辑的,但是最好自己还是要做一块嘛。。。最近已经开始动手画了,当然会参考人家现成的东西,谁让他们产品稳定呢,以后有机会会分享一下自己做的开发板,当然比较垃圾啊。我个人想法是想先画一个只有led和开关逻辑的简单FPGA板子,主要走通的流程,至于毕设用的,等等吧,毕竟对DDR3的走线不是那么容易啊。好了废话不多说

先来看一张图

这是A7系列的一张时钟架构,这些专业的名词解释博主在这就不说明了,主要介绍一个单元:BUFG 全局时钟缓冲

很容易从图上看出,BUFG将整个芯片分为上下两部分,那么这个BUFG 到底有什么用呢?很简单,全局时钟缓冲区(BUFG) 驱动全局时钟线,可以简单理解为将整个芯片的时钟统一

至于其他名词,什么水平时钟缓冲啊,区域时钟缓冲啊,大家有兴趣可以去看看,我个人认为初级阶段并不是用的太到吧。。。

那么BUFG由什么驱动呢,当然是专用的时钟管脚啦

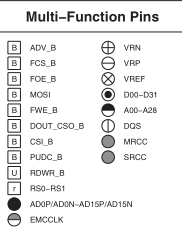

可以看到它可以被MRCC驱动,这个时钟管脚可以服务多个bank,所以外部晶振一定要接这个管脚

MRCC引脚的位置可以查看手册

嗯。。。怎么说呢,具体的FPGA时钟架构需要好好去看它的手册,博主之所以只介绍BUFG和MRCC这两个完全出于初级应用,因为你做板子需要时钟吧,那么连哪个口呢?连哪个bank呢?这是最基本的吧,博主一开始就卡在知道单时钟通过MRCC的p口接入,但是不知道接那个bank和怎么才能连全局时钟。现在明白原来bank可以任意,而全局时钟线是在你写xdc约束时默认接的是BUFG。。。

这样时钟的使用算是初步入门了。由于大部分应用中时钟在整个芯片是统一的,外部的设备需要其他频率可以通过pll等得到,所以我感觉了解这两个应该就可以了吧。。。

哈哈哈写的太烂,主要记录一点自己的心得。。。

1191

1191

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?