http://www.alexforencich.com/wiki/en/verilog/axi/start

1. AXI_CROSSBAR:

M接口连接S接口,所以crossbar的M接口对应于外部的slaver

注意M_ID_WIDTH的宽度要比S_ID_WIDTH多一个维度:$clog2(S_COUNT)

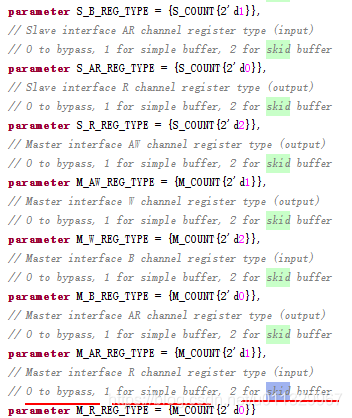

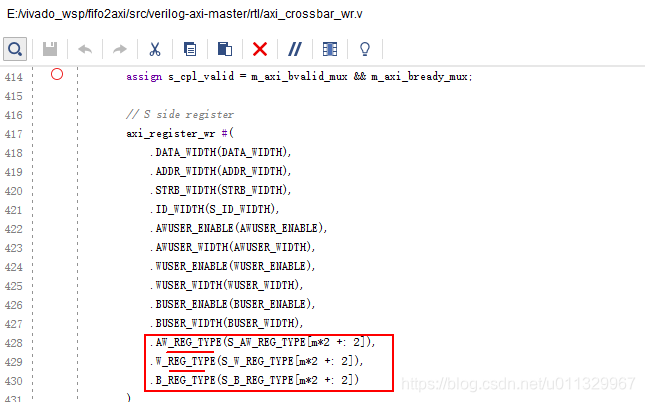

接口buffer设置:

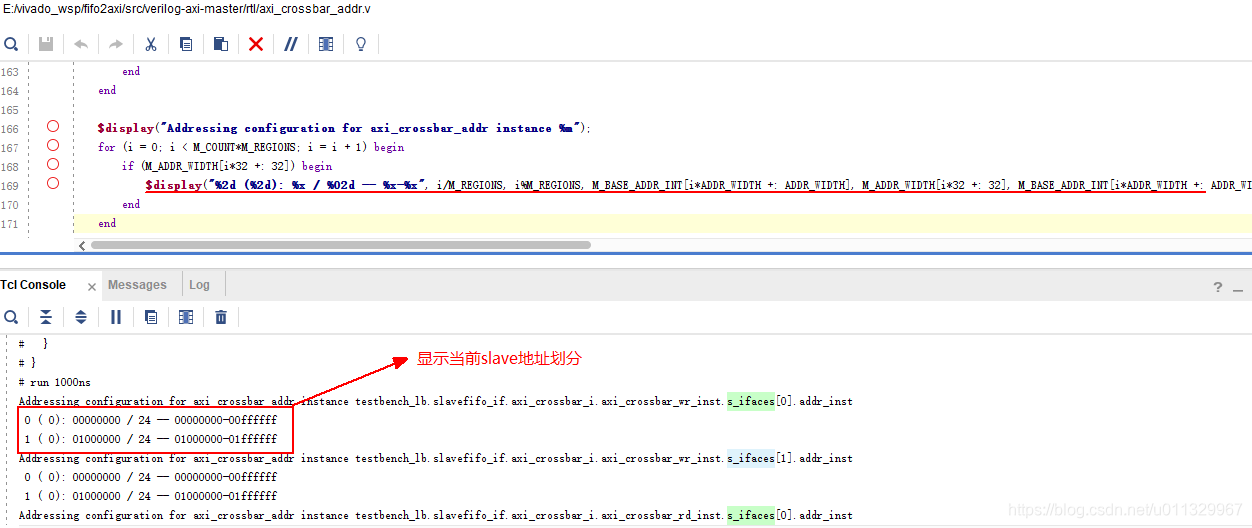

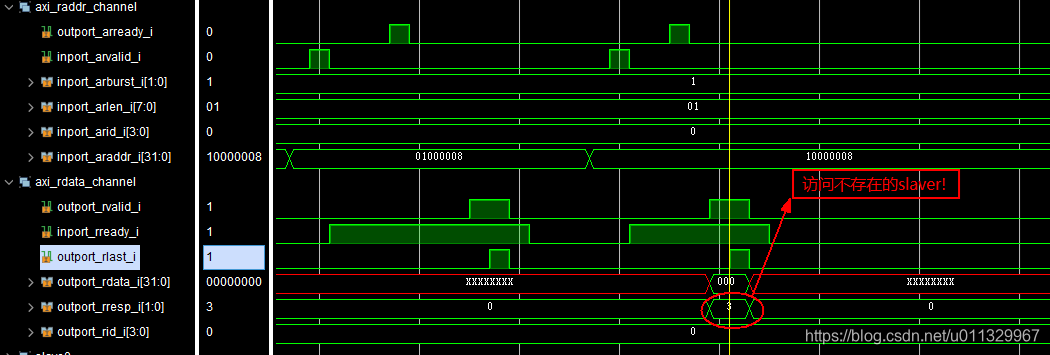

2,使用AXI_CROSSBAR当访问不存在地址时,返回响应3(即DECERR),之后操作出现总线挂死现象:

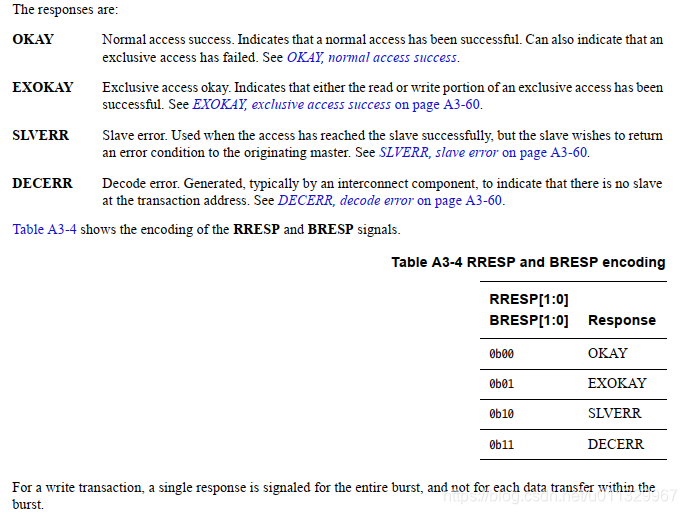

关于地址解码错误:

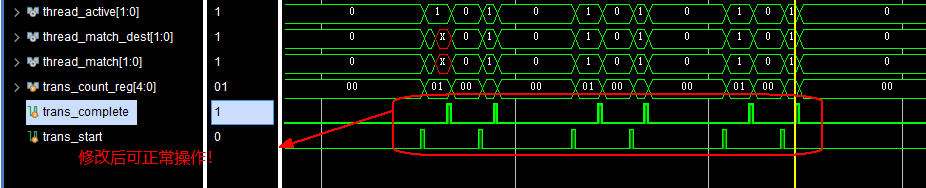

实际波形如下:

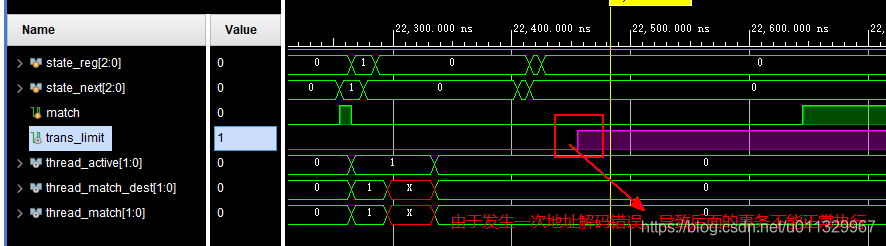

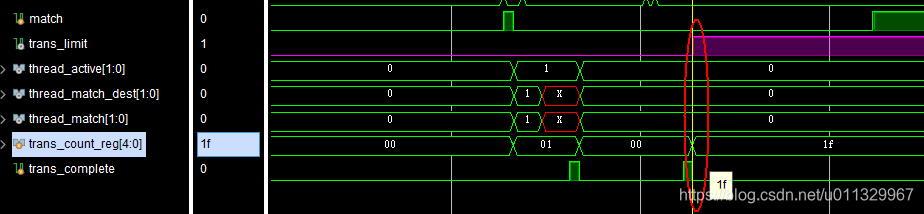

追踪信号可以发现:经过地址解析错误后arvalid信号已经不再下发了:

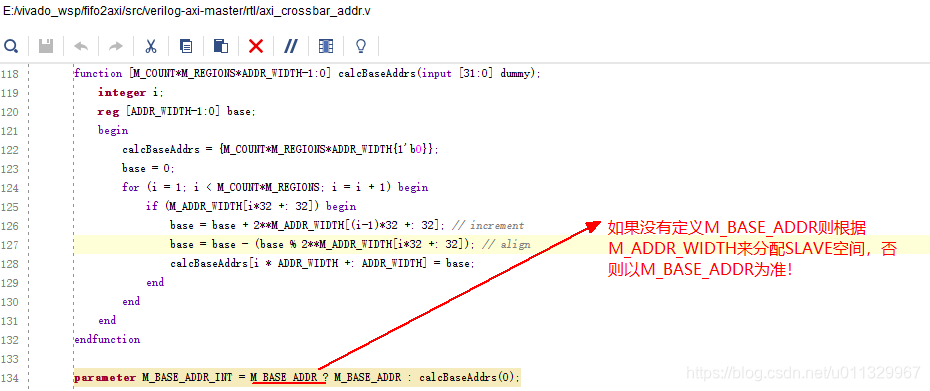

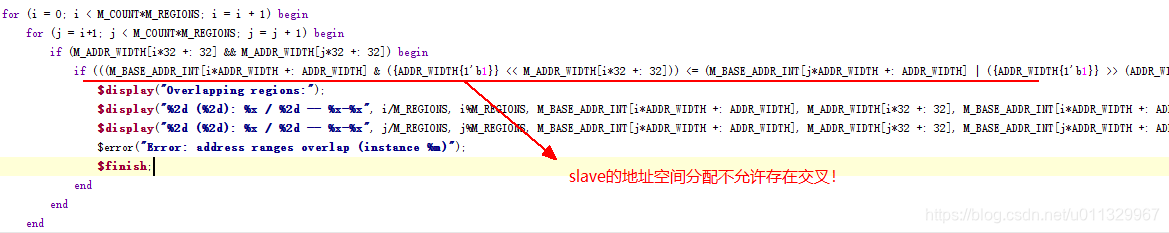

对应代码:/verilog-axi-master/rtl/axi_crossbar_addr.v

![]()

修改如下:

结果:

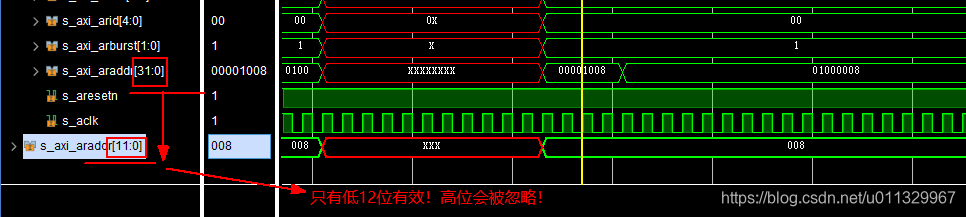

3、AXI_CROSSBAR划分地址后,地址所对应的slaver,只有低位有效,高位会被忽略:

比如slaver实际只有4KB,但划分的地址有64KB,多出的部分会被忽略仍然在低位循环:

同样的当burst访问地址跨slaver时也是如此,跨出范围的部分仍然会低位循环,而不会访问实际的地址:

//--------------------------------------------------------------------------------------------------------------------

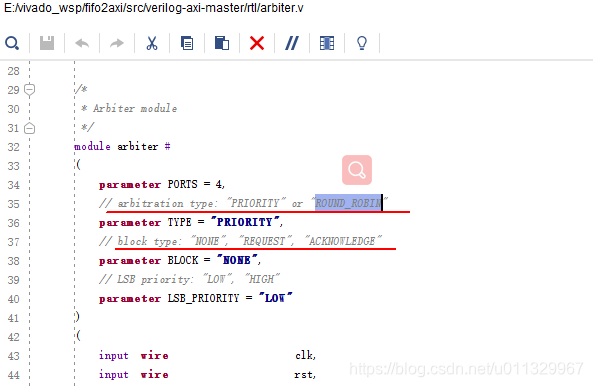

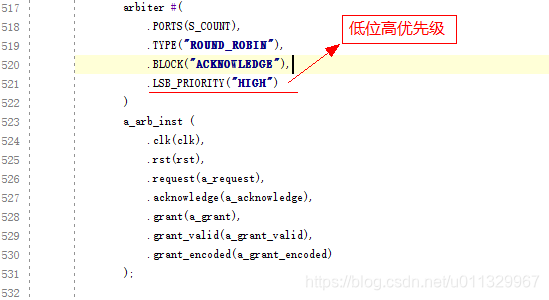

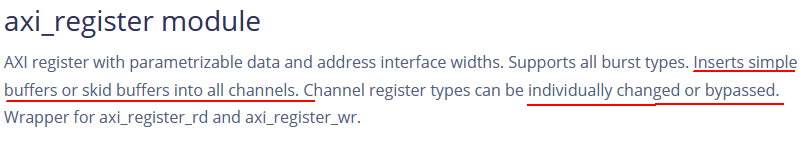

1、axi_register:用于在axi通道上插入buffer,用于改善时序

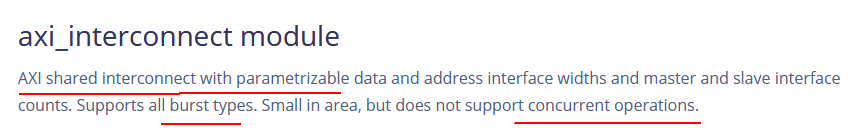

2、axi_interconnect:互联模块,多主多从互联,多主不能同时操作

3、axi_crossbar:同样用于互联,也是多主多从,完全独立通道,虽然描述不是很清楚但功能应该比interconnect更强

4、axi_fifo:axi_adapter:用于位宽适配

5、用于跨时钟域

6、

7、

AXI组件很全但好像缺少了时钟转换模块!

参考:

http://www.alexforencich.com/wiki/en/verilog/axi/readme

1116

1116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?