QRB5165 硬件设计指南(5)

4.9连接性

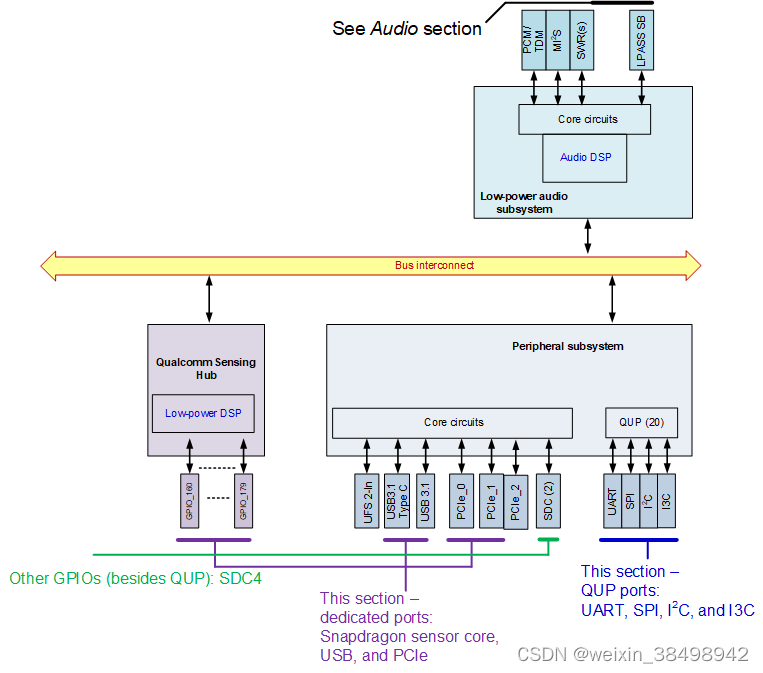

下图是QRB5165的连接图。

4.9.1 通用串行总线

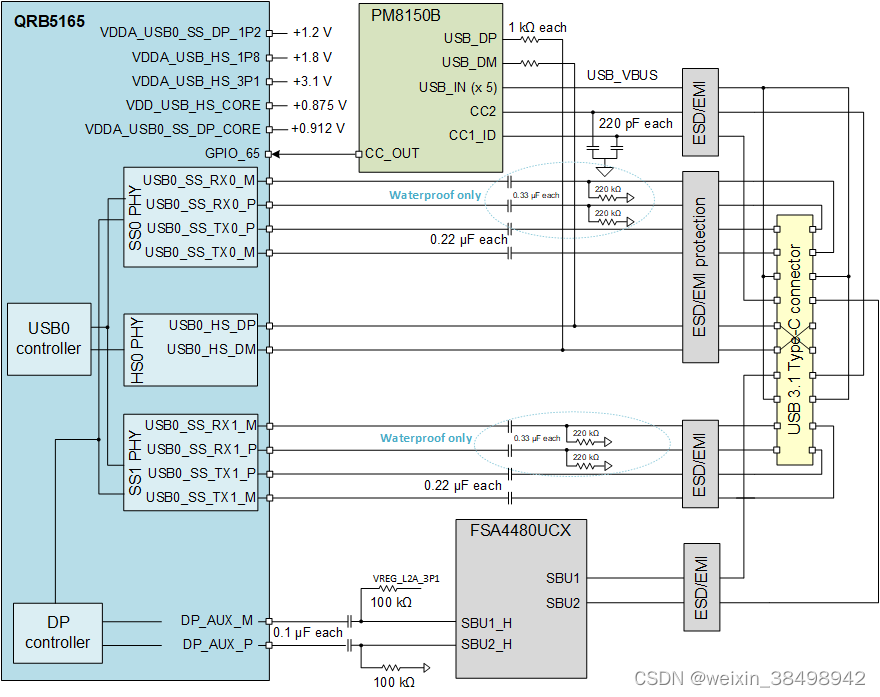

通用串行总线 (USB) 和 PCIe 是 QRB5165 的专用连接端口。

笔记

由于在 USB 3.0 端口上进行了浪涌测试 (IEC 61000-4-5),因此需要将 USB 3.0 PHY 0.9 V 电源(例如 VDDA_USB_SS_DP_CORE/VDDA_USB_SS_CORE 引脚)隔离或与专用 LDO 隔离。

FSA4480UCX 是一款包含 SBU 开关的 USB 音频开关。如果不需要 USB 音频,则可以使用不同的开关来降低 BOM 成本。有关更详细的电路,请参阅设计包、QRD8250、智能手机、电气硬件、PCB 原理图和布局(DP10-VL764-100A)。该框图仅出于说明目的显示了 SBU 开关。

根据 USB 电缆和连接器规范,必须在系统中断开 AUX_M/P 的连接,直到连接切换到 DisplayPort 模式。FSA4480UCX 隔离连接并在需要时切换 AUX_M 和 AUX_P。

根据 USB Type-C 标准中的 VESA DisplayPort Alt 模式,AUX_M 和 AUX_P 上需要 100 kΩ 上拉和下拉电阻。

有一个专用于 USB 1.0 PHY 的辅助 USB 控制器,为简化起见,图中未显示该控制器。

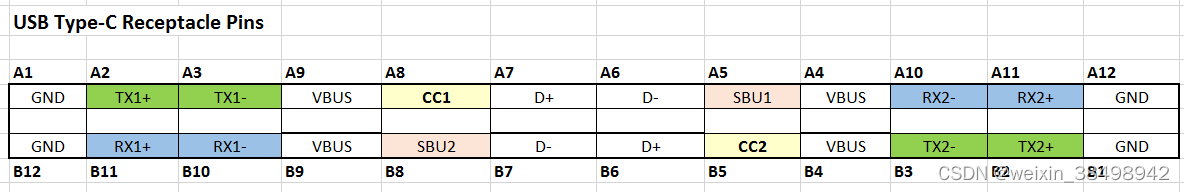

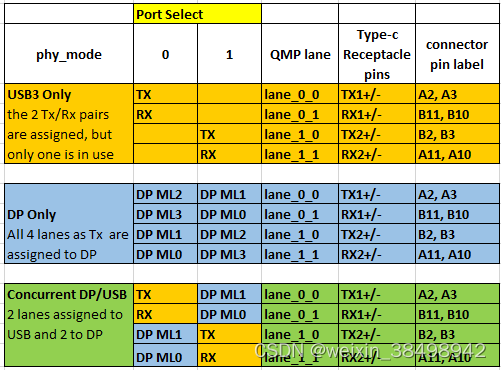

支持USB 3.0和DisplayPort并发模式

USB 模式和 DisplayPort 模式可同时在 USB 3.0 (10 Gbps) 和 DisplayPort (8.1 Gbps) 下运行。在 DisplayPort 模式下:

QRB5165 最多可支持 4 通道 DisplayPort,8.1 Gbps/通道。

可同时支持USB 2.0。

可同时支持USB 3.1。

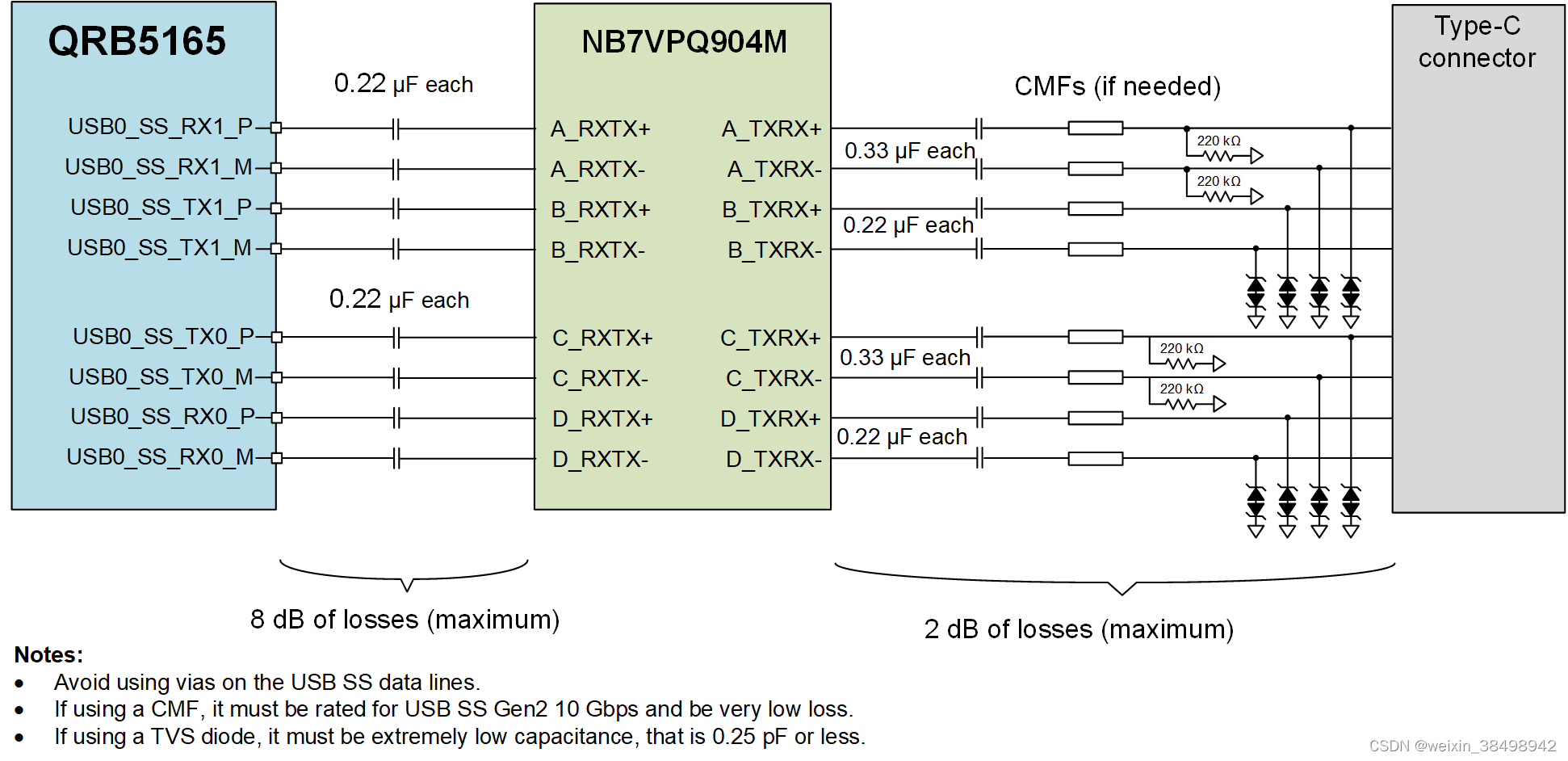

USB 3.1 和 DispayPort 重新驱动程序推荐

为了支持 10 Gbps USB 3.1 Gen 2,由于各种因素,插入损耗预算非常严格。

- PCB走线长度

- 柔性电缆材料

- ESD 和共模扼流滤波器

如果无法满足以下插入损耗预算,则需要重新驱动器(例如,见下图) - 10 Gbps USB 3.1 Gen 2(+ 8.1 Gbps DisplayPort):5 GHz 时为 -7 dB

- 5 Gbps USB 3.1 Gen 1(+ 8.1 Gbps DisplayPort):2.5 GHz 时为-5.5 dB

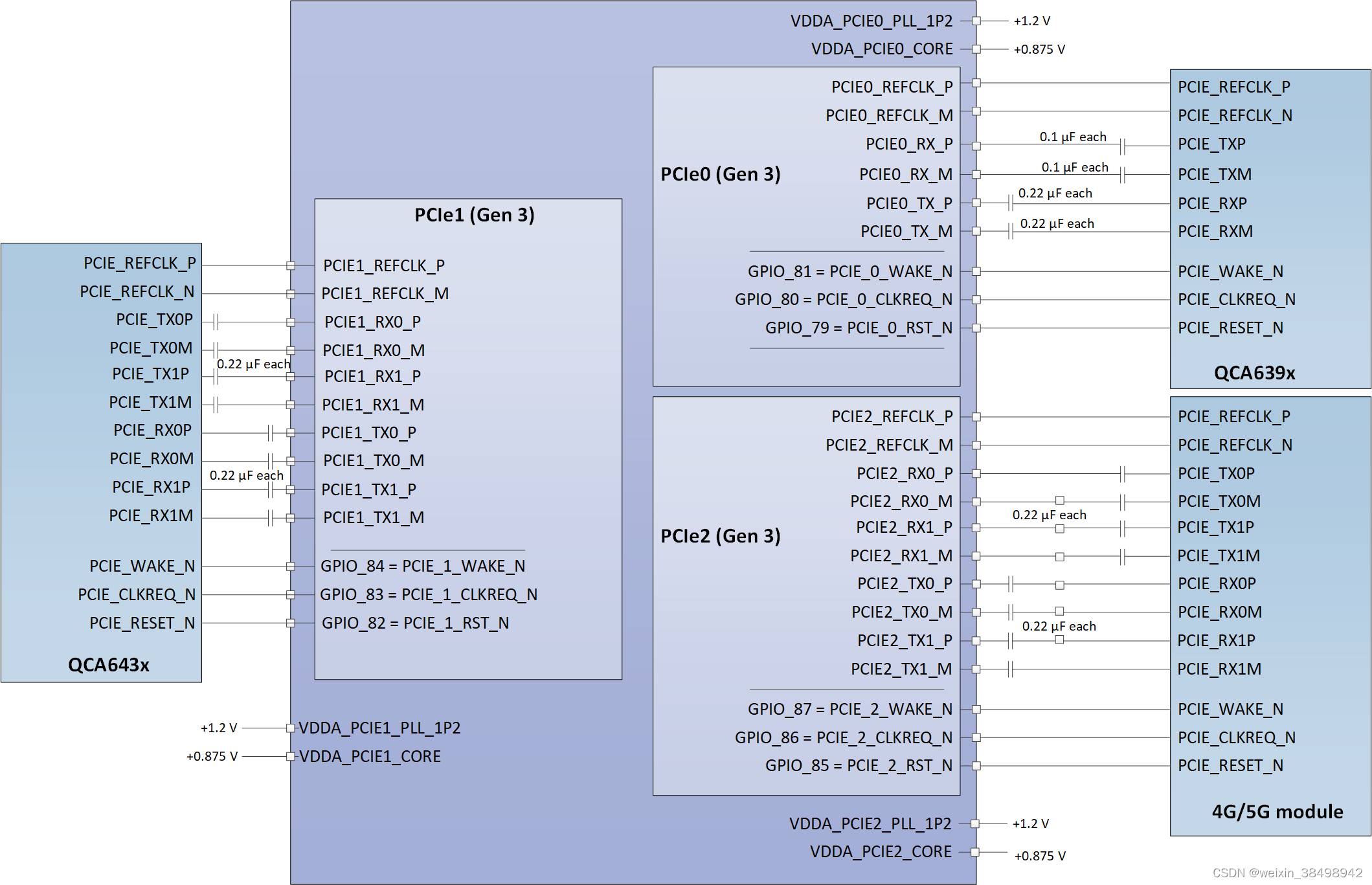

4.9.2 PCIe

QRB5165芯片组具有三个PCIe接口:

- PCIe0 是第 3 代 1 通道接口。它用于连接 QCA639x(WLAN/蓝牙 IC),接口以 Gen2 速度运行。

- PCIe1 是第三代 2 通道接口。它可用于 8011ad(搭配 QCA643x)。

- PCIe2 是第三代 2 通道接口。PCIe2用于连接4G/5G调制解调器IC。

笔记

PCIE_WAKE_N 和 PCIE_CLKREQ_N 信号需要外部上拉。有关更多信息,请参阅 设计包、QRD8250、智能手机、电气硬件、PCB 原理图和布局 (DP10-VL764-100A) 以及Qualcomm Snapdragon SM8150 移动设计参考原理图(80-YB966-47)的 QCA6431 SIP 。

4.9.3 QUP 端口(I 2 C、I3C、SPI 和 UART)

QUP 是高度灵活的可编程模块,支持各种串行接口(I 2 C、I3C、SPI 和 UART)。GPIO 中有 20 个 QUP 引擎,Qualcomm 传感中心 SSC_I/O 中有 8 个 QUP 引擎。每个 QUP 最多有 7 个通道 (I/O),编号从 0 到 6。表中列出了每个 QUP 所支持的分配。在一个 QUP 引擎中一次只能选择一种协议。例如,不再支持同步 UART 和 I 2 C 功能。

笔记

有关详细的 QUP 分配,请参阅QRB5165 数据表(80-PV086-1) 以及QRB5165 引脚分配和 GPIO 配置电子表格(80-PV086-1A)。

可以使用以下两个步骤配置串行接口:

- 引脚配置:请参阅QRB5165 引脚分配和 GPIO 配置电子表格(80-PV086-1A),并通过写入 TLMM_GPIO_CFGn [FUNC_SEL] 字段来选择 GPIO 上的 QUP I/O 功能。例如,如果需要 I 2 C,则只需在 GPIO 上配置 qup_l0 和 qup_l1。如果需要 4 线 SPI,则应在 GPIO 上配置 qup_l0 至 qup_l3。

- 协议选择:通过写入 QUP 寄存器来选择和配置串行协议引擎。

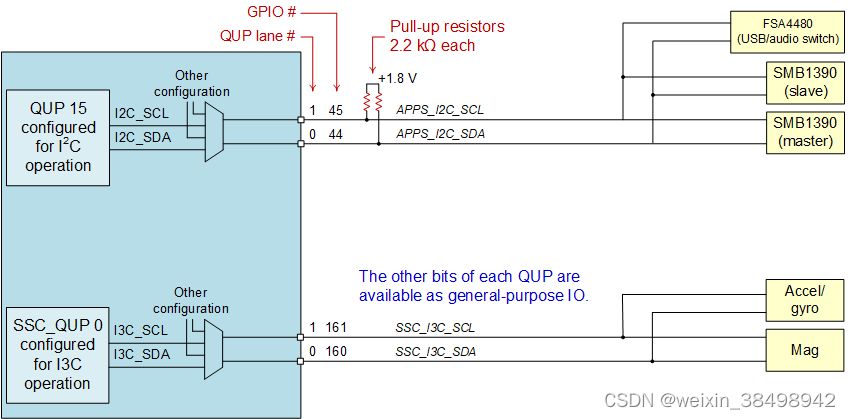

I 2 C 和 I3C

I 2 C 是 2 线总线,可以路由到多个设备;每条总线的每条线路均由一个 2.2 kΩ 上拉电阻补充。

I3C也是2线总线接口,性能更高;每条总线的每条线不需要任何上拉电阻。

每个 QUP 内核均可配置为支持一个 I 2 C 接口,始终使用通道 1 和通道 0。只有某些 QUP 或 SSC_QUP 支持 I3C 接口。

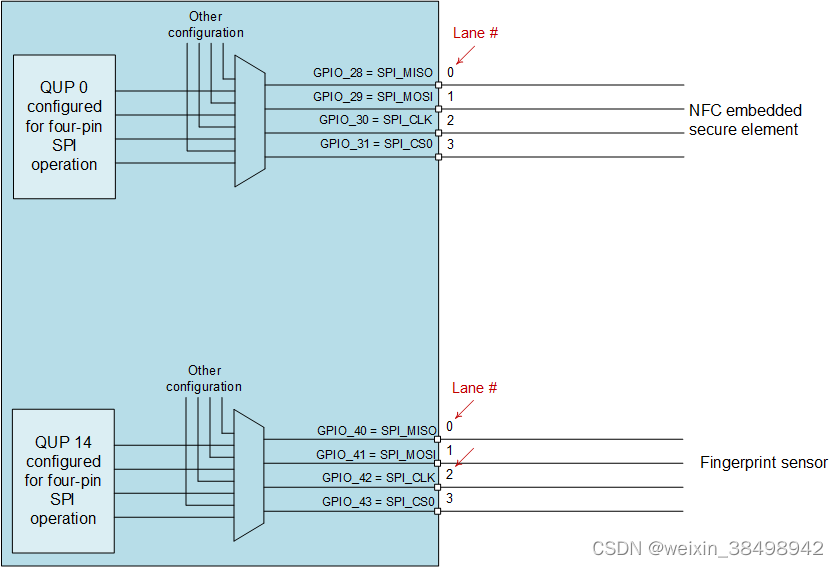

SPI

下图显示了 QUP 端口的 SPI 配置。

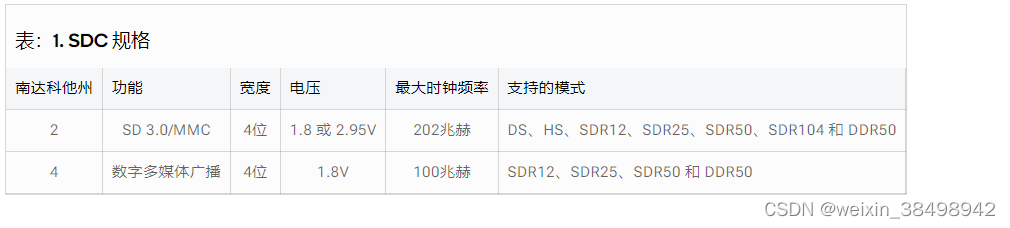

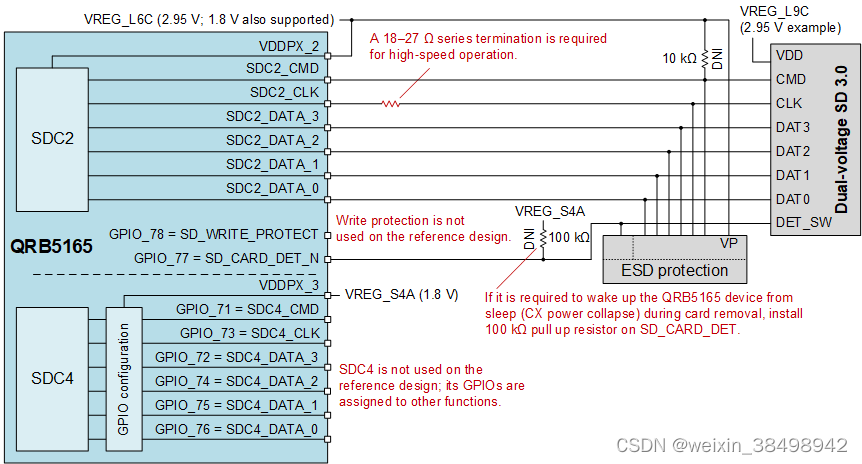

4.9.4 非 QUP GPIO 端口 – SDC

SDC 接口有两个:

- SDC2有专用引脚

- SDC4可通过GPIO进行配置

有关详细信息,请参阅MultiMediaCard/安全数字卡应用说明(80-V7837-1)。

QRB5165 器件不包括 SDC1 和 SDC3 接口。

笔记

SDC4 具有非顺序 GPIO 分配。

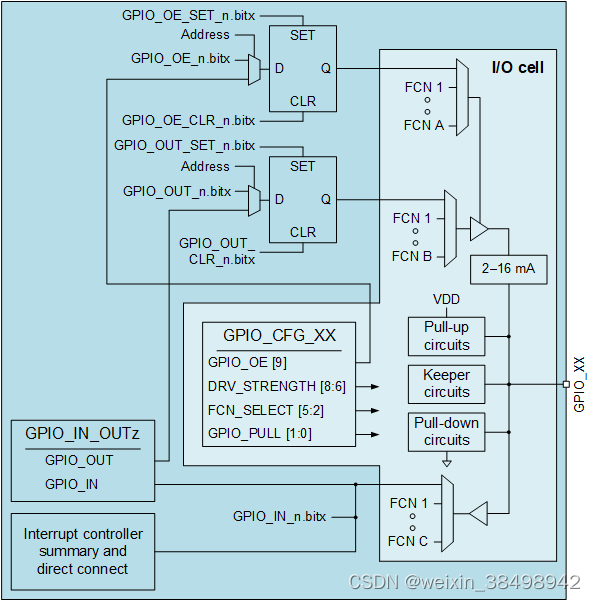

4.9.5 可配置的GPIO

可配置的 GPIO 端口和 MPM 支持

有 180 个 GPIO 端口,其中 146 个是普通 GPIO,配置选项如下所示,其中 34 个称为扩展 GPIO (eGPIO)。

软件将功能分配给 GPIO,并相应地设置它们的配置。

如果通过软件启用 MPM 以降低功耗,则只能使用选定的 GPIO 引脚来唤醒 QRB5165 器件。有关唤醒引脚信息,请参阅QRB5165 数据表(80-PV086-1)。

如果使用 MPM,请小心对待外部拉力。在 MPM 模式下,所有数字垫均由保持器电路保持。如果 MPM GPIO 在 MPM 模式期间由外部芯片驱动,外部反向拉动会导致直流电流流动(在睡眠模式期间非常不希望出现)。如果 MPM GPIO 连接到开漏电路,则需要外部上拉以将 GPIO 保持在预期状态。

PCB 布局必须避免唤醒 GPIO 上的串扰;耦合可能会导致意外触发。

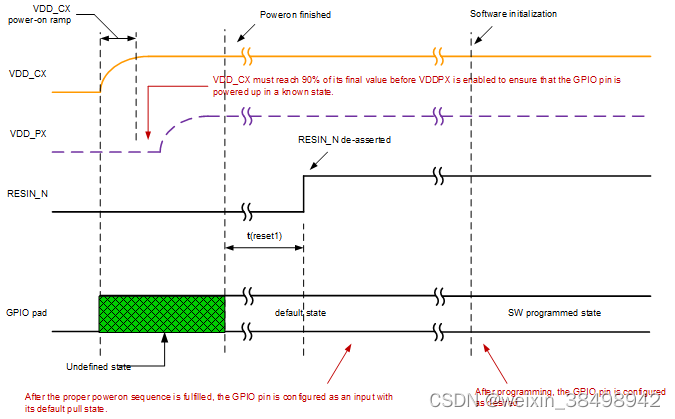

GPIO初始化

为了避免 GPIO 问题,为 QRB5165 器件供电时需要特定的供电顺序。

- 在启用任何焊盘电源 (VDD_PX) 之前,内核电源 (VDD_CX) 必须打开并达到其编程值的 90%。如果没有这些序列和时序关系,GPIO 焊盘可能会出现未定义的状态。

- PM8250 和 PM8150L/PM8150A 确保正确的供电顺序和时序。

建议连接到 GPIO 的外围设备在 RESIN_N 取消置位之前不要驱动信号。

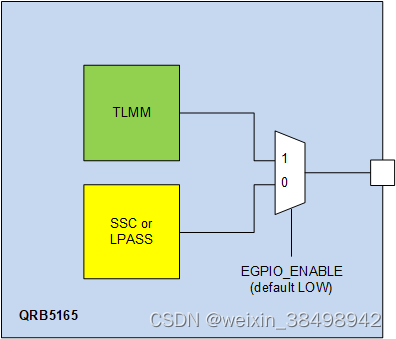

eGPIO 端口

有 34 个扩展 GPIO (eGPIO) 端口:

- 如果需要,eGPIO 允许将 SSC 或 LPASS I/O 重新用作常规 GPIO。

- 其中 20 个默认配置为 SSC GPIO。

- 其中 14 个默认配置为 LPASS GPIO。

每个 GPIO_CFG 寄存器中添加了两个新位以实现 eGPIO 功能。

- EGPIO_PRESENT 是只读位,显示 eGPIO 功能在特定 GPIO 上是否可用。在 QRB5165 中,该位仅对于 GPIO 146 至 GPIO 179 为 1,对于 GPIO 0 至 GPIO 145 为 0。

- EGPIO_ENABLE 是读/写位,仅在 EGPIO_PRESENT 为 1 时有效。设置后,eGPIO 由芯片 TLMM 块控制,而不是由 SSC 或 WCSS 控制。

有关 eGPIO 的更多信息,请参阅QRB5165 引脚分配和 GPIO 配置电子表格(80-PV086-1A) 和QRB5165 硬件寄存器描述(80-PV086-2X)。

2141

2141

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?