4.3多媒体

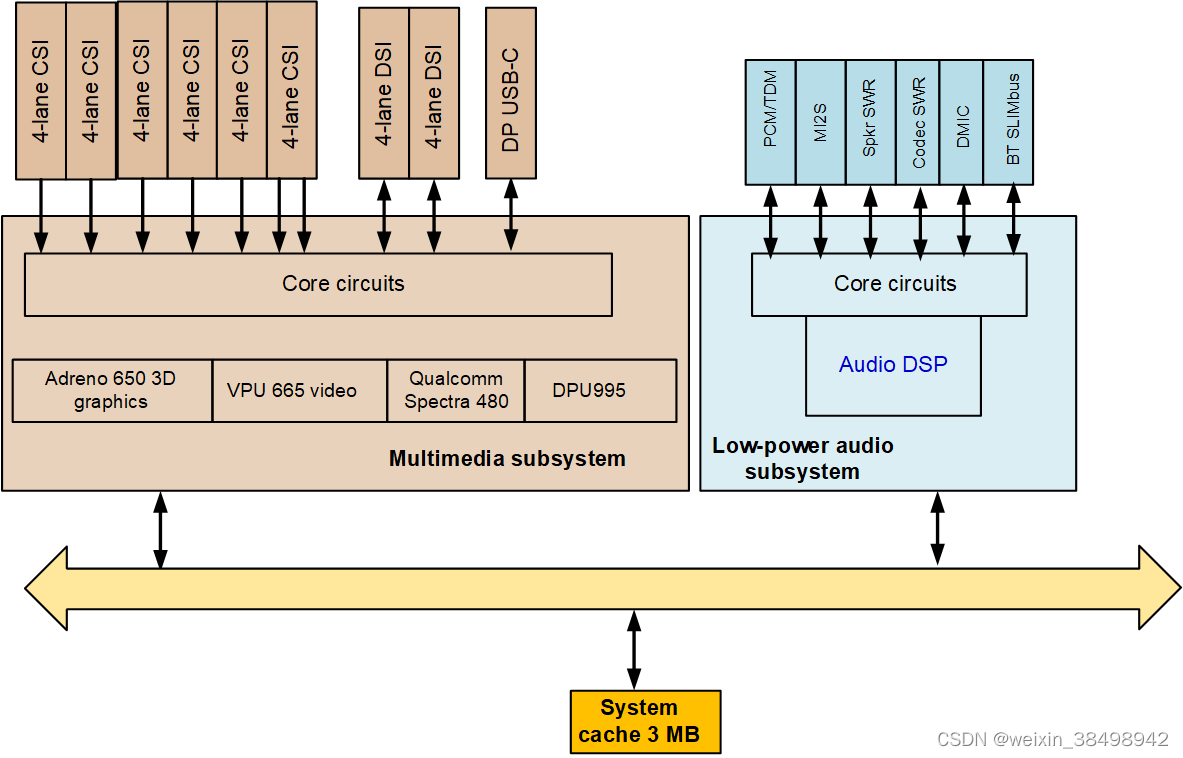

下图显示了QRB5165多媒体子系统。

4.3.1 展示

下面列出了 QRB5165 的显示概述。

- QRB5165 芯片组最多可支持三台 4K 显示器(一台通过 DSI 的内部显示器,两台通过 DisplayPort 的外部显示器)。

- 该器件还可以支持 5040 × 2160 @ 60 Hz、两个 2560 × 2560 @ 120 Hz 的双显示、高达 30 bpp 4096 缓冲区宽度和 16 个硬件层组合。

- 该子系统具有集成时钟控制器。

- 两个 4 通道 DSI D-PHY 1.2 或两个 3-trio C-PHY 1.1,带 VESA DSC v1.1。

- 支持 8.1 Gbps/通道的集成 DisplayPort v1.4。

- 通过 USB 3.1 Type-C 并行运行 4K60 DisplayPort 和 USB 3.0。

- 多流传输支持最多两个 4K60,其中任意一个流上有两个视频流、一个音频。

- 通过使用系统缓存、Qualcomm Snapdragon 通用带宽压缩 4.0 和 RPMh 的内联旋转来提高功耗。

4.3.2 相机

高通 Spectra 480 相机 ISP

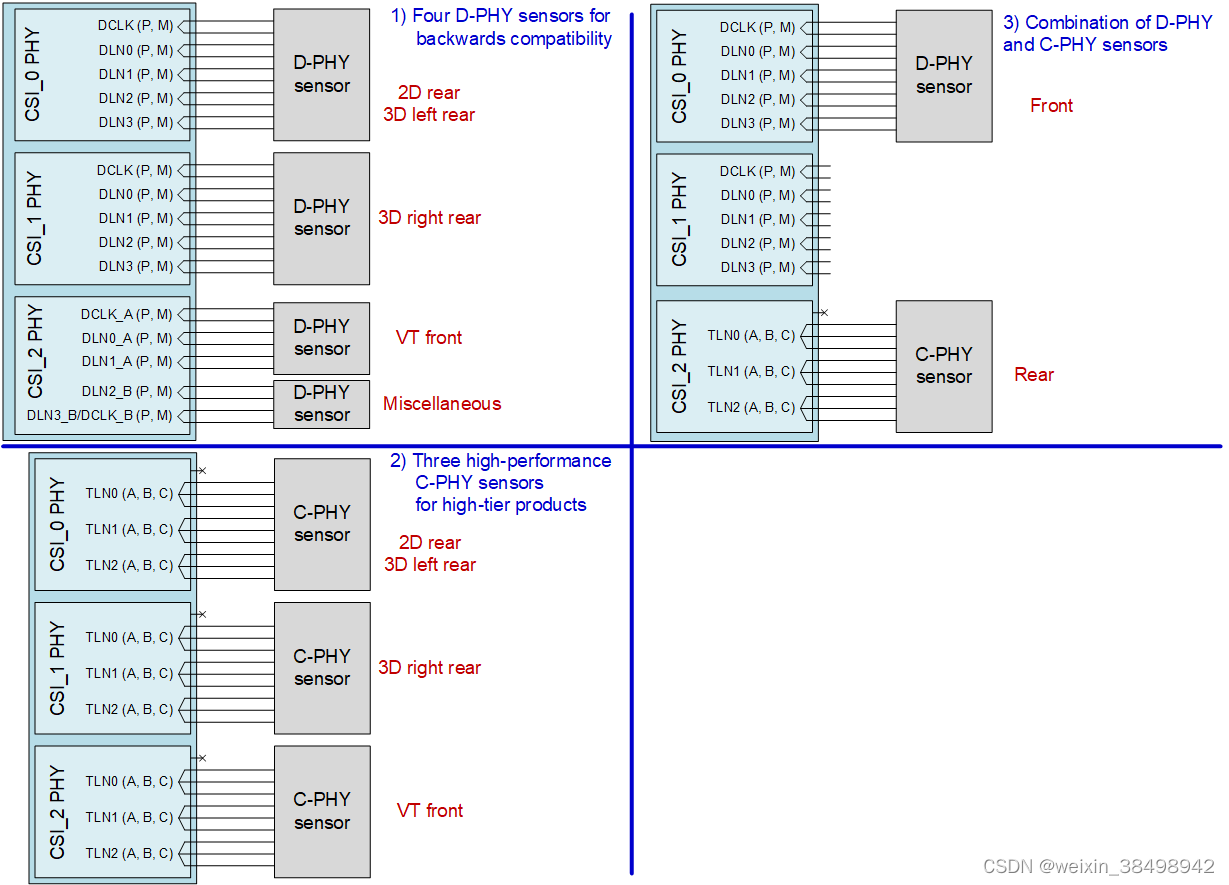

QRB5165 器件采用 Qualcomm Spectra 480 摄像头架构,该架构具有六个用于外部摄像头的接口 - 六个带有 CSI D-PHY 1.2 或 C-PHY 1.2 的 4 通道接口。

D-PHY 和 C-PHY 各有一个 1.2 接口,数据速率为 2.5 Gbps/lane,1.2 接口的数据速率分别为 10.26 Gbps/T (4.5 Gsps/T)。

QRB5165 器件可连接 6 个摄像头 (4 + 4 + 4 + 4 + 4 + 4) 或最多 12 个 (D-PHY)/18 (C-PHY) 摄像头。它可以支持七个摄像头并发使用。对于双摄像头,同步是通过 VSYNC 引脚完成的。

QRB5165 相机架构支持 HVX 流。

Qualcomm Spectra 480 摄像头架构可支持 25 MP + 25 MP + 2 MP + 2 MP + 2 MP + 2 MP + 2 MP ISP 配置。

- IFE0 – 25 MP

- IFE1 – 25 MP

- IFE_Lite0 – 2 MP 原始接口

- IFE_Lite1 – 2 MP 原始接口

- IFE_Lite2 – 2 MP 原始接口

- IFE_Lite3 – 2 MP 原始接口

- IFE_Lite4 – 2 MP 原始接口

最多七个并发摄像头

位于 VPU 中的专用计算机视觉处理器 (CVP)

- 从 CPU、计算 DSP、GPU 和 NPU 卸载基本 CV 任务

- 降低整体用例功耗并提高系统性能

CSI差动和三相

CSI 差分和三相配置如下:

- 每通道 6 个 4 通道 CSI (4 + 4 + 4 + 4 + 4 + 4) D-PHY 1.2,速率 2.5 Gbps,或 6 个 3-trio C-PHY 1.2,速率 30.78 Gbps。

- QRB5165 芯片组支持 C-PHY 1.2,该芯片组使用带有嵌入式时钟的单端信号(每三线三线)。

笔记

当CSI PHY用于2+1双摄像头模式时,仅DLN3可以用作第二摄像头的CLK。

笔记

这些只是示例配置。其他配置也是可能的。

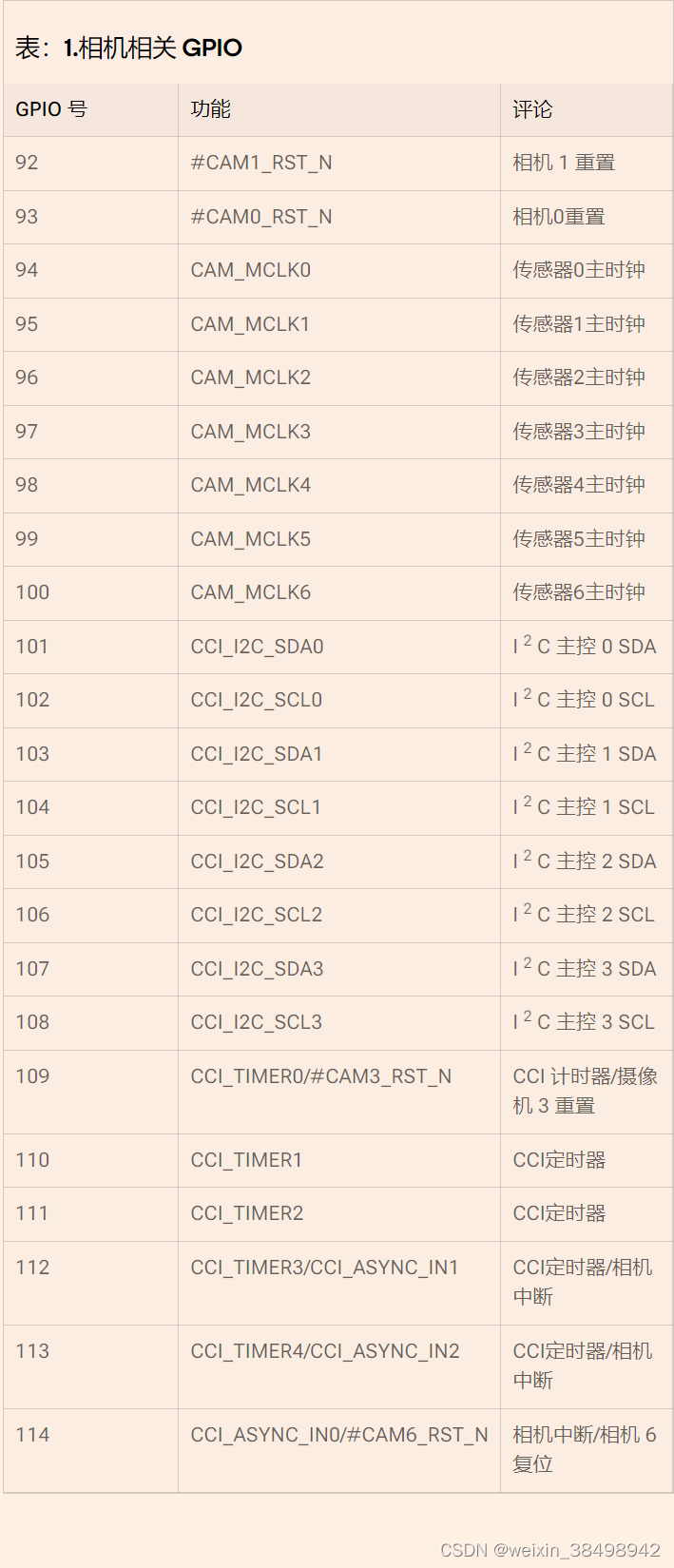

用于相机控制接口的专用相机 I 2 C 端口

除了 QUP I 2 C 端口外,还有四个 I 2 C 端口专用于相机控制接口 (CCI);请勿将 GPIO_101–GPIO_108 用作通用 I 2 C 端口。

根据使用情况,前置摄像头和后置摄像头可以共享 CCI_I2C 端口,也可以具有单独的 CCI_I2C 端口。

默认情况下,它最多可支持七个以 19.2 MHz 运行的 CAM_MCLK。

- 默认频率下,CAM_MCLKx 峰峰值抖动 < 400 ps。

- 在使用 19.2 MHz 以外的任何 CAM_MCLK 频率之前,请联系 QTI 客户工程人员,以调查此类情况下抖动是否可接受。

相机相关GPIO

下表列出了相机相关的 GPIO。

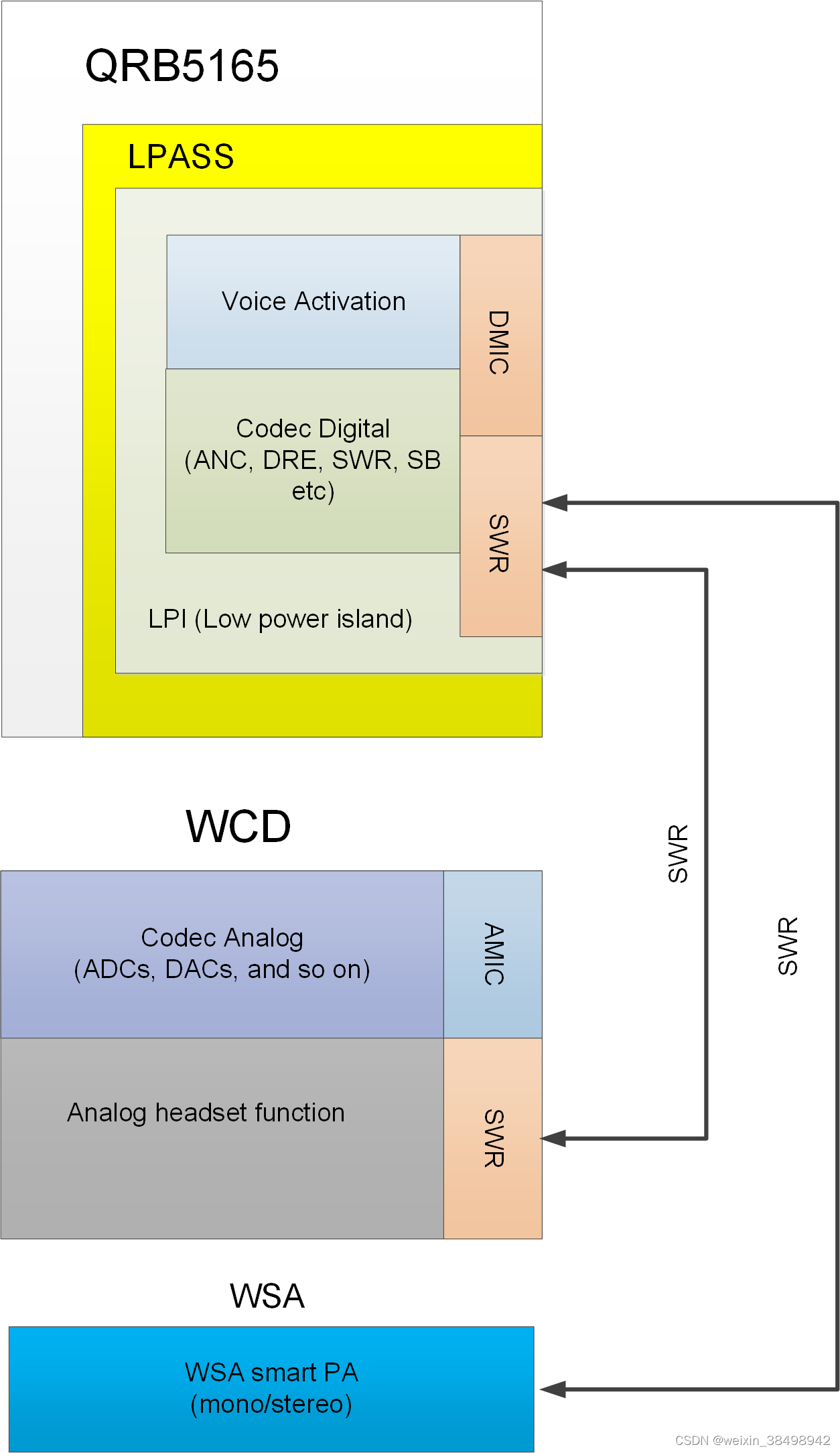

4.3.3 声音的

有关 QRB5165 LPASS 的详细信息,请参阅SM8250/SXR2130P/QRB5165/QRB5165N/QCS8250/QCS8245 音频编解码器硬件概述设计指南/培训幻灯片(80-PL546-5C)。

有关设计详细信息,请参阅Qualcomm Aqstic WCD9380/WCD9385 音频编解码器硬件设计指南/培训幻灯片(80-PL335-5)。

4.4高通传感中心

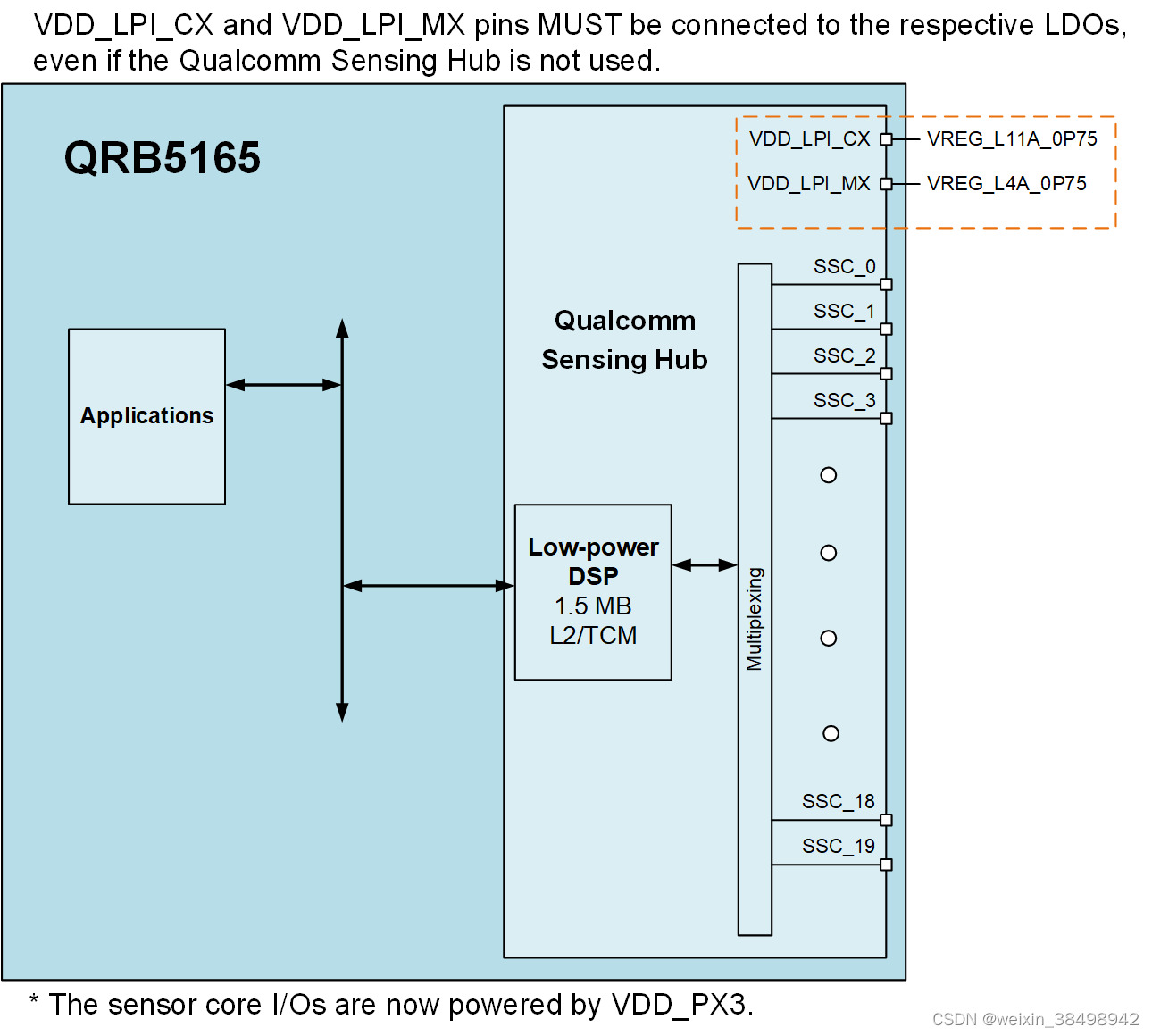

QRB5165 设备具有一个名为 Qualcomm 传感中心的集成传感器子系统,专门用于支持低功耗、始终在线的用例。Qualcomm 传感中心拥有自己的专用电源轨 – VDD_LPI_CX 和 VDD_LPI_MX。即使 QRB5165 器件的其余部分处于睡眠模式,传感器子系统也可以保持通电状态。

Qualcomm 传感中心采用低功耗 Hexagon DSP 进行处理。Qualcomm Hexagon DSP 具有专用的 1.5 MB L2/TCM 缓存。

Qualcomm 传感中心具有专用 I/O(SSC_0–SSC_19 复用在 GPIO_160 至 GPIO_179 后面)来与传感器进行通信。Qualcomm 传感中心中有八个 QUP 核心。I/O 可支持 UART、I 2 C、I3C 和 SPI 接口。

Qualcomm 传感中心可以直接访问内部核心,以支持各种传感器用例。当 GPIO_160 – GPIO_179 配置为 SSC_0–SSC_19 时,它们不能用于非 Qualcomm 传感集线器用例。它们专门供 Qualcomm 传感中心 Hexagon DSP 使用。

对于传感器中断,任何可用的支持 MPM 的 GPIO 都可以使用 TLMM 寄存器作为中断路由到 Qualcomm 传感中心子系统:

- TLMM_WEST_MPM_WAKEUP_INT_EN_0

- TLMM_NORTH_MPM_WAKEUP_INT_EN_0

- TLMM_NORTH_MPM_WAKEUP_INT_EN_1

- TLMM_SOUTH_MPM_WAKEUP_INT_EN_0

笔记

任何可用的 MPM GPIO 都可以路由到 Qualcomm 传感中心。请参阅相关软件文档或在 Salesforce 中向软件团队提交案例以了解详细的代码更改。

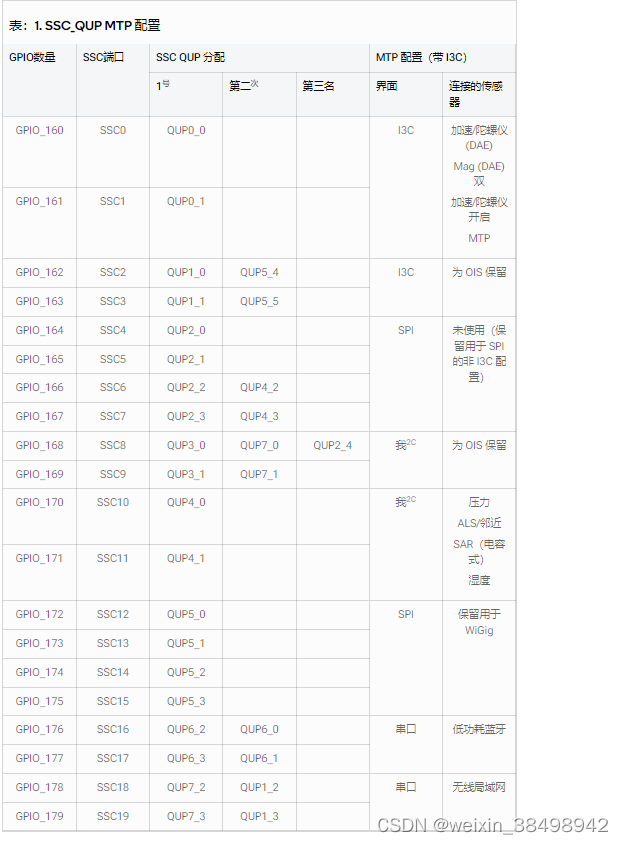

4.4.1 SSC_QUP MTP 配置

这是 QTI 将支持的传感器配置之一。连接到SSC0_1(I3C)、加速度/陀螺仪和磁力计的传感器使用DAE(数据采集引擎)。即使对于 I3C,也应为加速度和陀螺仪传感器保留中断引脚。QRB5165 上的 I3C IBI 支持不会商业化。有关最新信息,请参阅QRB5165 Linux Ubuntu 软件参考手册 (80-PV086-100)。MTP 具有连接到同一 I3C 总线的双加速器/陀螺仪。

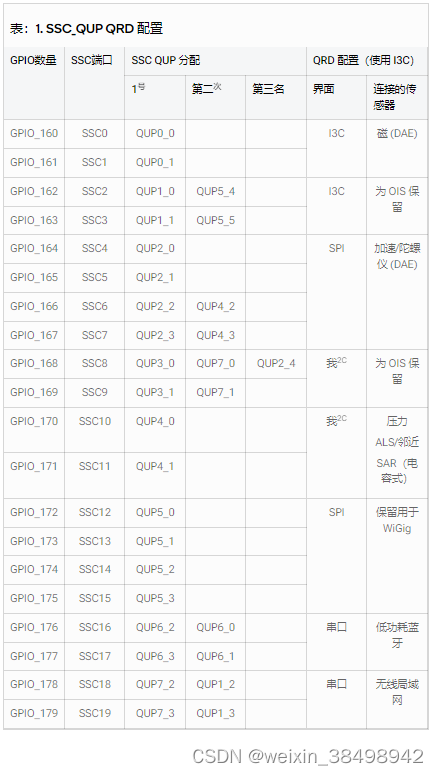

4.4.2 SSC_QUP QRD 配置

SCC_QUP QRD 是 QTI 支持的第二个配置。对于此配置中的 DAE(数据采集引擎)支持,加速器/陀螺仪应连接到专用 I 2 C 总线 SSC_0_1 上的 SSC_4_7 (SPI) 和磁力计。其他传感器不应共享 SSC_0_1。有关详细信息,请参阅QRB5165 Linux Ubuntu 软件参考手册(80-PV086-100)。

本文详细描述了QRB5165芯片组的多媒体子系统,包括支持的显示、相机接口和特性,以及高通传感中心的传感器配置。涉及的组件和技术如DSI、DisplayPort、摄像头架构、HexagonDSP和I/O接口等都被详细介绍。

本文详细描述了QRB5165芯片组的多媒体子系统,包括支持的显示、相机接口和特性,以及高通传感中心的传感器配置。涉及的组件和技术如DSI、DisplayPort、摄像头架构、HexagonDSP和I/O接口等都被详细介绍。

2077

2077

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?