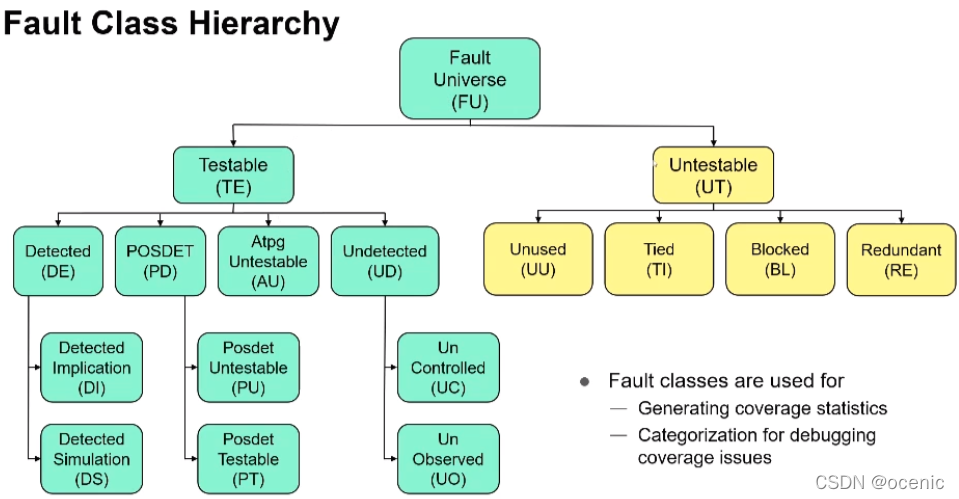

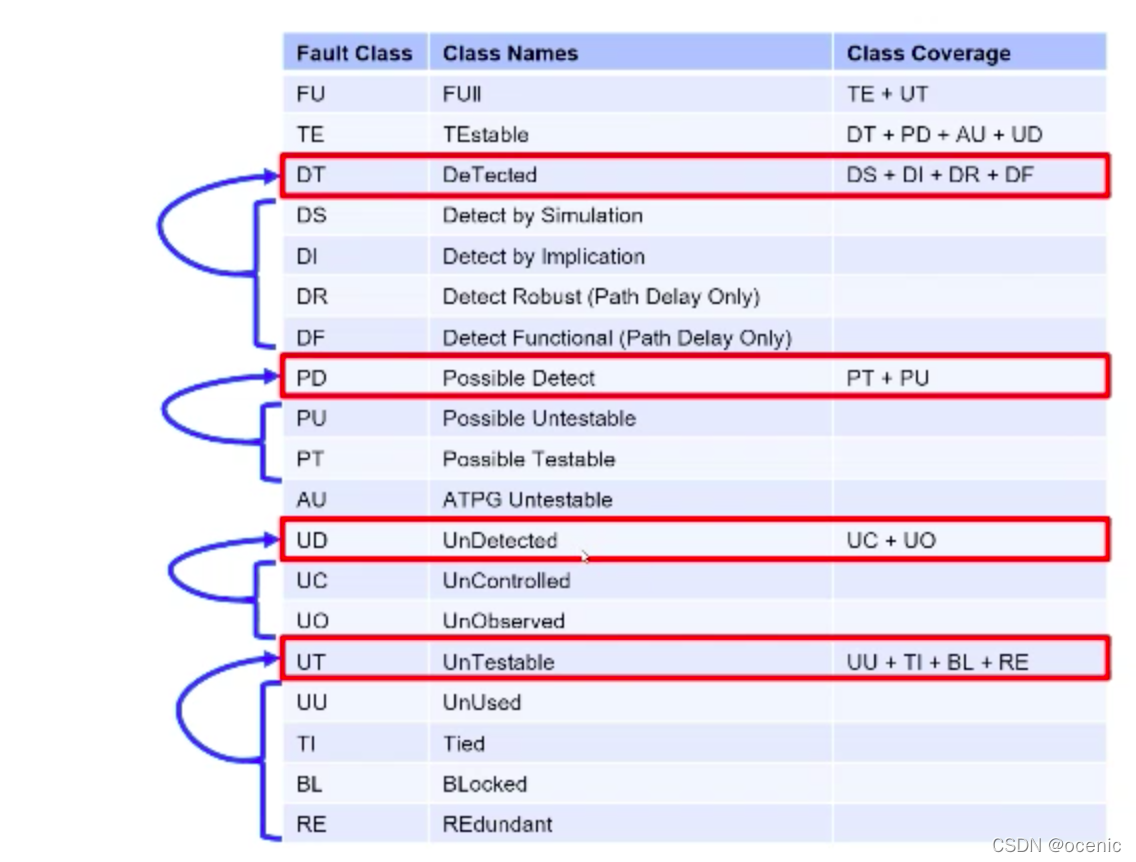

Fualt 的分类

在使用 report_statistrics报告scan chain 的总结性的报告时,会出现每种fault的数量 以及对覆盖率的影响,

TE(testable)

Detect by implication (DI)隐含检测

在scan chain 数据路径上的 faults被标记为 隐含可检测

通过推算电路就知道这些点可以被测到,这些fault location是测试电路的一部分.

扫描链的测试pattern (使用write_pattern 创建的)就可以检测到这些fualt;

creat_patterns 不会再产生DI fault 的pattern;

指那些 我们在shift 扫描链的时候 用到的那些信号 及所涉及的测试电路结构,包括但不限于 SI SO 扫描链寄存器的 D Q 等;

TE : detect by simulation (DS)

在推pattern,执行fault simulation的时候去看simulation的结果 比较 good circuit simulation和 fault circut simulation,两者之间不一样 那么这个fault 就是可以被detected;

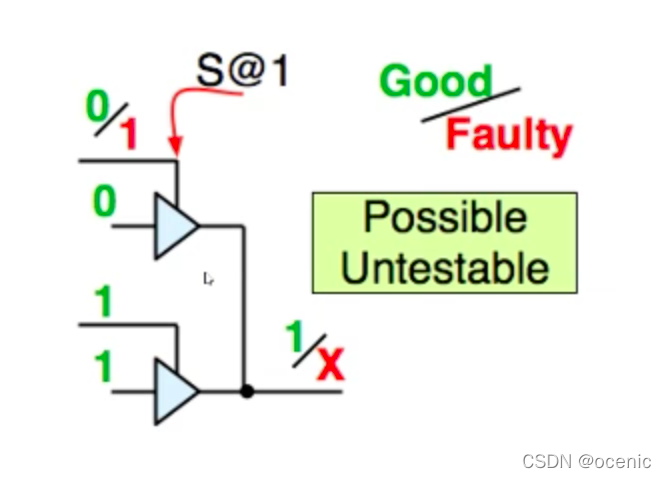

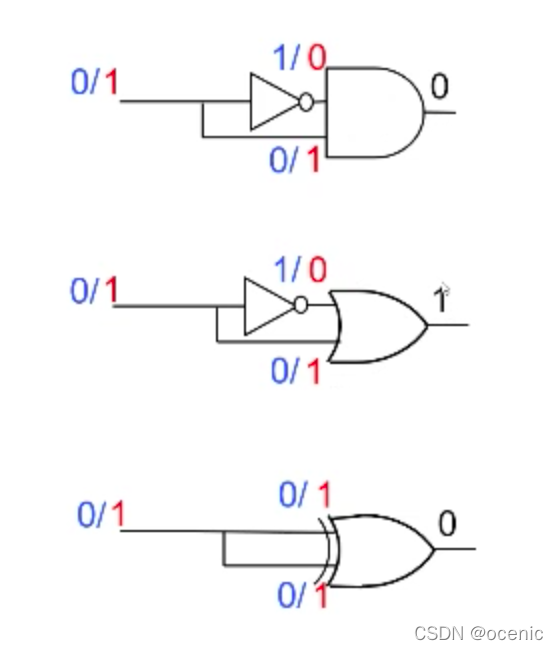

TE: Possible Detect fault (PT PU)

possible detect (POSDET) ,包含那些在fault simulation中识别到的作为可能检测到的但不肯定被检测到的所有fault;

possible detected fault 是由于当 good simulation的结果是(0 或 1) 而fault simulation的结果是 X 的时候

这时候 是有50% 的可能性可以detected;

默认 calculation 会给一个 50% 的可能性 给posdet fault 你可以调整credit 的百分比:

set_possible_credit N

TE ATPG untestable (AU)

AU 包含那些 ATPG 不能找到一个pattern区创建一个test 也不能提供一个 fault 的redunction 的那些fault; 所以 AU 是肯定会影响你的coverage的;

AU 可能有下面的情况产生:

constraints (约束阻止ATPG工具去产生一个pattern 检测fault);

No-Scan的 memory elements(未被替换的 no_scan cell) 以及不够的时钟时序深度; 工具很难去推算pattern (sequential depth很深的 no-scan cell 由于depath 太深 工具很难去推算pattern 就很难测试到了)

blocking condition from black boxes other tied or constrained logic.(black box 以及受black box 关联的逻辑 )(black box 的输入是不可观测的 输出是不定态,其前置逻辑和后置逻辑的 可观测性都会丢失掉)

TE : uncontrolled (UC) & unobserved (UO)

UC: 在test pattern生成之前 所有的testable fault 都被归类为 UC;

二是 那些没有办法为特定的fault设置成需要的状态的fault location 也会被标记为 UC;

UO: fault location 不能被propagated(推演)到一个可观测的点的 湖北归类为 UO;

如果在 pattern生成之后 一个fault location被同事标记为 UC 和 UO 那么他会最终标记为UC;

TE: UC UO & Aborted fault

在 pattern生成之后 UC UO fault 中的一部分会被标记为 AAB (ATPG Abort) 那些需要更多的effect 才能detect到的fault 就会被归类到AAB中 可以通过修改 abortlimit 尝试解决aab的fault

ATPG abort limit 一个数字 定义了解决目标location的 control 和 observe问题所使用的计算资源的数量,包含了使用附加的ATPG 预算引擎去生成pattern 去检测错误;

abort limit 数越高 在ATPG中每个fault 所做的尝试就越多;

create_pattern 会涉及一个abort limit 在pattern generation的时候根据需要进行调整;

UT

这里的UT (untestable) 是指根本就不能测试 或者不用测试的loaction;

包括:

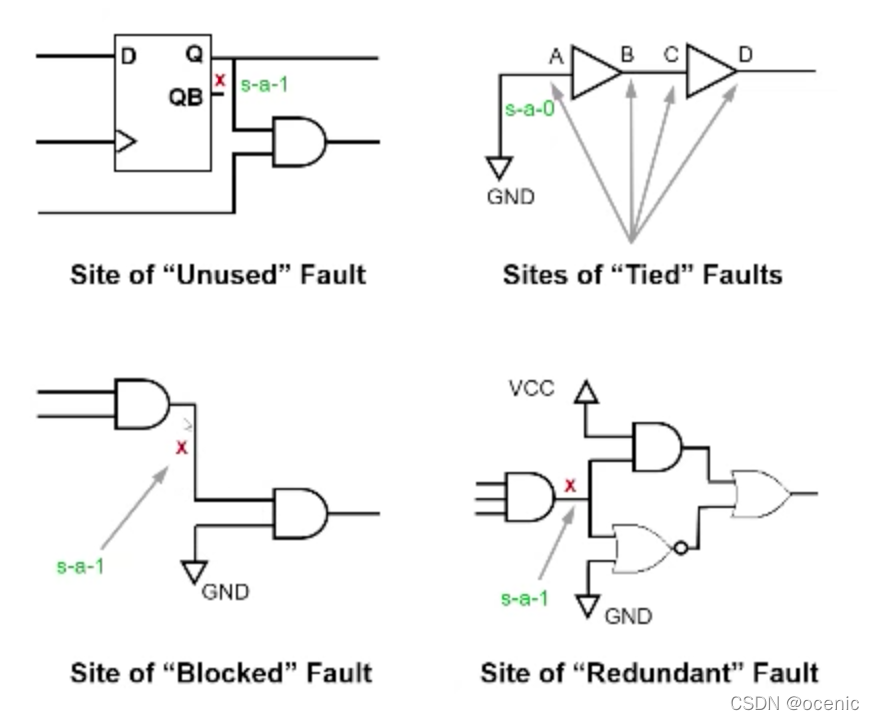

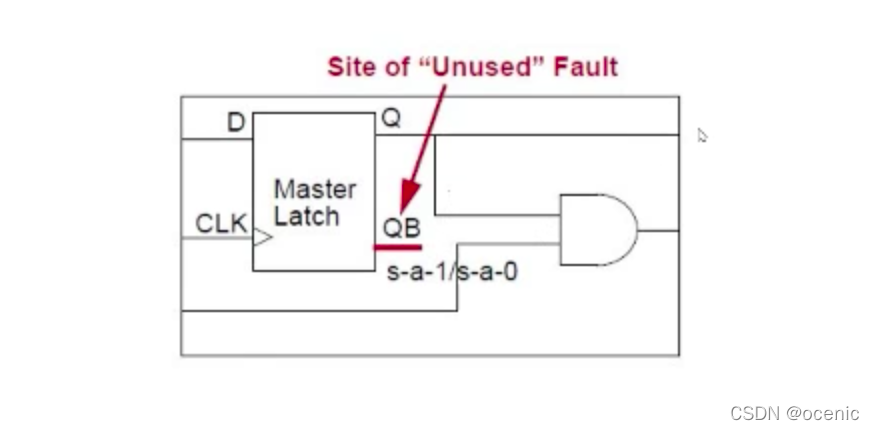

unused(UU)

Tied(TI)

Blocked(BL)

Redundant(RE)多余的

UU

例如 在触发器的 QB输出是floating的 是没有可观测的路径的;

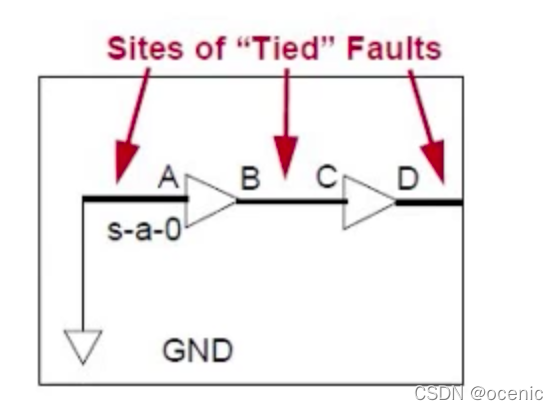

TI

the tied fault 包含那些 fault 点tied 的值与stauck @ 的值相同的 loacation;

tied 电路可能是由于:

- tied signal 恒高恒低的信号;

- 有着互补输入的与门 或门

- 有着相同输入的 与非门

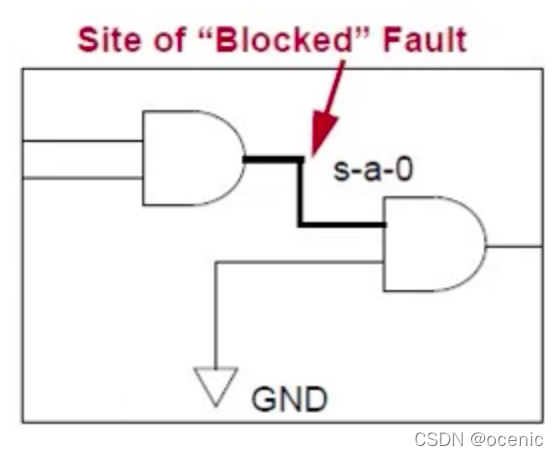

BL

fault point 的值没有办法往后传递; 这是由于 block的控制可观测路径是不可用的;

可能是由于设计中的 black box引起的;

RE

\冗余的fault 在现在的设计中很少 一般在综合工具中 都会处理掉;

all fault review

492

492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?