序言

我胡汉三又回来了!继续开更!!之前由于种种原因断更了许久,现在准备断点续更,继续和大家分享自己的学习所得。着实是水平有限,很多不足或者有误的地方还请不吝指出!

更新内容主要还是以Tessent的工具书为中心,同时扩展自己所见所得(可能是来自于项目经验或者设计)。OK,废话不多说,上菜!

第一回

第二回

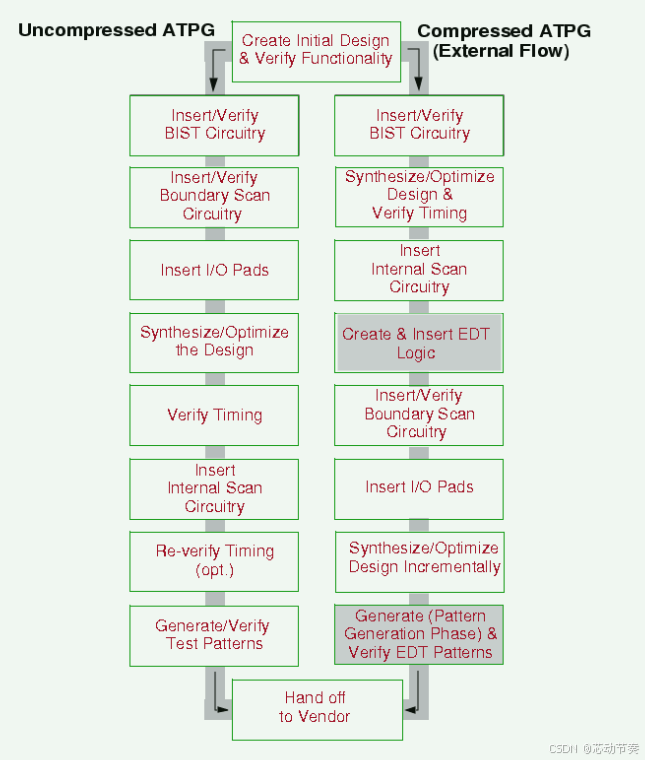

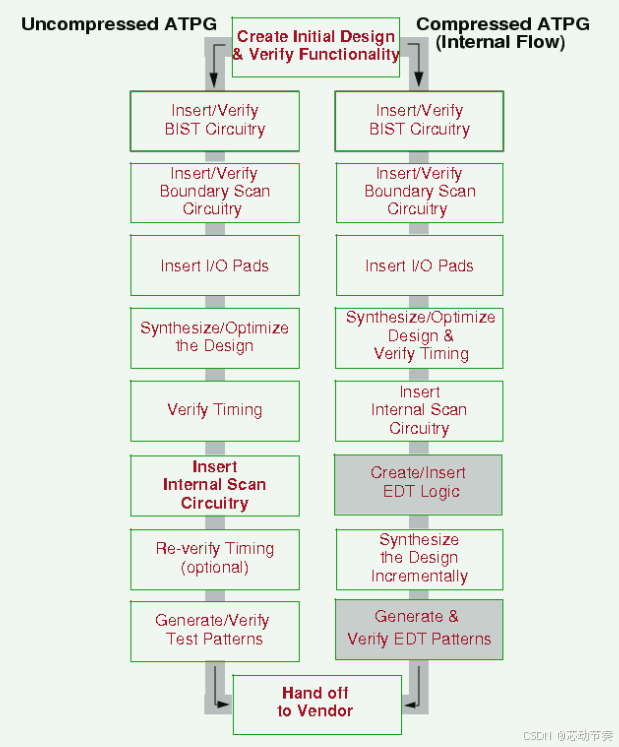

压缩模式下的pattern flow如下图所示(左图为外部模式,右图为内部模式)。相比与transition flow,设计上多出了edt 逻辑的插入,除此之外流程中自然也多除了针对edt 的pattern的verify动作。

第三回

第四回

第五回

第六回

第七回

第八回

因为近期先关注于edt的lowpower部分内容,因此就先跳跃式的先分享下关于DFT中的LOW-POWER设计。

第八回 第一话之 Low-Power test

EDT low-power逻辑贯穿于shift和capture cycle,同时也会EDT mode和bypass mode。只是shift cycle和capture cycle中lowpower(下面简称,LSP)作用方式有所差异:

- shift cycle

shift cycle的LP是基于:test pattern通常只包含一小部分特定于测试的位,其余的扫描单元或“不关心”位随机填充0和1;因此,只有少数几个扫描链具有指定的位。在低功耗运行过程中,没有任何指定位的扫描链单元使用0填充,以减少测试模式通过core时不必要的反转。 - capture cycle

相比而言,capture cycle是基于现有时钟门控设计。在这种情况下,控制设计的非目标部分的时钟门控将会被关闭,而控制目标部分的时钟gate会被打开。在采用时钟门,特别是多层时钟门(hierarchy,层次结构)来控制大多数元素状态的设计中,功率控制最为有效。capture阶段的低功耗配置只影响test pattern,并且在ATPG期间使用set_power_control命令来启用(这是一条十分重要的指令,后续会重点介绍)。

简单可以总结为:capture的低功耗是通过门控的方式实现的,而shift阶段的低功耗设计是通过scan chain中的扫描单元填充“0”实现。

下面分别分开讲解下shift和cature阶段的LP。

shift LP

这部分LP的启用可以分为两部分:

step1——低功耗逻辑的插入:

在Tessent工具中使用set_edt_power_controller 命令中的“-MIN_Switching_threshold_percentage”来添加低功耗逻辑。其实本质上dft的逻辑生成就是修改对应部分的DftSpecification,使用此命令和选项后会在对应的edt spec中生成对应的选项。这是一种“修改”spec的方法,还有一种是直接对spec进行操作——add_config_element和set_config_value搭配使用(后续讲)。

step2——生成带低功耗的pattern

当生成pattern时,必须使用set_power_control和set_edt_power_controller shift

命令启用电源控制器并指定扫描链移位期间使用的低功耗切换阈值。指定的开关阈值不应超过电源控制器硬件能力;支持超出范围的阈值,但会生成警告。

值得注意的是,这里的反转阈值,这里用变量s表示,有两个节点,共分为三个部分,分别为:

- s < 12%

- 12% < s < 24%

- s > 24%

阈值范围越小增加的LP逻辑量就相对应的越大。同时,切换阈值百分比代表的是shift期间整个扫描链翻转的百分比。然后,最小开关阈值百分比表示功率控制器硬件可以在低功耗应用中容纳的最小开关阈值,并确定测试向量生成可以使用的开关阈值百分比。如果指定的-MIN_Switching_threshold_percentage 落在其中一个范围内,则该工具

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1003

1003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?