数字电路时序分析

第一章 数字电路时序分析—建立保持时间

第二章 数字电路时序分析—时序路径

时序路径

时序路径是要进行时序分析的前提,想要进行时序分析,需要了解时序路径由那几部分组成

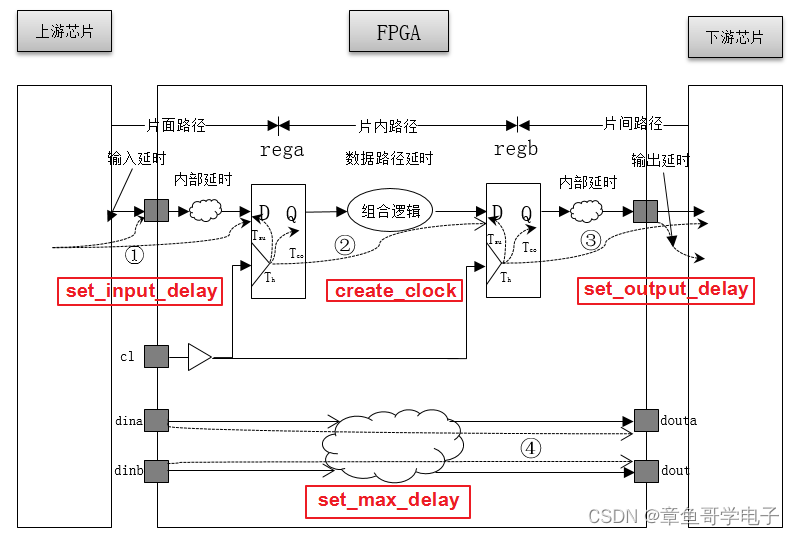

典型的时序路径有4类,如上图所示,这4类路径可分为片间路径(标记①和标记③)和片内路径(标记②和标记④)。

- 上游芯片到FPGA路径

- FPGA内部路径

- FPGA到下游芯片

- 上游芯片到下游芯片

我们一般只关注前三个。

1、上游芯片到FPGA路径

上游芯片到fpga的路径是输入端口到fpga第一集触发器的路径,在fpga中一般是使用set_input_delay进行约束。set_input_delay约束是约束时钟和数据的相位关系,相对延时多少,是边沿对齐还是中心对齐,是SDR单边沿信号还是DDR双边沿信号。

# Edge-Aligned Rising Edge Source Synchronous Inputs

# (Using a direct FF connection)

#

# For an edge-aligned Source Synchronous interface, the clock

# transition occurs at the same time as the data transitions.

# In this template, the clock is aligned with the beginning of the

# data. The constraints below rely on the default timing

# analysis (setup = 1 cycle, hold = 0 cycle).

#

# input __________ ________________

# clock |________________| |__________

# |

# skew_bre|skew_are

# <------>|<------>

# ________________ | ________________

# data XXX________________XXXXXXXXXXXXXXXXX____Rise_Data___XXX

#

本文介绍了数字电路中的时序分析概念,包括建立保持时间、时序路径等关键要素,并详细解析了上游芯片到FPGA、FPGA内部及FPGA到下游芯片的时序路径及其约束方法。

本文介绍了数字电路中的时序分析概念,包括建立保持时间、时序路径等关键要素,并详细解析了上游芯片到FPGA、FPGA内部及FPGA到下游芯片的时序路径及其约束方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1363

1363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?