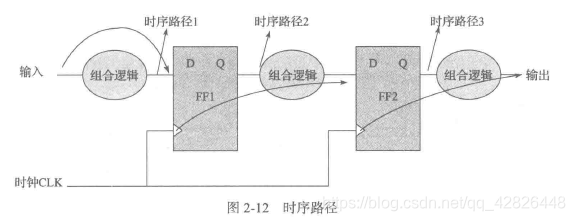

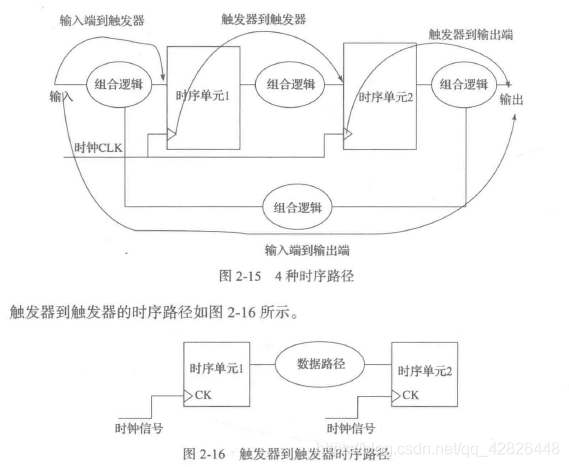

- 时序路径是指设计中数据信号传播过程中所经过的逻辑路径。每一条时序路径都存在与之对应的一个始发点和一个终止点。

- 时序分析中定义的始发点分为:组合逻辑单元的数据输入端口和时序单元的时钟输入端口。

- 时序分析中定义的终止点分为:组合逻辑单元的数据输出端口和时序单元的数据输入端口。

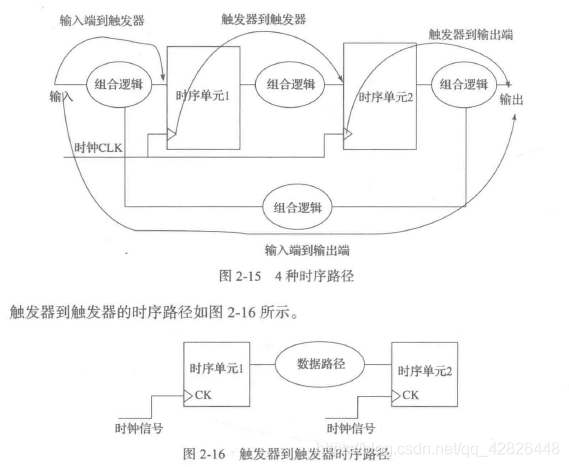

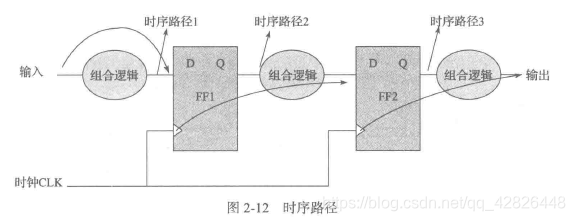

- 时序路径根据始发点和终止点的不同分为4种类型的时序路径:

时序路径(Timing path)简介

最新推荐文章于 2025-03-21 17:58:52 发布

836

836

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?