37、Mux256to1 4bit

Create a 4-bit wide, 256-to-1 multiplexer. The 256 4-bit inputs are all packed into a single 1024-bit input vector. sel=0 should select bits in[3:0], sel=1 selects bits in[7:4], sel=2 selects bits in[11:8], etc.

module top_module(

input [1023:0] in,

input [7:0] sel,

output [3:0] out );

assign out = {in[sel*4+3], in[sel*4+2], in[sel*4+1], in[sel*4+0]};

endmodule

/*

assign out = in[sel*4 +: 4];// 从 sel*4 开始,选择比特序号大于sel*4 的 4 位比特,相当于[sel*4+3:sel*4]

assign out = in[sel*4+3 -: 4]; // 从 sel*4+3 开始,选择比特序号小于 sel*4+3 的 4 位比特,相当于[sel*4+3:sel*4]

*/

38、半加器,无输入cin

module top_module(

input a, b,

output cout, sum );

assign {cout,sum} = a+b;

endmodule

39、全加器

module top_module(

input a, b, cin,

output cout, sum );

assign sum = a^b^cin;

assign cout = a&b|a&cin|b&cin;

//assign {cout,sum}=a + b + cin;

endmodule

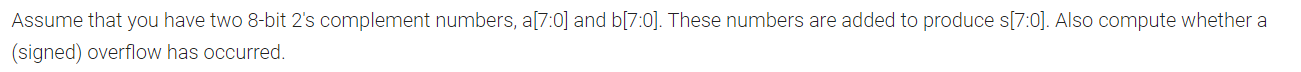

40、signed addition overflow

module top_module (

input [7:0] a,

input [7:0] b,

output [7:0] s,

output overflow

); //

assign s = a + b;

assign overflow = ( a[7] && b[7] && ~s[7] ) || (~a[7] && ~b[7] && s[7]);

//正数相加,符号位变为0,判断溢出……

endmodule

41、BCD加法器

module top_module(

input [15:0] a, b,

input cin,

output cout,

output [15:0] sum );

wire [3:0] cout_r;

//例化4次,注意前一次计算的cout为后一次计算的cin

bcd_fadd inst1_bcd_fadd(

.a(a[3:0]),

.b(b[3:0]),

.cin(cin),

.cout(cout_r[0]),

.sum(sum[3:0])

);

bcd_fadd inst2_bcd_fadd(

.a(a[7:4]),

.b(b[7:4]),

.cin(cout_r[0]),

.cout(cout_r[1]),

.sum(sum[7:4])

);

bcd_fadd inst3_bcd_fadd(

.a(a[11:8]),

.b(b[11:8]),

.cin(cout_r[1]),

.cout(cout_r[2]),

.sum(sum[11:8])

);

bcd_fadd inst4_bcd_fadd(

.a(a[15:12]),

.b(b[15:12]),

.cin(cout_r[2]),

.cout(cout_r[3]),

.sum(sum[15:12])

);

assign cout = cout_r[3];

endmodule

42、卡诺图1

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = ~a&~c&~d | ~b&~c | ~a&~d | b&c&d |a&~b&d;

endmodule

43、

module top_module (

input c,

input d,

output [3:0] mux_in

);

assign mux_in = {(c&d),(~d),1'b0, (c|d)};

endmodule

1196

1196

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?