ICG

在做综合时,往往会遇到很多ICG的timing问题(主要指的是setup),在后期CTS后,ICG由于天然的skew差,也很容易出现setup问题,这篇文章主要对综合时ICG的timing优化做分析!

ICG相关概念

CLOCK GATE Direct Fanout

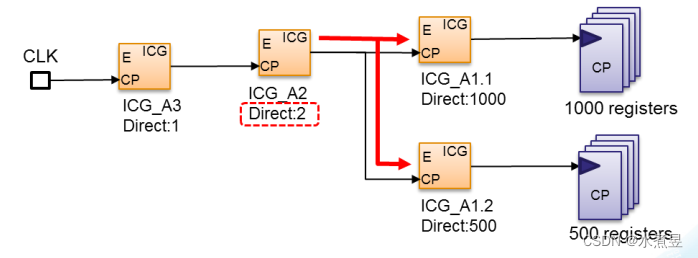

首先是clock gate direct fanout的概念,具体可以看下图

这里的direct fanout指的是由这个ICG直接drive的sequential cell(不能穿过ICG),所以这里ICG A2的direct fanout为2,而ICG A1.1的direct fanout则为1000;

CLOCK GATE Transitive Fanout

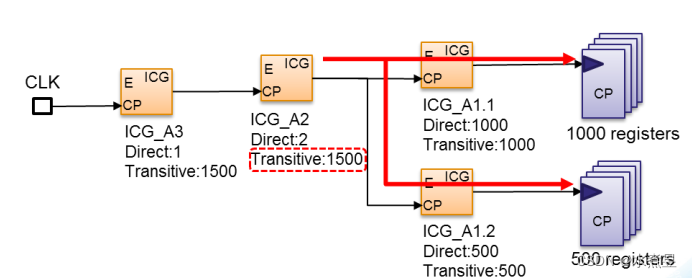

下面是clock gate transitive fanout的概念,具体可以看下图

与direct fanout不同的是,transitive fanout可以穿过ICG,其数量为该ICG去drive的leaf registers以及memory的和;

这里ICG

本文探讨了在综合过程中ICG(时钟门控)的时序优化问题,特别是setup问题。介绍了CLOCK GATE Direct Fanout和Transitive Fanout的概念,并详细说明了如何通过这两个概念来设置clock gate latency,以解决Post CTS后的skew问题,从而优化ICG的时序。文章提到了针对不同stage和fanout类型设置延迟的方法及其局限性。

本文探讨了在综合过程中ICG(时钟门控)的时序优化问题,特别是setup问题。介绍了CLOCK GATE Direct Fanout和Transitive Fanout的概念,并详细说明了如何通过这两个概念来设置clock gate latency,以解决Post CTS后的skew问题,从而优化ICG的时序。文章提到了针对不同stage和fanout类型设置延迟的方法及其局限性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8223

8223

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?