随着科技日新月异的发展,芯片工艺的进步始终是信息技术领域的重要推动力。近期,TSMC台积电发布的1.6nm(TSMC A16TM)半导体工艺,以其创新的纳米片晶体管结构与背侧电源轨解决方案,再次刷新了业界对先进制程技术的认知。

回顾芯片工艺发展历程:

-

微米时代(早期至1990年代初):芯片工艺起始于微米级别,如早期的10微米、1微米等。此阶段,主要通过缩小晶体管尺寸、增加集成度来提升芯片性能,但工艺进步相对缓慢。

-

深亚微米时代(1990年代初至21世纪初):进入90年代,工艺节点迅速跨越至0..png">5微米、0.25微米、0.18微米等,标志着深亚微米时代的到来。这一时期,集成电路设计与制造技术取得重大突破,包括引入铜互连、低介电常数材料等,显著提升了芯片速度和功耗效率。

-

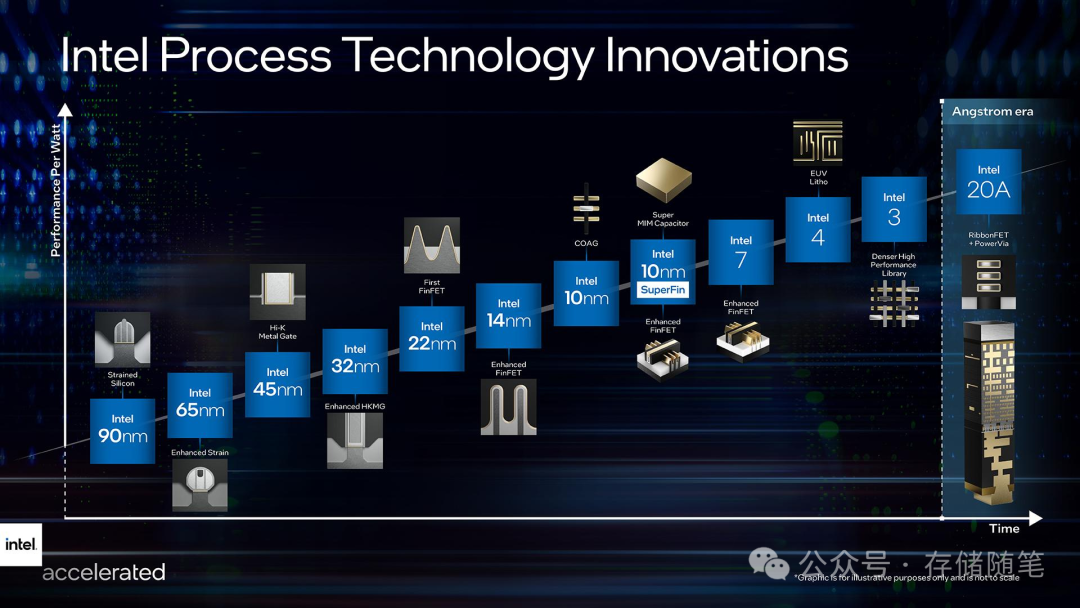

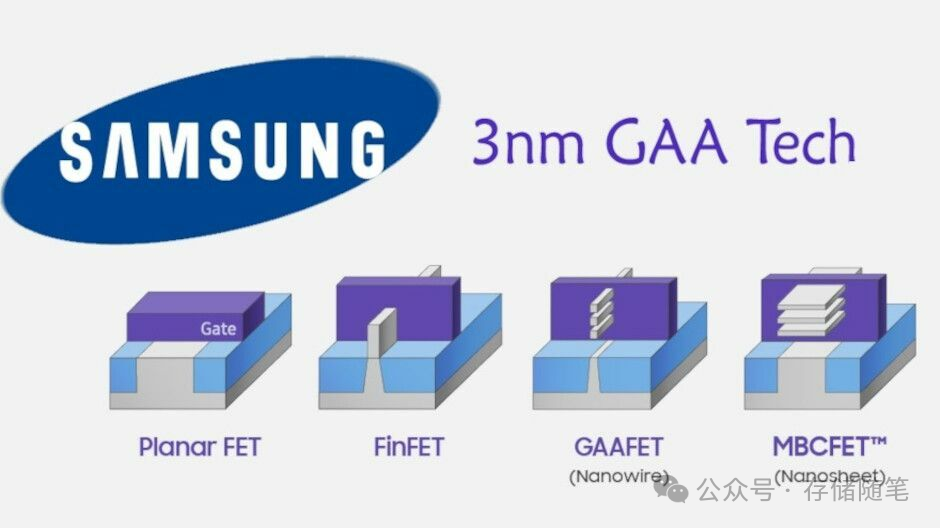

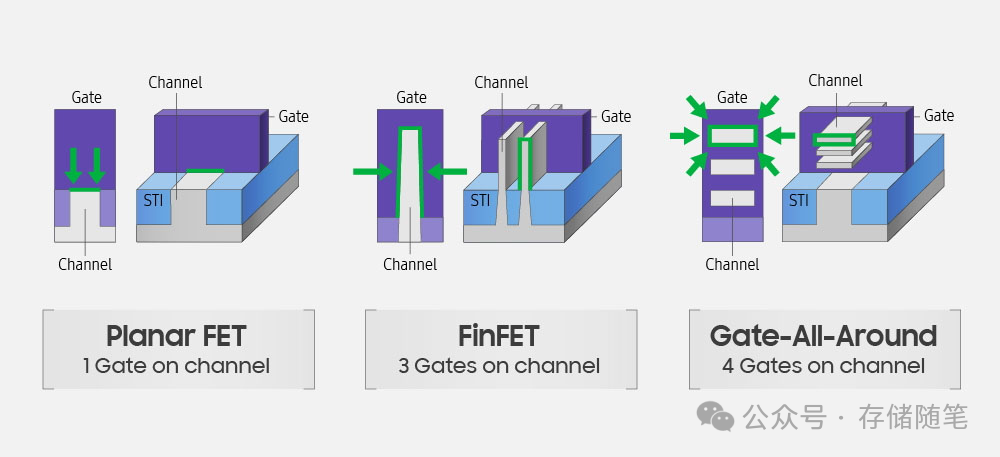

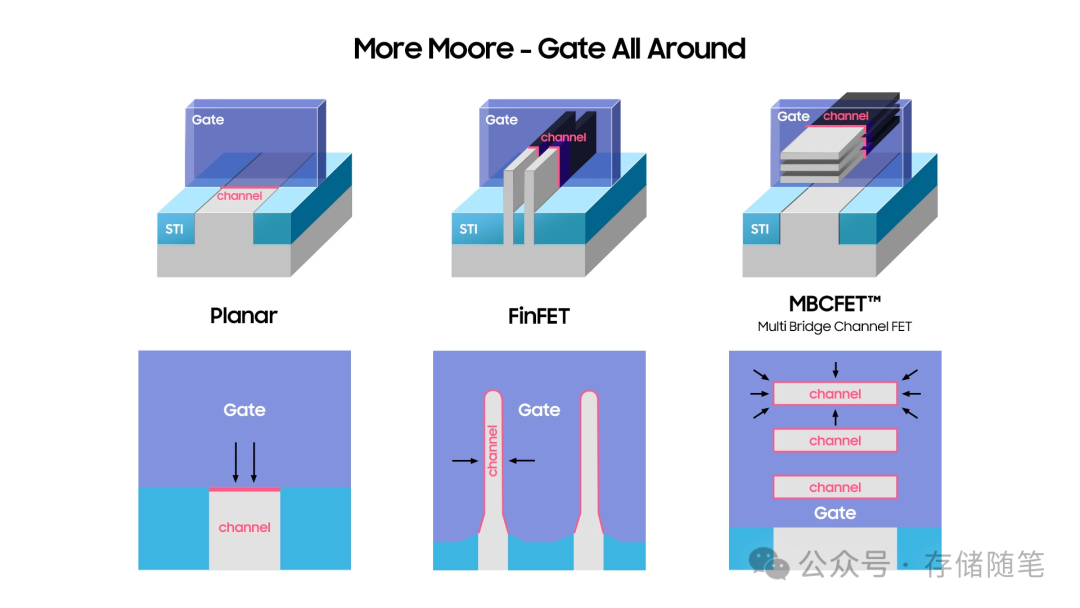

纳米时代(21世纪初至今):21世纪以来,芯片工艺进入了纳米级别,从90纳米、65纳米逐步推进至当前的1.6纳米。随着节点尺寸的持续缩小,业界面临诸多物理极限挑战,如漏电流、量子隧穿效应等。为克服这些难题,技术革新不断涌现,如高K金属栅极、FinFET(鳍式场效应晶体管)、GAA(环绕栅极场效应晶体管,如TSMC A16TM所采用的纳米片晶体管)等新型晶体管结构,以及先进的封装技术如3D IC、Chiplet等,实现了芯片性能、功耗、面积等方面的持续优化。

7纳米工艺节点标志着半导体行业进入深度纳米时代,晶体管结构开始向FinFET(鳍式场效应晶体管)过渡。台积电(TSMC)于2018年率先实现7纳米工艺的商业化量产,其后的三星电子紧随其后。这一节点的突破不仅带来了晶体管密度的大幅提升(约每平方毫米集成1亿个晶体管),还显著改善了功耗与性能比。7纳米工艺被广泛应用于高端智能手机、数据中心服务器、人工智能硬件等,成为当时尖端技术的象征。

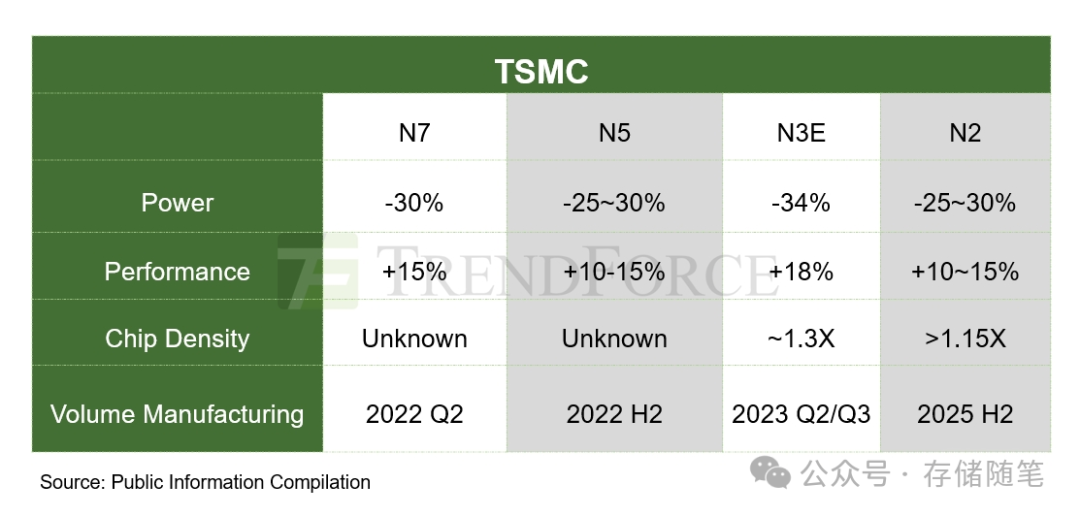

随着摩尔定律的持续推进,芯片制造商们在短短几年内便跨越了7纳米,迈向了更先进的5纳米节点。2020年,TSMC再次领先,推出了全球首个商用5纳米工艺,苹果A14芯片成为其首批使用者。5纳米工艺不仅延续了晶体管密度的翻倍增长(每平方毫米集成约1.7亿个晶体管),而且通过更精细的设计规则、更先进的材料与设备,进一步降低了漏电、提高了频率,为高性能计算、移动设备和AI芯片等领域带来了前所未有的性能飞跃。

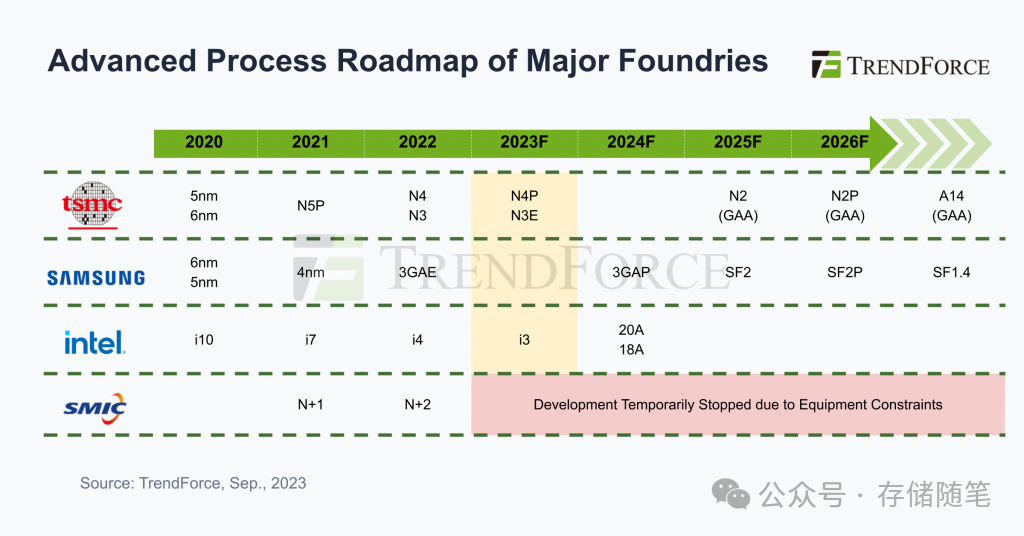

在当今高速发展的科技时代,芯片工艺的重要性不言而喻。芯片制造技术不断突破,使得电子产品性能更高、功能更强大,同时也推动了整个科技行业的快速发展。三星、台积电和英特尔三大芯片制造巨头的工艺技术相互卷起来了。

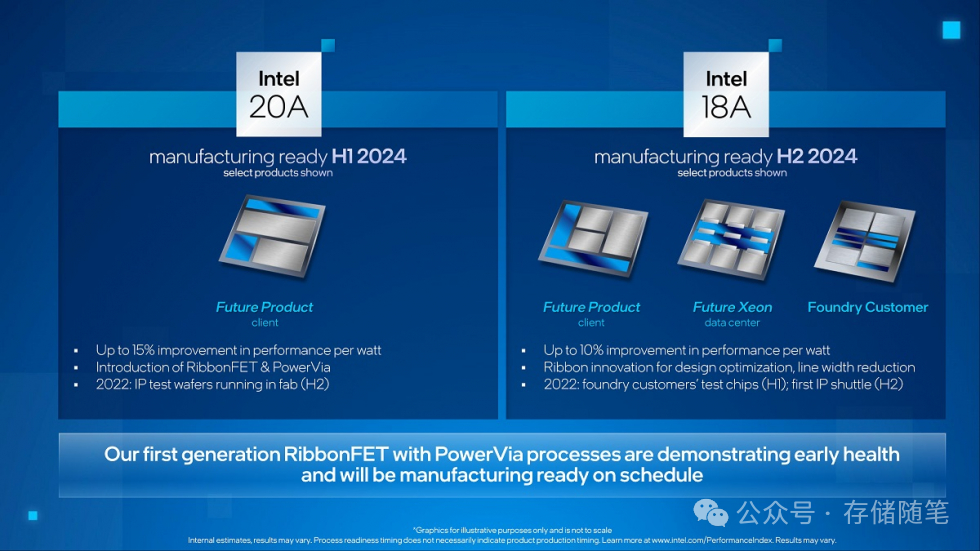

英特尔未来几年的主要目标之一是在技术领先方面击败台积电,并从需要前沿节点的公司那里获得代工订单。为此,英特尔计划在未来五个季度内引入三种先进的制造工艺,并在2024年下半年至2025年上半年开始量产其2nm和1.8nm制造技术。但台积电认为,即使其将于2025年使用的N3P节点在价格上也将提供与英特尔18A相当的PPA,而其N2将击败它,尽管晚一年进入市场。

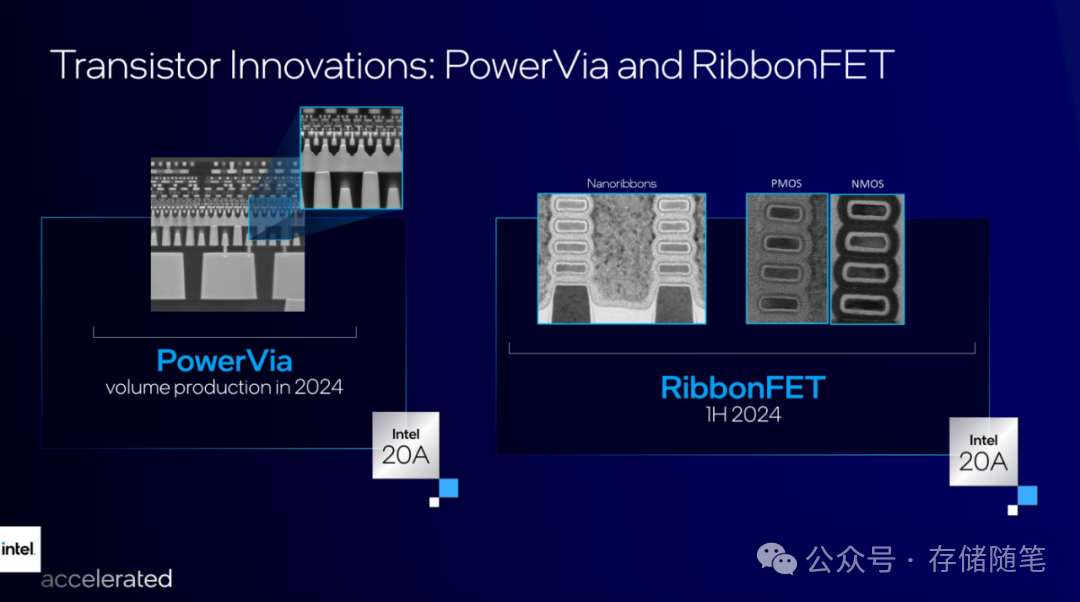

英特尔的20A(2nm节点)制造技术将于2024年推出,有望在创新方面取得突破,因为它将引入RibbonFET全栅极晶体管和背面功率传输网络(BSPDN),这两种技术旨在实现更高的性能、更低的功耗和更高的晶体管密度。

与此同时,英特尔的18A生产节点旨在进一步改进20A的创新,并在2024年底至2025年初进一步改善PPA。

英特尔的下一代Meteor Lake芯片是第一个使用“英特尔4”节点的芯片,目前正在按计划生产,并计划于今年晚些时候推出。这些将是该公司首批使用基于小芯片的架构的高产量消费类芯片,该架构使用3D Foveros互连技术将多个小芯片连接在一起。

英特尔下一代Arrow Lake芯片采用相同的设计方法,并使用更新一代的英特尔20A工艺节点,该节点具有许多新的功能,可以使英特尔在晶体管技术方面领先于台积电。

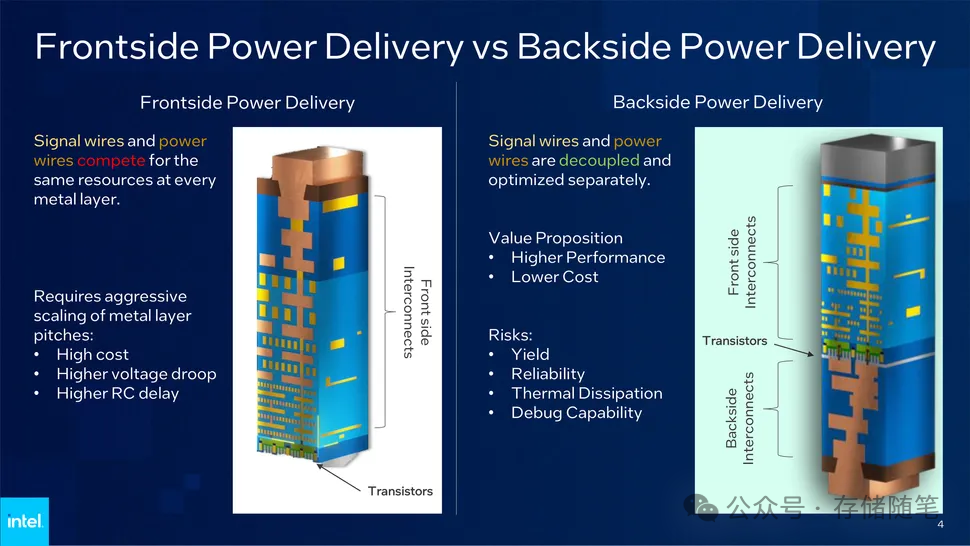

Arrow Lake将是英特尔第一个使用英特尔20A节点(2纳米)的产品,该节点包括PowerVia背侧电源传输等新的创新。这种技术将晶体管的全部电源直接通过晶体管的背面路由,同时将数据传输互连保持在传统的另一侧位置,从而将电源传输分区到晶体管的背面。

这种方法产生了一系列优势,包括能够实现更密集的晶体管阵列、改善电压下垂特性以解锁更高的频率、同时允许更快的晶体管开关速度,同时能够在芯片顶部实现更密集的信号路由。信号传输也因此受益,因为简化路由能够实现更快的导线并降低阻抗和电容。

英特尔将在2024年引领业界首款批量生产的具有背侧电源传输的芯片。台积电要到2026年才会整合这项技术。

尽管英特尔的20A(2纳米级)和18A(1.8纳米级)制造技术将比台积电的可比制造工艺早推出,但台积电却不服气,称其N3P(3纳米级)技术将提供与英特尔18A相当的特性,而其N2(2纳米级)将在功率、性能、面积(PPA)优势方面全面超越它。

台积电首席执行官魏哲家在公司财报电话会议上表示:我们的2nm技术没有背面供电(N2)比N3P和18A更先进,并将在2025年推出时成为半导体行业最先进的技术。”

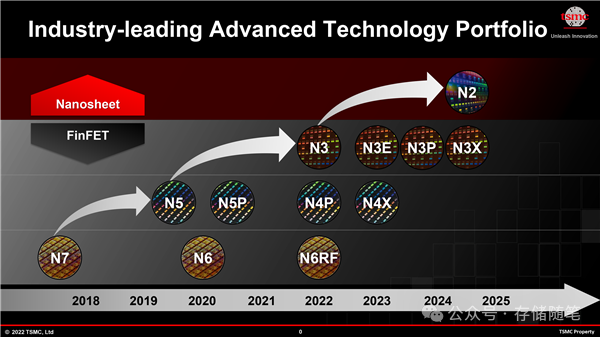

相比之下,台积电的3nm级的N3、N3E、N3P和N3X制造工艺都依赖于成熟的FinFET晶体管和传统电源传输网络。这家全球最大的代工厂似乎并不急于采用纳米片GAA晶体管和BSPDN,因此前者将在台积电的N2节点上引入,预计在2025年下半年进入量产,而后者将添加到N2P中,预计在2026年底开始量产。

台积电的N3、N3E、N3P和N3X,以及N2和N2P等工艺各有不同的优势。

-

N3和N3E:这两款工艺都是台积电的3nm工艺家族中的基础版本。其中,N3在相同频率下降低32%的功耗,或是在相同功耗下提高18%的性能。而N3E相比较现阶段的台积电5nm工艺,可在相同频率下降低32%的功耗,或在相同功耗下提高18%的性能。

-

N3P:这款工艺在同漏电下性能提升接近5%,并且还有密度提升,即2%的光学缩小,结果是芯片密度提升4%。它在同功耗的情况下比N3E提升5%的性能。

-

N3X:这款工艺是专门为高性能计算设备设计的。它相比N3P在驱动电压为1.2V的情况下速度提高了5%,并且芯片密度与N3P相同。

-

N2:这款工艺性能提升10-15%,芯片密度提升大于15%。预计在2025年量产。

-

N2P:这款工艺引入了backside power delivery,可能会是历代P提升比较大的一代。预计在2026年量产。

在制程技术上,三星的4nm工艺已经与台积电的工艺相当,而且公司有信心很快就会超过台积电的4nm产能。此外,三星在提高4nm芯片产量方面取得的稳步进展,可能会为该公司赢得高通(Qualcomm)和英伟达(NVIDIA)等重要客户的新订单。

同时,三星也在致力于改进其4nm芯片制造工艺,并已取得重大进展。据Sammobile和9to5google的数据显示,三星的4nm工艺现在已经与台积电的工艺相当,而且该公司有信心很快就会超过台积电的4nm产能。

三星的3纳米制程工艺已经成功为一家客户代工芯片,良品率达到了60%。然而,三星在3nm遇到了一些困难,其3nm GAA工艺尚未实现量产。据说,三星已经向中国客户交付了第一批3nm GAA芯片,但这些芯片并不完整,只是逻辑芯片中的SRAM。而且,三星的完整的3纳米GAA晶圆比较难生产,良率只有50%。

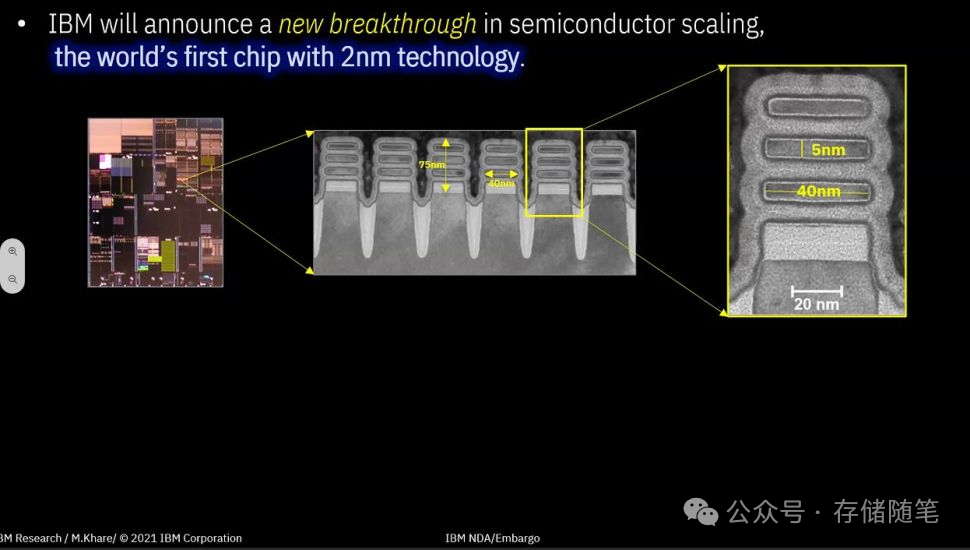

根据三星官方公布的信息,公司已经在2nm工艺方面取得了进展,并计划在2026年量产该工艺。具体的工艺指标还未公布,只知道还是GAA晶体管,跟3nm一样基于MBCFET(多桥沟道FET)技术,这是一种纳米片晶体管,可以垂直堆叠,而且兼容现在的CMOS工艺,降低新技术的升级成本。同时,三星也参与了IBM的2nm技术研发,但量产的2nm技术跟IBM的2nm并不一样,后者需要新的生产方法,而三星还会依赖自家研发的2nm技术。

据英国《金融时报》报道,高通打算将其下一代高端移动芯片的生产从台积电转移到三星的2nm工艺。三星提供大幅折扣,正在积极寻求英伟达等主要参与者的订单,对台积电的主导地位构成挑战。

据援引内幕消息的报道,台积电已向苹果和英伟达等主要客户展示了其2nm原型测试结果。此外,消息人士表示,三星不仅计划推出其 2nm 原型,而且还提供折扣价,吸引了包括 NVIDIA 在内的知名客户的兴趣。

该报告强调,高通正计划将三星的“SF2”(2nm)工艺用于下一代高端智能手机芯片。三星作为去年全球第一家大规模生产 3nm (SF3) 芯片的公司,也是采用新型全环绕栅极 (GAA) 晶体管架构的先驱。

三星表示,“我们已经全面部署,可以在2025年大规模生产SF2。由于我们是第一家进入并改造GAA架构的公司,我们希望从SF3到SF2的进展会比较顺利。

不过,业内人士透露,三星最基础的3nm芯片良率仅为60%,远低于客户预期。此外,当生产复杂度相当于苹果 A17 Pro 或 NVIDIA 图形处理单元 (GPU) 的芯片时,良率可能会进一步下降。

高通(Qualcomm)和英伟达(NVIDIA)等全球巨头遵循多元化的晶圆代工战略,但目前仍严重依赖台积电。此前,英伟达首席财务官科莱特·克雷斯(Colette Kress)在瑞银全球技术大会上暗示,英伟达可能会考虑让英特尔生产其下一代芯片,这可能会脱离与台积电在AI芯片方面的独家合作关系。

现在,高通也在探索与三星在2nm工艺方面的合作,这加剧了台积电的压力,以解决先进半导体制造领域两家主要客户的潜在订单损失。

另一方面,台积电向英国《金融时报》表示,其2nm工艺的开发进展进展顺利,计划于2025年投产。推出后,它将在密度和能效方面代表业界最先进的半导体技术。

在之前的投资者会议上,台积电表示,客户对高速计算和智能手机应用的 2nm 非常感兴趣和参与。预计2nm在2025年推出时,将是业界最先进的半导体技术,可与同阶段的3nm相媲美甚至优于3nm。

台积电计划于2025年下半年推出2nm背面电源轨解决方案,计划于2026年量产。

除了台积电和三星积极向2nm和更先进的工艺迈进外,英特尔也加入了竞争。英国《金融时报》将这场2nm工艺竞赛描述为“塑造一个价值5000亿美元的行业的未来”。

英特尔正沿着其先前设定的 5 个工艺节点在四年的轨迹中取得进展。英特尔 4 工艺已准备好进行大规模生产,英特尔 3 工艺计划于今年晚些时候推出。英特尔首席执行官帕特·基辛格(Pat Gelsinger)此前曾展示过英特尔20A晶圆,预计将于明年上半年进入预生产阶段。英特尔 18A 工艺计划于 2024 年下半年量产。

3890

3890

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?