搭建基于Modelsim的自动化仿真

我们之前通常进行Modelsim界面操作,这样会很费时很麻烦。这里我们介绍一种快捷的方法,通过do文件快速搭建仿真环境,实现更高效的仿真过程。

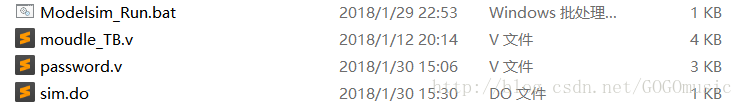

我们只需将sim.do中的代码写好,然后点击一下modelsim_run.bat文件,即可完成所有仿真过程。

批处理文件modelsim_run.bat

只需要双击批处理文件modelsim_run.bat,就可以自动调用Modelsim,并自动完成对Testbench和待验证设计文件的编译和仿真,并且可以自动将要观察的信号添加到wave窗口。完全自动化!!

批处理文件包含一条命令:

modelsim -do sim.do这是一条DOS命令,意思就是调用Modelsim工具,并在Modelsim工具中执行sim.do这个文件。

do文件

sim.do文件是由tcl脚本语言编写的

##create work library

vlib work

vlog "../src/*.v"

vsim -voptargs=+acc work.moudle_TB

# Set the window types

view wave

view structure

view signals

add wave -divider {moudle_TB}

add wave moudle_TB/*

.main clear

run 320usvlib work:建立work库,相当于新建工程时所生成的work库,后期我们编译的结果信息存放到work库中。

vlog “../src/ * .v”:vlog相当于modelsim工具中的compile,”../src/ * .v”表示编译/src路径下所有的verilog文件。

vsim -voptargs=+acc work moudle_TB :vsim表示启动仿真功能,仿真文件为moudle_TB 。

add wave -divider {moudle_TB} :将moudle_TB所有信号线 划线隔开

add wave moudle_TB/* : 将顶层文件moudle_TB中左右的信号线加到仿真波形窗口

.main clear :清除Transcript窗口

run 320us :运行时间320us

2795

2795

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?