提高工作频率的本质

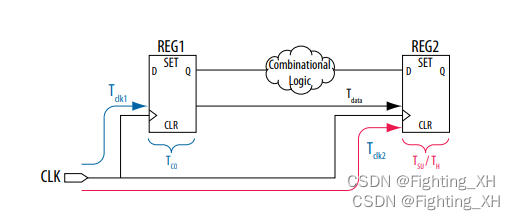

提高工作频率的本质就是减少寄存器到寄存器的时延,简言之,降低各种延时

电路延迟

-

电路延迟主要包括三个:

寄存器延迟Tco(时延是由器件物理特性决定)、走线延迟和组合逻辑延迟。 -

走线延迟:

1、加入时钟约束(一般以加5%裕量较为合适)

2、将相关的逻辑的布线时尽量靠近,从而减少走线时延。 -

组合逻辑延迟:

1、切割组合逻辑,减少LUT级联,当输出判断条件大于四个输入的话,一般采用多LUT级联的方式,那么就会引入更多的延迟,因此我们要尽可能减少输入条件,从而级联LUT也减少。切割组合逻辑常采用流水线技术,通过各级之间插入寄存器来实现,从而各级之间的组合逻辑减少。

2、将计数器移除FSM。当我们在进行状态机设计的时候,有时也会将计数器作为判断条件,但是输入常为四输入,而计数器数值较大,比如

订阅专栏 解锁全文

订阅专栏 解锁全文

2611

2611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?