AXI4协议基于猝发式传输机制。在地址通道上,每个交易有地址和控制信息,这些信息描述了需要传输的数据性质。主从设备间的数据传输有两种情况,一种是主设备经过写通道向从设备写数据(简称写交易),另一种是主设备经过读通道从从设备那里读取数据(简称读交易)。在写交易过程中,AXI有一个额外的写响应通道,从设备通过该通道向主设备发出信号表示完成写交易。

AXI 协议可以实现:

- 地址信息发出先于实际传输的数据

- 支持多个未完成的交易

- 支持乱序交易

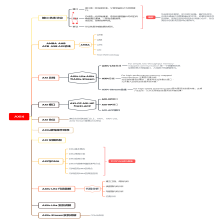

图4‑13展示了使用读地址和读数据通道如何实现读交易。

图4‑13 读通道结构

图4‑14描述了使用写地址、写数据和写响应通道如何实现一次写交易。

AXI4协议采用猝发式传输,包括地址、读、写和写响应通道。地址通道传递交易信息,读通道用于从设备到主设备的数据传输,写通道则相反。写响应通道提供从设备对写交易的确认。每个通道通过VALID和READY信号进行数据传输的握手,支持可变长度猝发、原子操作等特性。通道之间关系灵活,允许不同步的数据传输。

AXI4协议采用猝发式传输,包括地址、读、写和写响应通道。地址通道传递交易信息,读通道用于从设备到主设备的数据传输,写通道则相反。写响应通道提供从设备对写交易的确认。每个通道通过VALID和READY信号进行数据传输的握手,支持可变长度猝发、原子操作等特性。通道之间关系灵活,允许不同步的数据传输。

订阅专栏 解锁全文

订阅专栏 解锁全文

1023

1023

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?