项目:基于FPGA的视频转换功能

外设:DDR3

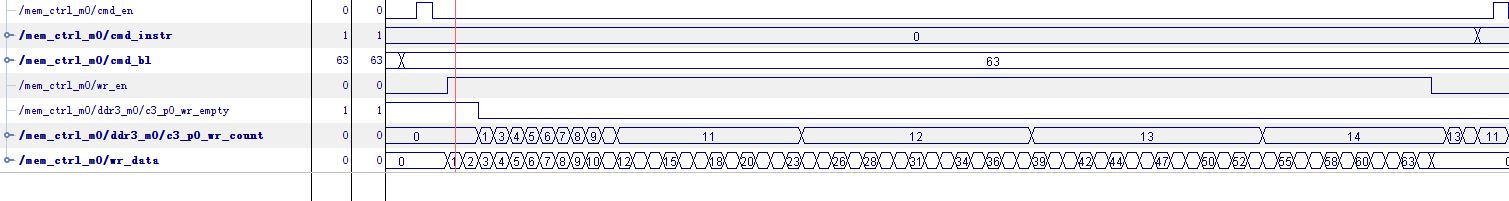

描述:在调试DDR3时,按照时序要求,向地址0写入64个数据,数据位宽为64bits,发现DDR3内部计数器wr_count不 是连续计数到64,以为是自己操作存在问题,查询官方资料,发现这样的情况不存在问题,解释大致意思是: ISP生成的IP有一个时钟,用户对DDR3写操作时也有一个时钟,其实就是FIFO的读写控制,因为两个时钟是异 步的,所以存在差异,这里的wr_count表示用户写入数据与IP内部读取数据 的差值。这个数值从-2到+64 变化都是正常的。实际操作时波形如图一所示。

图一 DDR3写操作wr_count计数过程

参考:http://china.xilinx.com/support/answers/44267.html

5726

5726

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?