一、概述

在前面的文章中,我们基本聊完了DDR的原理,对于DDR操作的基本结构和如何看懂一本DDR的手册。在此基础上,我们将进入最核心的部分,如何在FPGA去使用DDR,这里采用的DDR为DDR4系列,具体型号为MT40A1G16WBU-083E。

需要特别说明的是,由于我手头使用的板子是UltraScale系列的,所以IP核的使用方式与普通7系列的会有所不同,但是基本的原理还是相同的,关于7系列的使用,后续有时间也会进行更新。

二、IP 配置

2.1 打开IP核设置

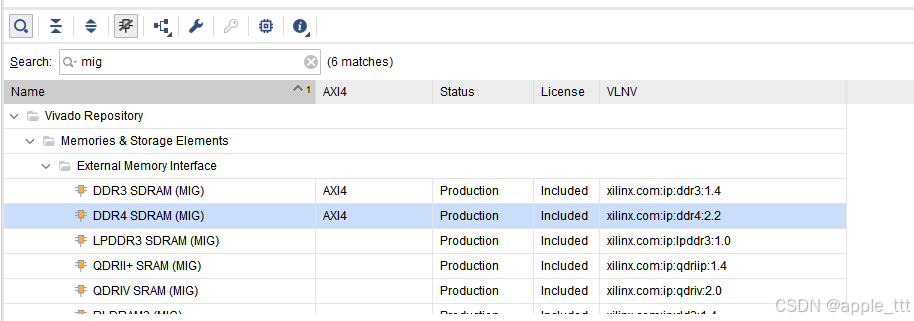

在IP catalog搜索MIG,就能找到我们需要的MIG IP核,这里由于使用的是UltraScale系列,所以IP搜索的结果与普通7系列就已经有所不同。我们选择本文中需要的DDR4系列。

2.2 Basic 配置

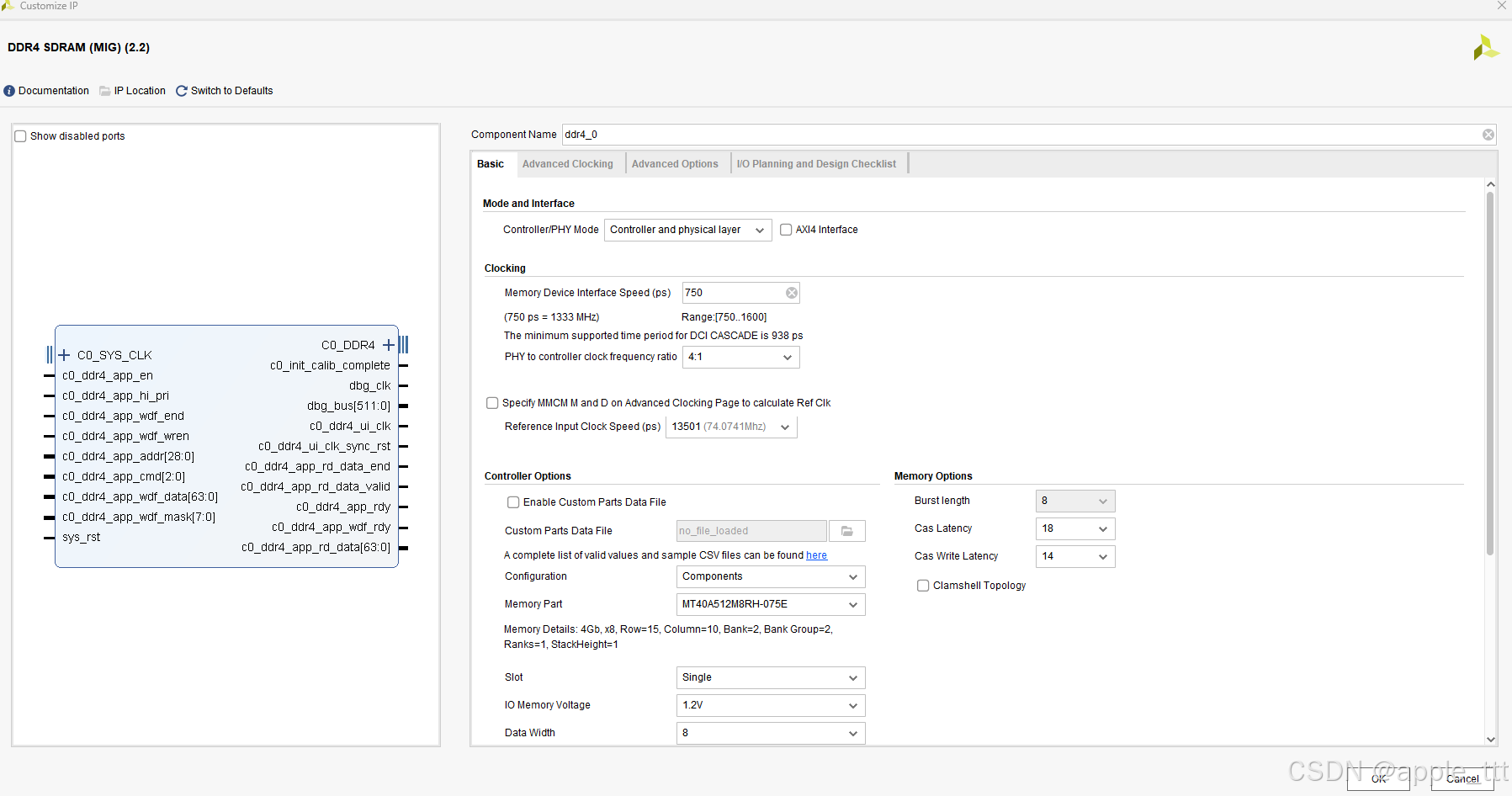

在打开IP核的配置界面后,我们可以看到有几个配置界面需要我们一一定制,我们首先从第一页的Basic界面开始。

2.2.1 Mode and Interface

这部分选择的是模式和接口类型,在之前的文章中我们提到过,对于xilinx提供的MIG DDR解决方案中,可选的接口分为以下的三种:

- User Interface

- AXI4 Slave Interface

- PHY Only Interface

一种是普通的用户接口,一种是AXI4 协议封装的接口,最后一种是不带有DDRC(DDR 控制器),只包含DDRPHY的物理接口,这里我们显然不会希望自己去开发DDRC,因此我们就选择最普通的Controller and physical layer 类型,旁边的AXI4 Interface我们也暂时不做选择,关于AXI4 接口的DDR使用,后面有机会会单独写文章进行讨论。

2.2.2 Clocking

在时钟配置中,我们需要设置内存设备接口的速度。我们选择的接口速度会自动影响可用的参考输入时钟速度。首先是Memory Device Interface Speed的选择,这里应该填写的是我们使用的DDR芯片的速率,这部分信息来源于DDR的Datasheet,关于如何阅读Datasheet,可以参考:

从零开始讲DDR(5)——读懂Datasheet![]() https://ztzhang.blog.csdn.net/article/details/142444632

https://ztzhang.blog.csdn.net/article/details/142444632

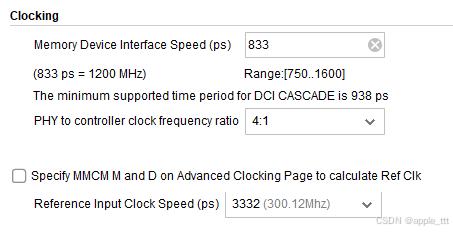

这里我们从手册中获知,我们所使用的这块DDR4的时钟频率为1200MHZ,接口速率为0.833ns,所以这里填写833(ps)。

接下来是PHY to controller clock frequency ratio的选择,其实在填完上面的833p后,我在这里就已经无法进行选择了,只有4:1一个选项,这里还是解释一下其原理。

在DDR3或DDR4 SDRAM的实现中,PHY时钟频率通常是控制器时钟频率的倍数。控制器的时钟频率决定了内存接口的操作速率,PHY时钟则是该频率的倍数,用于满足DDR3/DDR4内存协议的要求。通常情况下,PHY时钟频率是控制器时钟频率的2倍或者4倍。

这一般取决于以下因素:

- 使用的DDR所支持的最大IO时钟频率

- 使用的FPGA所支持的 memory interface 频率

这里在我们已经设置DDR侧(PHY侧)的时钟频率为1200MHZ的情况下,PHY to controller clock frequency ratio为4:1意味着我们的控制侧时钟输入为300MHZ时钟。

接下来会有一个Specify MMCM M and D on Advanced Clocking Page to calculate Ref Clk的选择,这个是让我们选择是否根据已有信息来反推输入的参考时钟频率。这里首先解释一下参考时钟:参考时钟(Reference Clock) 是指用于驱动和同步其他时钟信号的基础时钟信号。在 FPGA 设计中,参考时钟是一个稳定的输入时钟,它作为其他时钟源的基准,以确保设计中的时钟域一致性和同步性。在 FPGA 中,参考时钟常常用于时钟管理单元(例如 MMCM、PLL)来生成系统所需的各种时钟信号。这些单元会通过调整输入时钟的频率、相位等,产生多个不同频率的时钟信号,用于不同的模块和接口。例如,DDR3 或 DDR4 内存接口通常需要一个高速时钟来进行数据传输,而参考时钟则提供了一个稳定的基础时钟,经过 MMCM 或 PLL 后生成所需的时钟频率。

由于MIG ip是一个复杂的IP核,内部会使用到很多不同的时钟频率,内部会例化MMCM来生成所需的时钟,而用户需要从外部给定一个参考时钟来供MMCM使用。

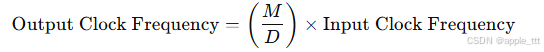

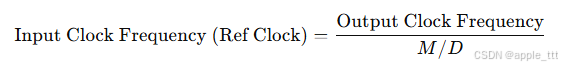

在Vivado中配置混合模式时钟管理器(MMCM)时,M 和 D 是影响时钟频率和参考时钟(Ref Clock)计算的两个重要参数。这两个参数用于计算输出时钟频率,并确保整个时钟结构的正确配置。以下是如何通过MMCM的 M 和 D 参数来计算参考时钟(Ref Clock):

- M (Multiply Factor):这是 MMCM 时钟输出的乘法因子,用于调整时钟的频率。

- D (Divide Factor):这是 MMCM 时钟输入的除法因子,用于调整输入时钟的频率。

在使用 MMCM 时,M 和 D 参数决定了时钟的频率关系。通过这些参数,我们可以确定参考时钟(Ref Clock)和 MMCM 输出时钟之间的关系。

公式如下:

因此,如果我们已知目标输出时钟频率,并且希望反推出参考时钟频率,公式可以重排为:

这里我们可以勾选,勾选后下面的参考时钟频率会直接固定成300.12Mhz。我们也可以不勾选,自己手动选择合适的参考时钟频率。

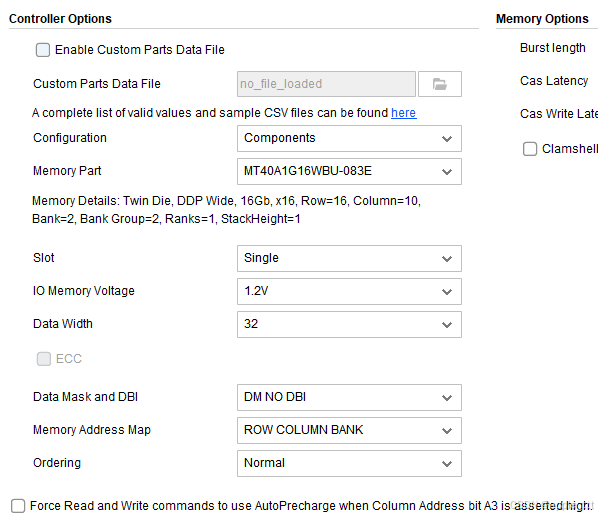

2.2.3 Controller Options

首先我们需要选择是否“Enable Custom Parts Data File”。Vivado 默认提供的 DDR3/DDR4 SDRAM 部件库并不能涵盖所有可能的内存部件。如果我们的设计需要使用不在默认部件库中的内存部件,我们就可以通过创建自定义部件的 CSV 文件来导入这些部件信息。CSV 文件用于描述这些自定义内存部件的特性(如大小、时序、速度、引脚配置等)。一旦上传了这个文件,Vivado 将能够识别并使用这些自定义部件。当我们有这方面的需求时,我们就需要勾选“Enable Custom Parts Data File”并在下面的文件栏导入所需的文件。在这里,我们使用的DDR可以在Vivado提供的部件库中找到,因为,我们不需要进行勾选。

下面是Configure的选择,一般没有特殊需求,我们就选择默认的Components,然后是选择自己所用的DDR型号。之后进行Slot和接口电压的选择, 都来源于所选型号,然后是数据位宽的配置。这里我们选择32bit,不启用ECC模式。这样配合后面我们需要在Memory Options里面设置的Burst Length为8,就可以实现一次32*8=256bit位宽数据的传输。

接下来是Data Mask(DM)和 DBI(Data Bus Inversion)的选择。

| 特性 | Data Mask (DM) | Data Bus Inversion (DBI) |

| 作用 | 屏蔽某些数据位,减少不必要的写操作 | 反转数据位以减少功耗和信号干扰 |

| 应用场景 | 主要在写操作时使用,选择性屏蔽特定字节的数据 | 在数据传输过程中优化信号质量和功耗 |

| 功能实现 | 用掩蔽位指示哪些字节数据不被写入内存 | 反转数据位使高低电平数量平衡,降低功耗和电磁干扰 |

| 数据传输效果 | 提高内存带宽的利用效率 | 降低高速数据传输中的功耗和电磁干扰 |

在 DDR3/DDR4 内存中,数据总线通常是 64 位宽,而 DM 信号的位数与数据总线的位数相同。每一个 DM 信号的位都对应数据总线上的一个字节(通常是 8 位)。如果 DM 信号的某一位被置为“1”,表示对应的数据字节不被写入。如果 DM 信号的某一位被置为“0”,则表示对应的数据字节将被写入内存。举例:如果 DDR 内存总线是 64 位宽并且 DM 信号也有 8 位,那么每个 DM 位控制一个字节的写入。如果某个 DM 位被设置为 1,表示该字节的数据在写入时会被屏蔽。

DBI 技术的关键是:如果传输的数据中逻辑 1 的个数多于逻辑 0 的个数,则将所有数据位反转;反之,则不反转数据位。换句话说,只有在反转后能够使数据传输中的高电平和低电平的数量更加平衡时,DBI 才会启用。举例:如果在某个时钟周期内,数据总线上的数据位中逻辑 1 的数量比逻辑 0 多,那么 DBI 会将数据反转。例如,如果原始数据是 11100000,DBI 将其反转为 00011111,以此来减少高电平和低电平之间的不平衡,降低电力消耗和电磁干扰。

这里我们选择启用DM,不启用DBI。

下面是存储器地址映射形式,这里我们采用官方推荐的默认形式:ROW_COLUMN_BANK,Ordering选择Normal, 详细的解释可以参考:

从零开始讲DDR(4)——Xilinx方案![]() https://ztzhang.blog.csdn.net/article/details/142406830

https://ztzhang.blog.csdn.net/article/details/142406830

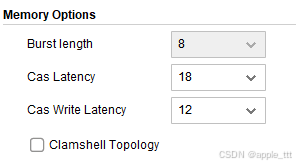

2.2.4 Memory Options

这里面有3个选项,第一个是突发长度,直接设置成一个Byte。

CAS Latency(列地址选择延迟) 是指从内存控制器发出读命令到内存模块返回数据所需的时钟周期数。简单来说,它表示内存读取操作的延迟。

工作原理: 当你执行一个内存读操作时,内存控制器首先发出一个“激活行”的命令(Active),然后根据指定的列地址发出列地址选择命令(CAS)。列地址选择命令告诉内存模块要读取哪个列的数据。CAS Latency 就是从发出列地址选择命令开始,到数据从内存返回给控制器所需的时钟周期数。

例如: 如果 CAS Latency (CL) = 9,意味着内存控制器发出列地址选择命令之后,需要 9 个时钟周期才会接收到数据。

对系统性能的影响: CAS Latency 是影响内存性能的一个关键因素。CL 值越小,内存的读取速度越快,因此通常需要选择 CL 值较低的内存条以提高系统性能。

CAS Write Latency (CWL) 是指从内存控制器发出写命令到内存模块开始写入数据所需的时钟周期数。

工作原理: 类似于 CAS Latency,CWL 是关于写操作的延迟。具体来说,CWL 定义了内存控制器发出写命令后,内存模块开始写入数据的延迟周期数。CWL 是在写操作时需要的时钟周期数,它与内存控制器与内存之间的时序设计密切相关。

例如: 如果 CWL = 6,表示从内存控制器发出写命令到内存开始写入数据之间有 6 个时钟周期的延迟。

对系统性能的影响: 对于写操作,CWL 也直接影响内存的写入速度。CWL 值越小,写操作的延迟越短,性能越好。

CAS Latency (CL) 是针对读取操作的延迟,描述了从发出读取命令到数据返回之间的时间延迟。CAS Write Latency (CWL) 是针对写入操作的延迟,描述了从发出写命令到数据写入内存开始之间的时间延迟。某些内存模块的 CWL 可能会与 CL 不完全相等,这是因为写入数据和读取数据的时序要求不同,写操作可能需要更多的时钟周期来进行数据存储。

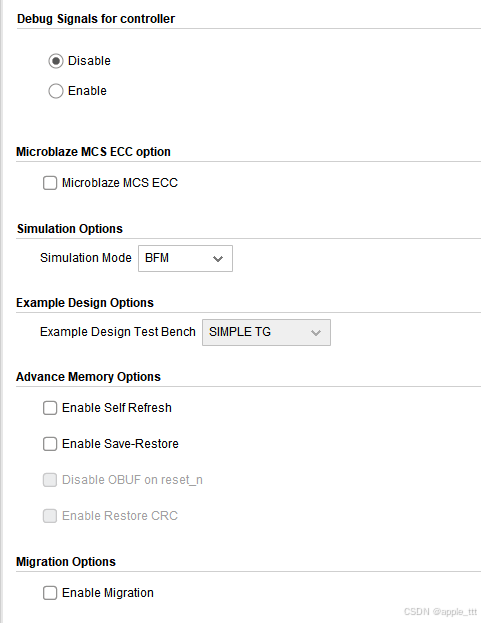

2.2.5 Advanced User Request Controller Options

这里有一些额外的附加选择,我们就保持默认的状态即可。

2.3 Advanced Clocking

2.3.1 Specify MMCM M and D

还记得之前Basic的配置中有一个Specify MMCM M and D on Advanced Clocking Page to calculate Ref Clk的选择,对应的计算公式在这里进行了展示,前文已经有所解释,这里不过多赘述。

2.3.2 System Clock Option

这里选择的是参考时钟的来源,一般来说,可选项如下:

- Differential:来源是外部的差分时钟

- Single Ended:来源是外部的单端时钟

- NO Buffer:来源是MMCM或者PLL,因为MMCM的输出会自带BUFG

这里需要根据自己使用时钟的来源进行选择,我这里使用的是开发板上的差分时钟,所以选择Differential。

2.3.3 Additional Clock Outputs

MIG IP 可以通过与生成 ui_clk 的同一MMCM生成最多四个附加时钟。GUI会列出从MMCM生成的可能时钟频率,附加时钟的频率会根据所选的内存频率(基本选项卡中的“Memory Device Interface Speed (ps)”值)、所选的FPGA以及FPGA的速度等级而变化。这里我们不需要使用。

2.4 Advanced Options

这里提供了一些额外的高级选项,我们保持默认配置,不做修改。

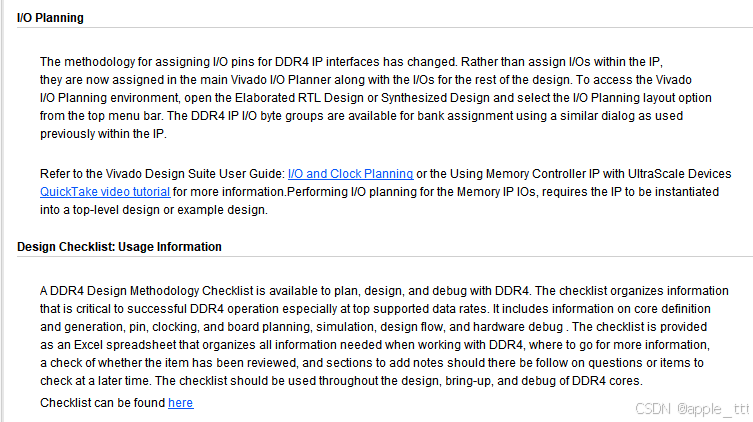

2.5 I/O Planning and Design Checklist Tab

这里提供了一些设计信息的说明。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?