在为设计中的不同timing路径设置时序约束时,有一些timing路径需要特别注意,有些timing路径不需要满足,这些路径被称为被称为Timing Exceptions。其中一个例外是“False paths”。

通常,发射触发器会传输一个信号,该信号需要在下一个时钟周期中被捕获触发器捕获。但有一些路径,传输的信号可以随时到达另一个触发器(而不仅仅是一个时钟周期)。这些路径不需要任何timing约束设置,并被称为“false path”。

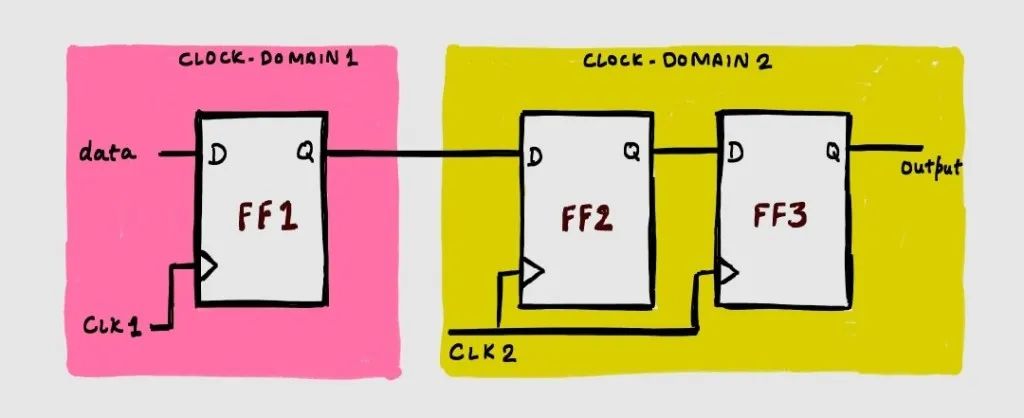

最常见和最重要的false path场景之一是两级触发器同步器,如图所示。

由于FF1和FF2位于不同的时钟域,因此FF2 setup/hold违例的可能性很大。即使FF2输出是亚稳态的,FF3也会避免亚稳态并给出固定的输出。这种亚稳态概率取决于两个时钟的频率。因此,从FF1到FF2(同步器的第一个阶段)不需要timing要求,它可以被设置为“False path”。

其他false path场景:

设计中走不到的物理路径也被称为false path。例如,下图中的mux结构。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?