- 数字芯片设计人员在对数据流的处理中,免不了会遇到存在无效数据的情况,此时通常有两种处理方式:

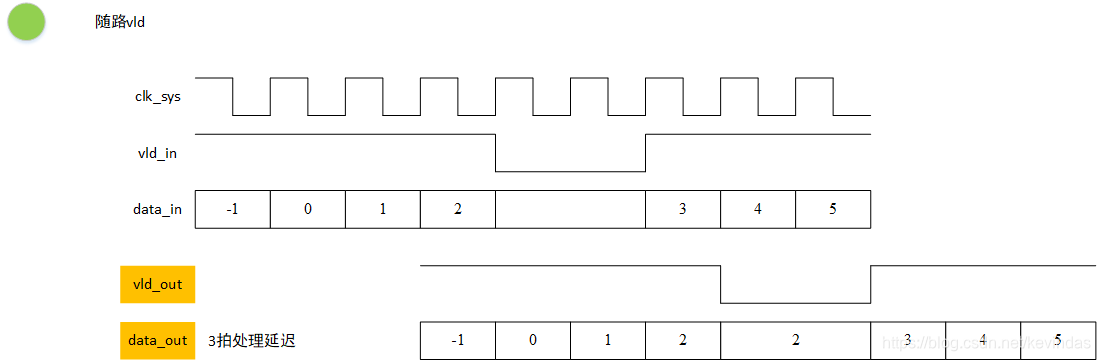

- 一是采用随路vld的方式。vld_in跟随数据,数据每做一拍的处理,vld对应打一拍;数据在vld有效时进行处理,无效时保持。

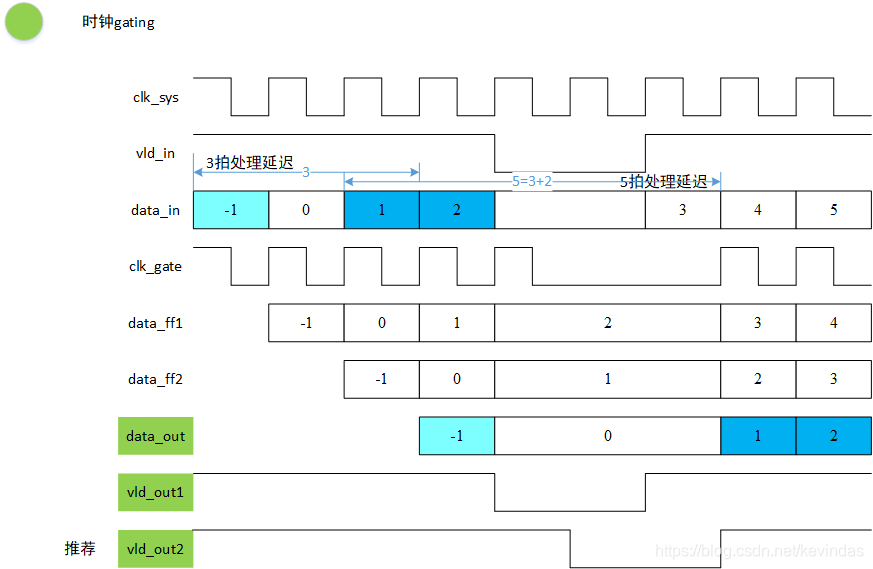

- 二是采用时钟gating的方式。直接在时钟上产生缺口(ICG),数据流在缺口时钟下进行处理。

- 可以看到:

1、随路vld的处理方式下,输入到输出的处理延迟是确定的,取决于数据的处理拍数。

2、时钟gating的处理方式下,输入到输出的处理延迟是不确定的,最大延迟为数据的处理拍数+处理拍数内vld的缺口数。假设vld_in缺口无限大,就会永远得不到输出。

3、采用时钟gating的处理方式,输出vld_out有两种选择,推荐使用第二种,和大家平时习惯符合(先有效数据,后保持数据)。

4、在数据流处理只有1拍的情况下,两种处理方式是等价的。

本文探讨了数字芯片设计中处理无效数据的两种方法:随路vld与时钟gating。vld保证了确定的延迟,而gating可能导致不确定延迟。介绍了如何选择输出vld_out策略,并强调了这两种技术在单拍处理时的等价性。

本文探讨了数字芯片设计中处理无效数据的两种方法:随路vld与时钟gating。vld保证了确定的延迟,而gating可能导致不确定延迟。介绍了如何选择输出vld_out策略,并强调了这两种技术在单拍处理时的等价性。

4889

4889

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?