定义:

Multi-bit Cell 是一种数字电路设计中的术语,通常用于数字信号处理器(DSP)和其他高速数字电路中。它是一个处理多位二进制数字的单元,可以执行加法、减法和其他数学运算。

Multi-bit Cell 由多个逻辑门组成,通常包括加法器、寄存器、比较器和其他逻辑元件。它可以处理多个二进制位(通常是4位或8位),并在单个时钟周期内执行一次运算完成多位数的运算。

优化PPA:

Multi-bit Cell 的应用通常可以帮助降低功耗并优化 PPA(性能、功耗和面积)。

在数字电路中,使用多位的数据处理单元可以减少运算的次数和电路的复杂度,从而降低功耗和面积。使用 Multi-bit Cell 可以同时处理多个二进制位,可以执行一次运算完成多位数的加法、减法等运算,这样在实现相同功能的情况下,所需的逻辑门数量可以减少。

在数字信号处理器(DSP)等需要高性能和低功耗的应用中,Multi-bit Cell 的应用可以有效地优化功耗和性能。例如,多位处理器可以在单个时钟周期内处理多位数据,从而减少时钟周期数,减少运算时间和功耗。此外,由于 Multi-bit Cell 在单个单元中处理多个位,因此它可以减少数据传输的次数和带宽,这也有助于降低功耗和提高性能。

总之,使用 Multi-bit Cell 可以在数字电路中实现高性能、低功耗和小面积,因此它在需要处理大量数字数据的应用中非常有用。

功耗优化详解:

-

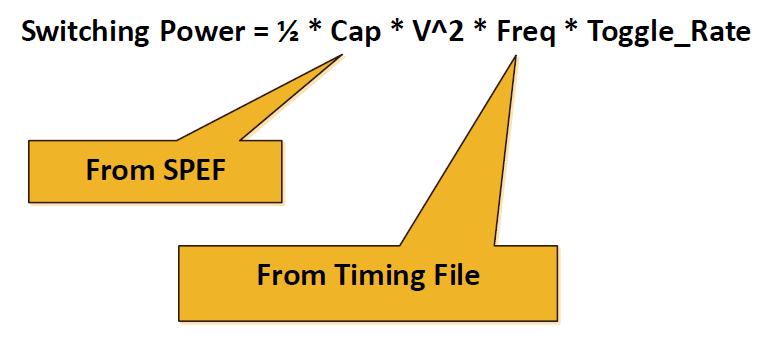

多bit cell的 clock pin capacitance减少从而降低动态功耗中clock switching power。

2)时钟树buffer数量减少,降低switching和leakage power。

引入multi-bit cell的design中,同样的buffer可以驱动更多bit的DFF,buffer数量减少,进一步降低时钟树上的功耗。

3)绕线资源优化,有效减少时钟树寄生RC,也节省部分功耗。

当design中的multi-bit DFF数量占据绝大多数的时候,相对于single-bit design来说,整体的DFF standard cell数量减少,且DFF的摆放一般比较集中,这就会减少很多绕线,进而优化了时钟网络的绕线寄生RC。

尽管multi-bit cell理论上会带来很大的收益,但具体还要看项目评估。

实际应用中,通常会遇到以下几个方面问题:

-

single-bit到multi-bit的转化可能会带来时序上恶化,很多时候会发现实际的multi-bit cell比率不高,达不到降低功耗的效果

-

multi-bit cell摆放的不合理反而会增加更多的组合逻辑的power从而抵消clock 上带来的功耗降低的效果,有时会发现功耗收益为负。

-

IR Drop会考虑让multi-bit cell不要聚集,这样在减少clock line寄生RC的效果就不明显,达不到想要的功耗优化

总之,具体还要结合当前项目进行合理评估,以免适得其反。

本文介绍了Multi-bit Cell,它是数字电路中处理多位二进制数字的单元,由多个逻辑门组成。其应用可降低功耗、优化PPA,还能从多方面优化功耗。不过,实际应用中可能出现时序恶化、功耗收益为负等问题,需结合项目合理评估。

本文介绍了Multi-bit Cell,它是数字电路中处理多位二进制数字的单元,由多个逻辑门组成。其应用可降低功耗、优化PPA,还能从多方面优化功耗。不过,实际应用中可能出现时序恶化、功耗收益为负等问题,需结合项目合理评估。

2400

2400

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?