Multi-bit cells作为一种控制功耗的手段已经广泛应用于大量的芯片设计中,各种EDA工具中也提供了广泛而完善的支持。今天我们将对这种cell的基本构造和原理开始,带大家一起认识一下multi-bit cell。

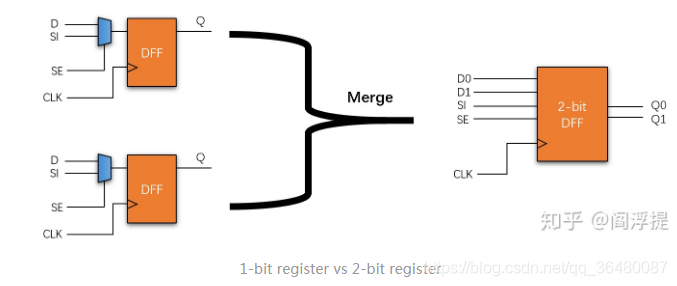

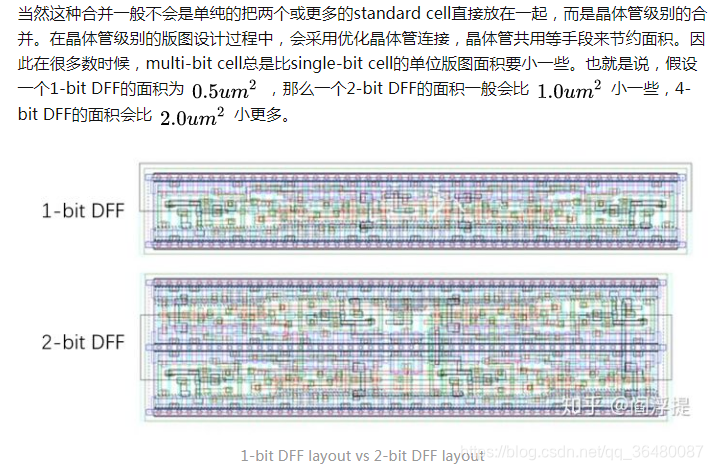

首先,顾名思义,所谓multi-bit cell,就是同一个cell中包含多个逻辑位,也可以理解成把多个完全相同的cell合并在一个cell里。以DFF为例,single bit 和multi bit的逻辑关系一般如下(注:此处展示的均为scan DFF):

这种multi-bit结构会在功耗上带来的好处主要体现在一下几个方面:

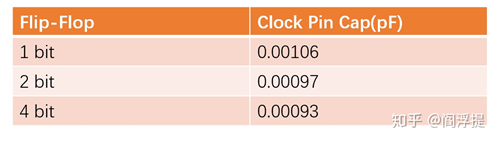

1)clock pin capacitance减少从而降低clock switching power。

下表列出了同种DFF不同bit的clock pin capacitance数值。从中可以看出,single-bit结构与multi-bit结构并未在clock pin cap上有明显差别,因此当design中有大量multi-bit DFF来替代single-bit DFF时,其时钟上整体的pin cap数值下降将是非常明显的。而基于我们对switching power的理解可知,cap越小switching power也会越小,这就会对时钟树上整体的动态功耗降低起到很好的作用。

2)时钟树buffer数量减少,降低switching和leakage power。

在multi-bit design中一个相同的buffer可以驱动更多bit的DFF,从而显著减少时钟树上的buffer数量和面积,进一步降低时钟树上的功耗。

3)时钟树绕线资源优化,有效减少时钟树寄生RC从而降低dynamic power。

当design中的multi-bit DFF数量站据绝大多数的时候,相对于single-bit design来说,整体的DFF standard cell数量必然大幅下降,而且在很多时候DFF的摆放也可能会更加集中,这就会在时钟树上节约更多的绕线,进而减少整个时钟网络的绕线寄生RC。

尽管multi-bit有以上诸多优点,但是在实际应用中并不总能得到最好的结果。其主要原因在于以下几个方面:

a) single-bit到multi-bit的转化有诸多条件限制,因此在很多时候会发现design实际的multi-bit cell比率不高,从而达不到想要的降低功耗的效果

b) multi-bit cell摆放的不合理可能会引起绕线资源紧张,甚至使timing恶化,反而会增加更多的组合逻辑的power从而抵消clock line上带来的功耗降低的效果

c) IR/EM方面的考虑可能会故意让multi-bit cell互相摆放的远一些,从而无法达到减少clock line寄生RC从而降低功耗的效果

本文介绍了Multi-bit cell在芯片设计中的低功耗应用。Multi-bit cell指一个cell包含多个逻辑位,能减少clock pin capacitance、时钟树buffer数量和优化绕线资源,降低功耗。但实际应用中,因转化条件限制、摆放不合理及IR/EM考虑等,不一定能达最佳降功耗效果。

本文介绍了Multi-bit cell在芯片设计中的低功耗应用。Multi-bit cell指一个cell包含多个逻辑位,能减少clock pin capacitance、时钟树buffer数量和优化绕线资源,降低功耗。但实际应用中,因转化条件限制、摆放不合理及IR/EM考虑等,不一定能达最佳降功耗效果。

4909

4909

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?