一、半导体器件物理

1.PN结

1.1 如何工作

PN结由P区和N区组成,在两个区中间会形成空间电荷区,所以会形成内建电场。

PN结打开:当外加正偏压时,会抵消一部分内建电场,使得空间电荷区减小,势垒减小,打破了漂移电流和扩散电流的平衡,使得P区的空穴扩散到N区,N区的电子扩散到P区,漂移电流减小,扩散电流占优势,产生了PN结正向电流。

PN结关断:当外加反向偏压时,会增大势垒,多数载流子越过空间电荷区更加困难,使得漂移电流>扩散电流,但漂移电流是少子电流,所以反向电流很小,PN结关断。

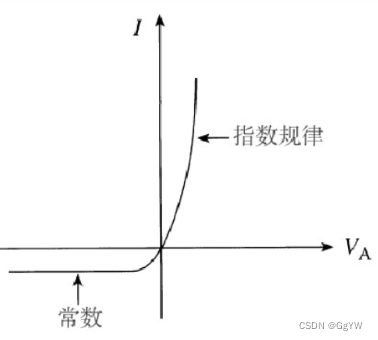

1.2 I-V特性曲线

2.MOSFET

2.1 与双极性晶体管(BJT)相比优点

①输入阻抗高。有利于各级间的直接耦合。(可以通过MOSFET是压控电流源,电流源电阻理想情况是无穷大来理解)

②温度稳定性好。

③噪声较小。

④在大电流情况下跨导基本不下降。(跨导也就可以理解为增益)

⑤没有少子存储效应,开关速度快。(MOSFET是多子器件,BJT为多子+少子,且少子占主导)

⑥功耗低。(栅控)

⑦制造工艺简单。

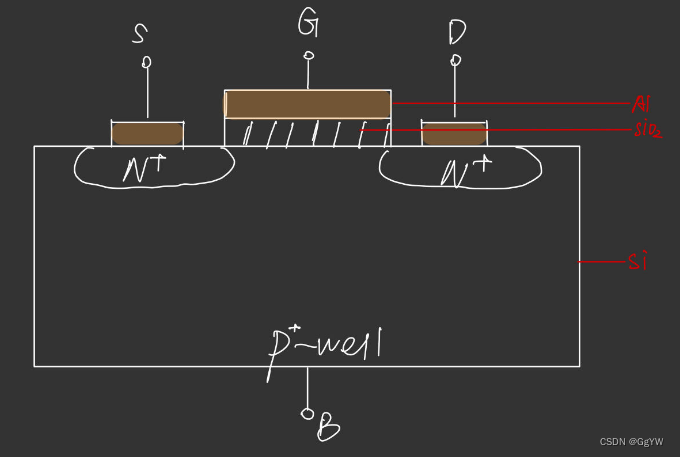

2.2 结构

NMOS:

S(source):源极

D(drain):漏极

G(gate):栅极

2.3 工作原理

以NMOS为例(上图):

当没有外加适当的栅压(Vgs)时,源漏区被两个背靠背的PN结隔离。若在此时外加偏压(Vds),除了及其微小的PN结反向电流,是不会产生电流的。

当施加Vgs时,就会在栅极下面产生一个指向内部的电场。

当Vgs > Vth 时,由于电场作用,栅极下面发生强反型,连通源漏极。外加Vds时就能产生源漏电流。

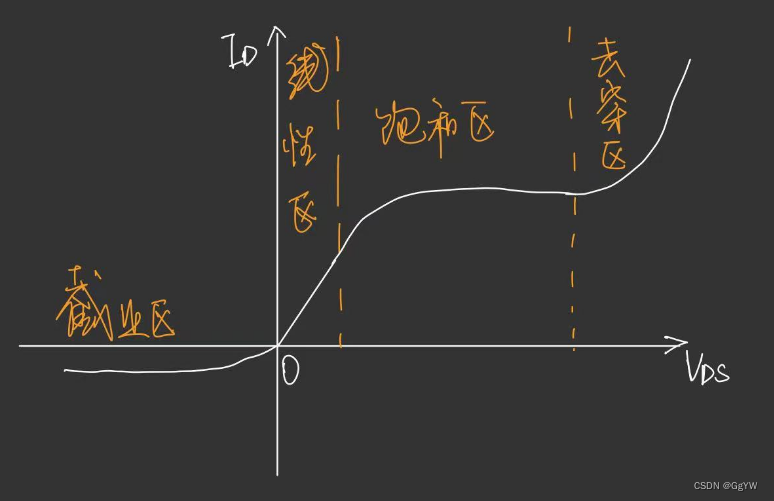

①Vgs < Vth 时,截止区。

②Vds < Vgs - Vth 时,线性区;常用作开关。

③Vds > Vgs - Vth 时,饱和区;常用作放大器。

(此时出现沟道夹断,沟道与漏区间隔着一段耗尽区,当沟道中的自由电子到达沟道端的耗尽区边界时,将立即被耗尽区内的强电场扫入漏区。由于电子在耗尽区内的漂移速度达到了饱和速度,不再随电场变化,故漏电流也不再随偏压增大)

④当Vds增大到源漏击穿电压时,反偏的漏PN会因雪崩倍增效应发生击穿。

(当一个半导体二极管加上足够高的反向偏压时,在耗尽层内运动的载流子就可能因碰撞电离效应而获得雪崩倍增。)

(对于包含PN结的半导体器件,一般说来,雪崩倍增效应是个限制性因素。但也可以利用此效应来制作某些器件,如碰撞雪崩渡越二极管及雪崩注入MOS非易失性存储元件。)

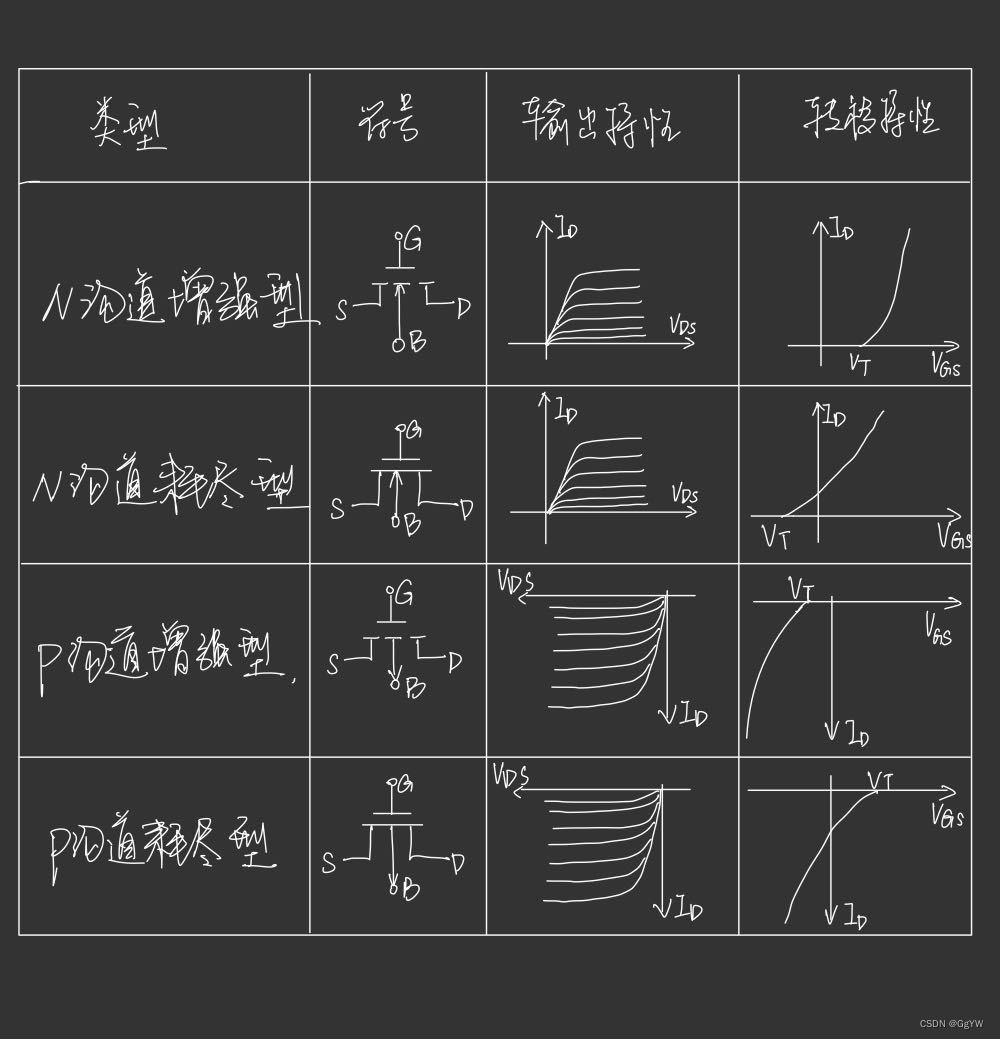

2.4 分类

增强型:无外加栅压时处于关断状态。

耗尽型:无外加栅压时处于导通状态。

2.5 直流特性

2.5.1 直流电流电压方程

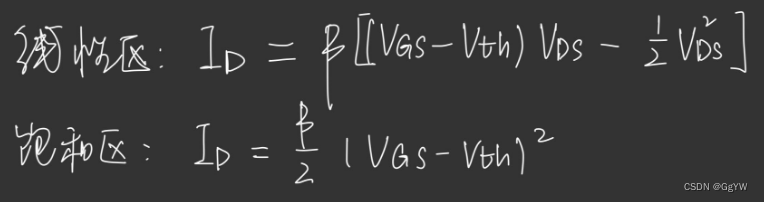

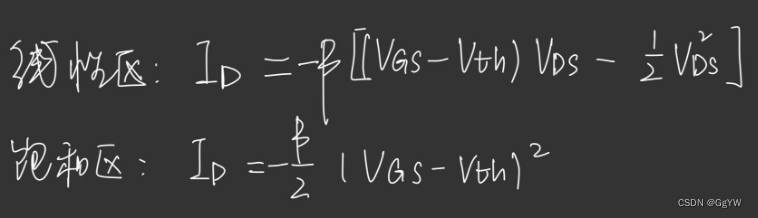

NMOS线性区与饱和区漏极电流:

PMOS线性区与饱和区漏极电流:

2.5.2 直流参数

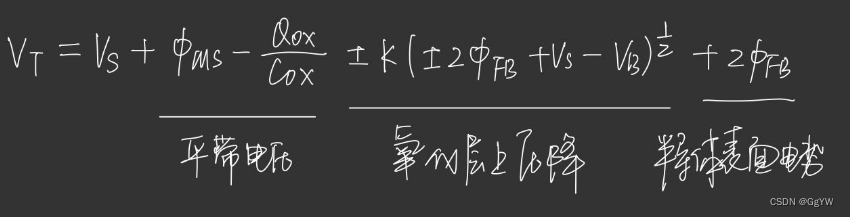

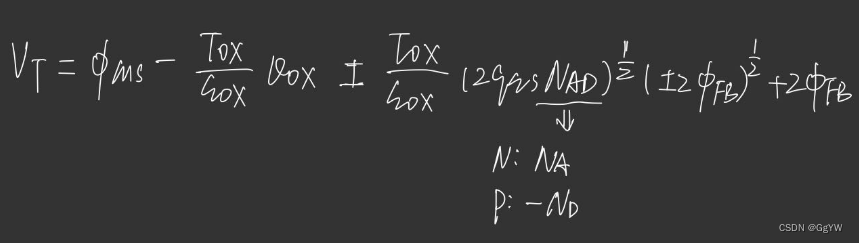

(1)阈值电压

定义:栅下衬底表面开始发生强反型时的栅电压,记作Vth。当Vgs=Vth时,半导体表面处的平衡少子浓度=体内平衡多子浓度。

影响因素:

①栅氧化层厚度Tox :Tox 越薄,阈值电压绝对值越小。

②衬底费米势FB:衬底掺杂浓度影响不大。

③金属半导体功函数差:与金属的种类、半导体的导电类型及掺杂浓度有关。其中衬底掺杂浓度影响也不显著。

④耗尽区电离杂质电荷面密度QA:与衬底浓度有关,成正比。

⑤栅氧化层中的电荷面密度Qox:制造工艺、晶面、氧化后的工艺等都会对其产生影响。

主要与Qox和NA、ND有关。

调整阈值电压主要措施:通过离子注入来改变衬底杂质浓度,也可以在一定范围内改变栅氧化层厚度。

(2)饱和漏电流

对于耗尽型MOSFET,Vgs = 0 时就已导通。该电流与沟道宽长比成正比,与栅氧化层厚度成反比。

(3)截止漏电流

对于增强型MOSFET,Vgs = 0 时不导通,但由于存在亚阈值极电流及PN结反向饱和电流,仍由电流通过。

(4)导通电阻

当MOSFET工作在非饱和区,输出特性曲线为线性,相当于一个与Vds无关的电阻,该电阻与沟道宽长比成反比,与栅氧化层厚度成正比。

(5)栅极电流

由于栅极与沟道间隔着绝缘性良好的氧化层,所以栅电流非常小,使得MOSFET有很大的输入电阻。

2.5.3 温度特性

N沟道MOSFET的漏极电流的温度系数可为正、负或零,主要取决于栅源电压Vgs的数值。只要适当选择工作条件,MOSFET就会有很高的温度稳定性。此外,当Vgs-Vth较大时,也即Id较大从而功耗较大时,Id的温度系数为负,这也有利于MOSFET的温度稳定性。

对P沟道MOSFET有类似的结论。

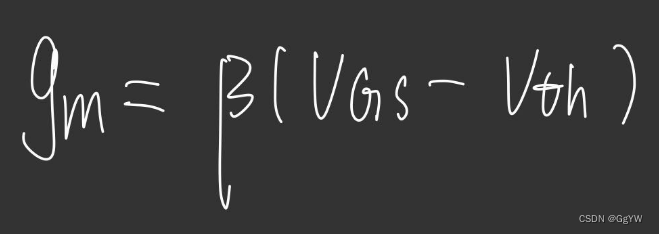

2.6 小信号交流参数——跨导

跨导gm:是转移特性曲线的斜率,反映了栅极电压对漏电流的控制能力,反映了增益。

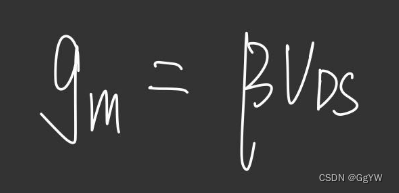

饱和区:

非饱和区:

模拟电路中常工作在饱和区,从电路使用角度,应增大Vgs;从器件设计角度,应提高增益因子,即提高沟道宽长比,与=减薄栅氧化层厚度。

2.7 效应

2.7.1 衬底偏置效应(体效应)

衬底偏压Vbs对N沟道MOSFET转移特性曲线的影响:当外加Vbs后,转移特性曲线的形状并没有改变,而只是随着|Vbs|的增大而向右平移。转移特性曲线在横轴上的截距就是阈电压,所以曲线向右平移就意味着阈电压增大。

物理解释:外加偏压将使沟道下面的耗尽区的跨度增大,|Qn|减小,为了获得同样多的|Qn|,就必须提高Vgs,也就意味着阈值电压提高。

衬底偏压Vbs对P沟道MOSFET转移特性曲线的影响:当外加Vbs后,转移特性曲线的形状并没有改变,而只是随着|Vbs|的增大而向左平移,说明电压负方向移动,阈电压绝对值增大。

2.7.2 漏极电流不饱和的原因

(1)有效沟道长度调制效应

沟道有效长度随Vds的增大而缩短的现象称为有效沟道长度调制效应。(可将夹断区域看作PN结的耗尽区,随着Vds增大反偏增大,耗尽区变宽,有效沟道长度缩短)

(2)静电场的反馈作用

由于漏区与沟道间的静电耦合,当偏压Vds增大,沟道内载流子增多,沟道电导增大,漏电流增大。

使漏极电流不饱和的原因有有效沟道长度调制效应和静电场的反馈作用。在衬底掺杂浓度低时以静电场的反馈作用为主。

2.7.3 小尺寸效应

(1)阈电压的短沟道效应

阈电压随沟道长度的缩短二减小。

(2)阈电压的窄沟道效应

当沟道宽度很小时,阈电压随宽度减小而增大。

621

621

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?