- 衬底偏置效应

1、NMOS和PMOS的衬底电位

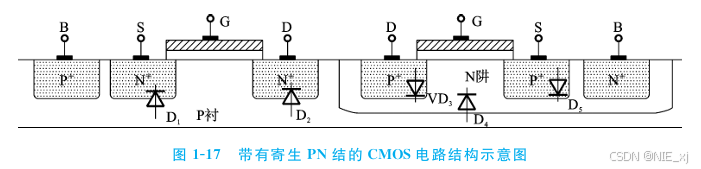

CMOS电路中有许多寄生的PN结,如上图所示。我们希望MOS管的电流仅仅在源极和漏极之间,通过栅极下方的导电沟道流过。也就是说,我们不希望这些寄生PN结处于导通状态。要让二极管不导通,就要求加载到二极管上的电压不超过其正向导通电压,最简单的方式是给P型衬底接最低电位(通常是GND)而给N阱接最高电位(通常是VCC)。这也就是常用的PMOS管衬底接VCC,NMOS管衬底接GND。

2、衬底偏置效应

根据MOS管的I-V特性可知,MOS管的电流与耗尽层、反型层的分布有密切关系。同时,如果MOS管的源极和体极之间有电压差(VSB ≠ 0),会直接影响结电容的势垒,也会影响耗尽层和反型层的分布,从而最终影响MOS管电流。

当VSB > 0时,源极周围的耗尽区扩大,耗尽区产生了更多的负电荷,会“抵制”从源端过来的电子,这需要更大的VGS来补偿这个效应。从而,即使MOS管的VGS和VDS相同,其电流也与VSB = 0的情况不相同。这种现象通常被归纳为对VTH的影响,称为“衬底偏置效应”,也称为“体效应”。此时阈值电压变为:

![]()

式中![]() 为不存在衬底偏置效应时的阈值电压;

为不存在衬底偏置效应时的阈值电压; ![]() 为费米能势;

为费米能势; ![]() 为MOS管体效应系数。由上式可知,只要VSB > 0,阈值电压就比不存在衬底偏置效应时的阈值电压高,即在相同VGS和VDS的情况下,存在衬底偏置效应的MOS管,其电流比不存在衬底偏置效应的MOS管要小。

为MOS管体效应系数。由上式可知,只要VSB > 0,阈值电压就比不存在衬底偏置效应时的阈值电压高,即在相同VGS和VDS的情况下,存在衬底偏置效应的MOS管,其电流比不存在衬底偏置效应的MOS管要小。

该效应还称为“背栅效应”,即衬底可以等效为另外一个可以对MOS管的电流进行控制的栅极,只是控制能力相对于真正的栅极要弱得多。这个等效的栅,位于MOS管真正的栅极的另外一面,从而该效应也可以称为“背栅效应”。

- 沟长调制效应

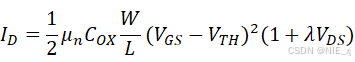

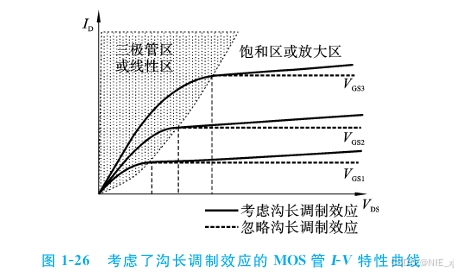

当MOS管工作在饱和区时,随着漏源电压的增加,会出现夹断现象,实际的导电沟道逐渐变短,这将会影响MOS管的电流。当夹断区的有效沟道长度变化时,漏源电流随漏源电压的变化而改变,而非一个固定值。该效应称为沟长调制效应。考虑了沟长调制效应后,MOS管的I-V特性应修改为:

式中λ被称为MOS管的沟长调制系数。上式表明,当MOS管工作在饱和区时,随着![]() 的增加,漏源电流是线性增加的。

的增加,漏源电流是线性增加的。

MOS管的沟长调制系数λ并非定值,而是与沟道长度L成反比,且随沟道掺杂浓度的增加而递减。同一种工艺下,晶体管的沟道长度越短,λ越大,沟长调制效应越明显,晶体管工作在饱和区时的漏源电流受漏源电压的影响越大。

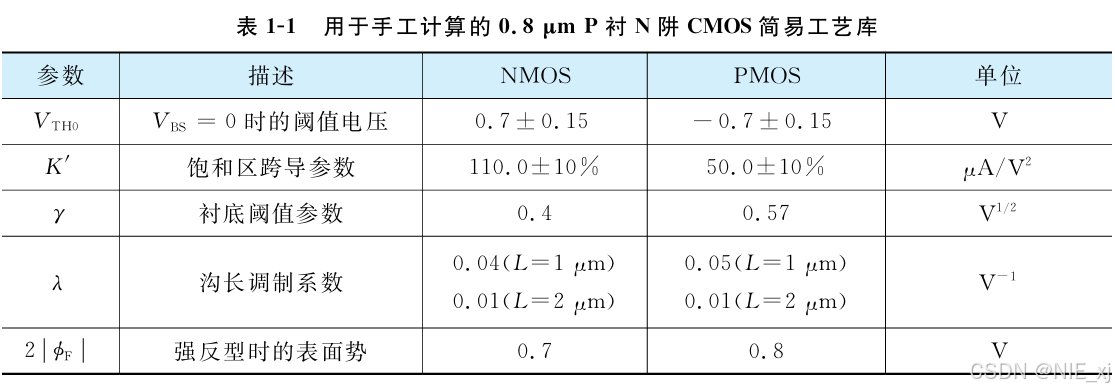

Phillp Allen在其教材中给出了用于手工计算的一个工艺库一级模型,如下表所示。模型中不同L下的λ与L并不成比例关系。

在实际的电路设计中,由于漏极耗尽层中的电场分布非常复杂,导致计算λ比较困难,最管用的方法是通过仿真MOS在不同L情况下的I-V特性曲线,从曲线中提取λ值。提取λ值的方法,就是根据仿真曲线,选取饱和区波形上的几个点,读取每个点的VDS、VGS、IDS,然后列写饱和区MOS管电流公式,依据多个方程联立可以求解简化的一级模型工艺参数。

参考来源:[1]邹志革,刘冬生编.新工科暨卓越工程师教育培养计划集成电路科学与工程学科系列教材 CMOS模拟集成电路设计基础[M].武汉:华中科技大学出版社,2024

349

349

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?