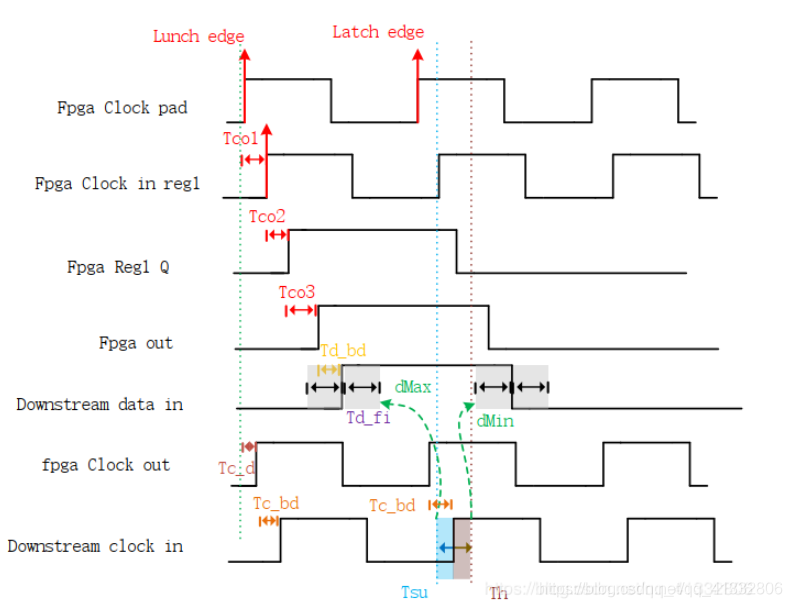

在前面的博客中,介绍了output_delay的基础。output_delay就是从FPGA管脚输出到下游芯片之间的时钟和数据之间的关系。

output_delay的约束,就是希望输出时钟落在数据的合适的区间:

dMin = bskew

dMax = Tcycle - askew

1 output_delay约束

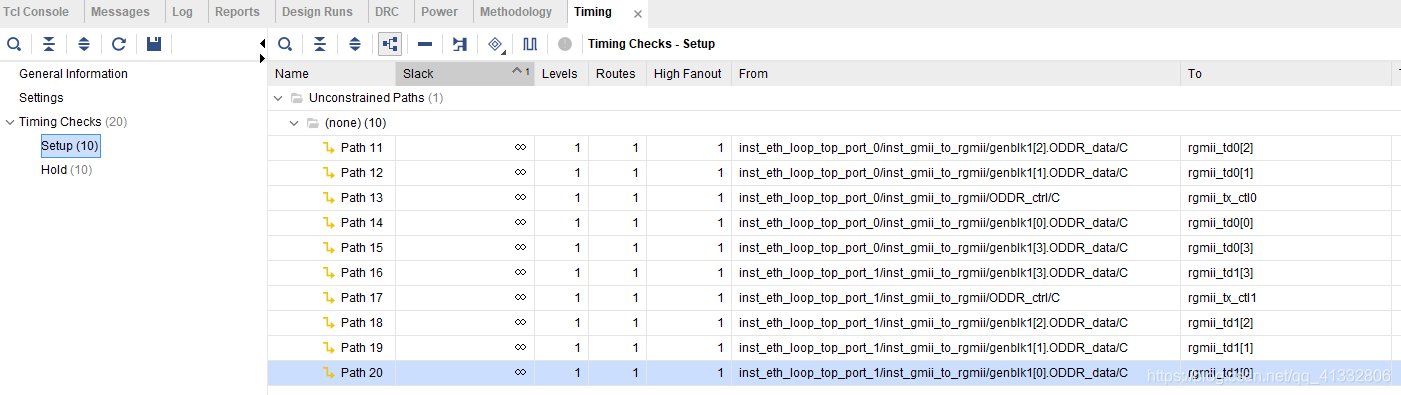

我所使用的工程中,通过ODDR原语输出千兆网的发送时钟,这个时钟,没有经过PLL,需要对其进行生成时钟的约束,对其进行约束后才能对输出的数据进行output_delay。没有进行output_delay时的时序报告如下,可以看到对于输出的余量都为无穷。

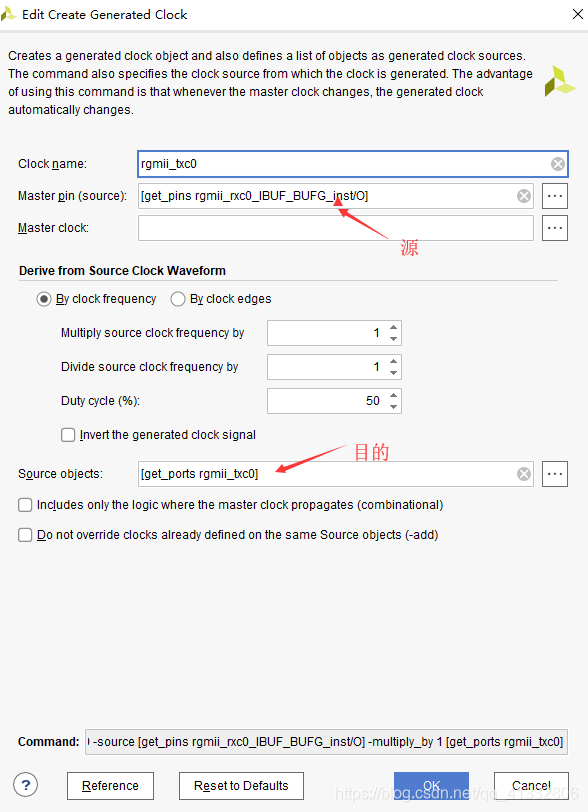

1.1 生成时钟约束

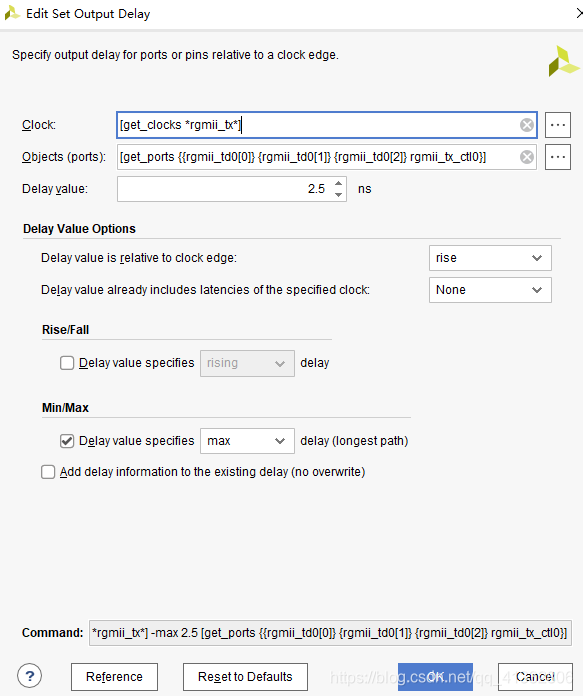

1.1 output_delay约束

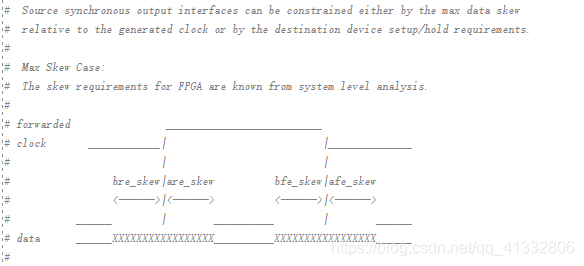

对于output delay的约束,本质上考虑的是输出到FPGA管脚处的时钟和数据之间的关系。在上图所示的截图中,特给出了Xilinx官方在进行output delay约束时的表示方法。可以看到输出output delay同样只是表现数据和时钟之间的关系。

设置output delay 的方式与input delay类似。约束好后,可以综合后查看时序报告,然后根据时序报告来对约束进行修改。

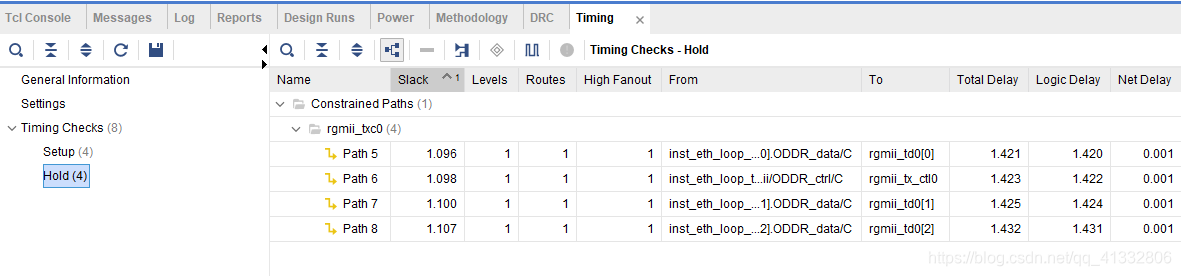

可以看到此时输出路径上的数据也都满足建立时间和保持时间的要求。output delay就设置好了哦。

参考:

V3学院时序分析课程

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?