引言

记录一些 我自己刷的 IC行业招聘真题,不是每题记录,只记录一些值得记录的,写下自己的看法。主要是一些数字IC行业题目,偏前端。

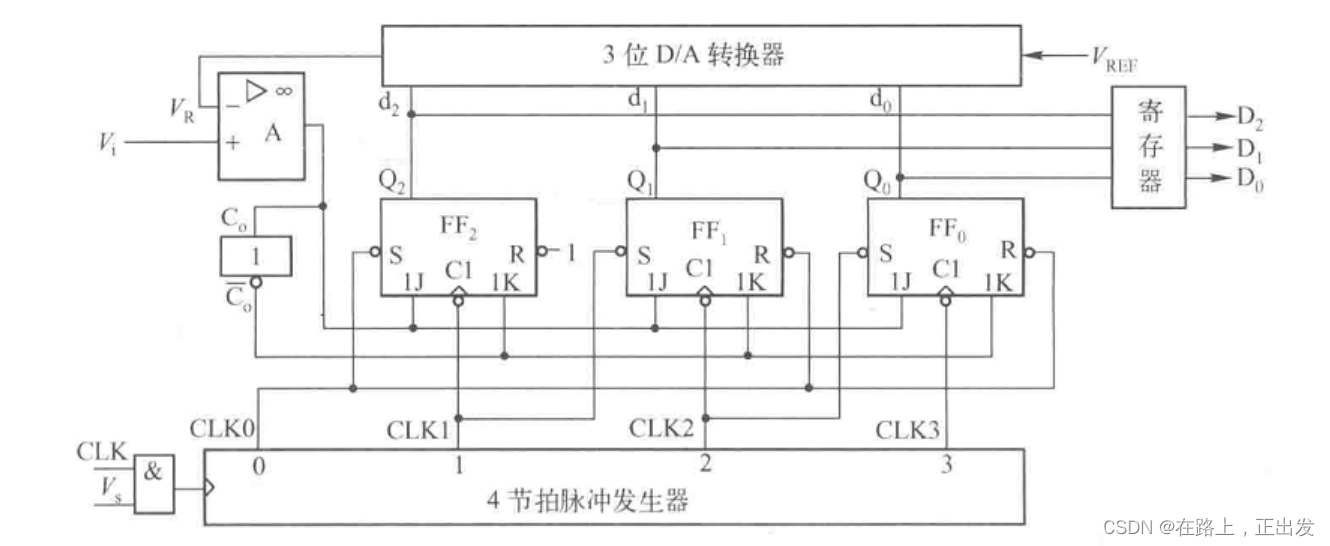

1、有一个逐次逼近型 8位A/D 转换器,若时钟频率为250KHz,完成一次转换需要多长时间?

逐次逼近型 A/D转换器的工作原理类似于用砝码称重,一个时钟周期操作一次确定一个比特,所以至少需要8个时钟周期才能完成A/D量化,但是芯片实际工作还需要额外的两个时钟来完成数据清除和输出。因此对于时钟频率为 f_clk Hz 的 n 位逐次逼近型A/D芯片,完成一次转换的时间为

T = (n+2)/ f_clk

注:也有一些计算公式给的是(n+1) / f_clk。

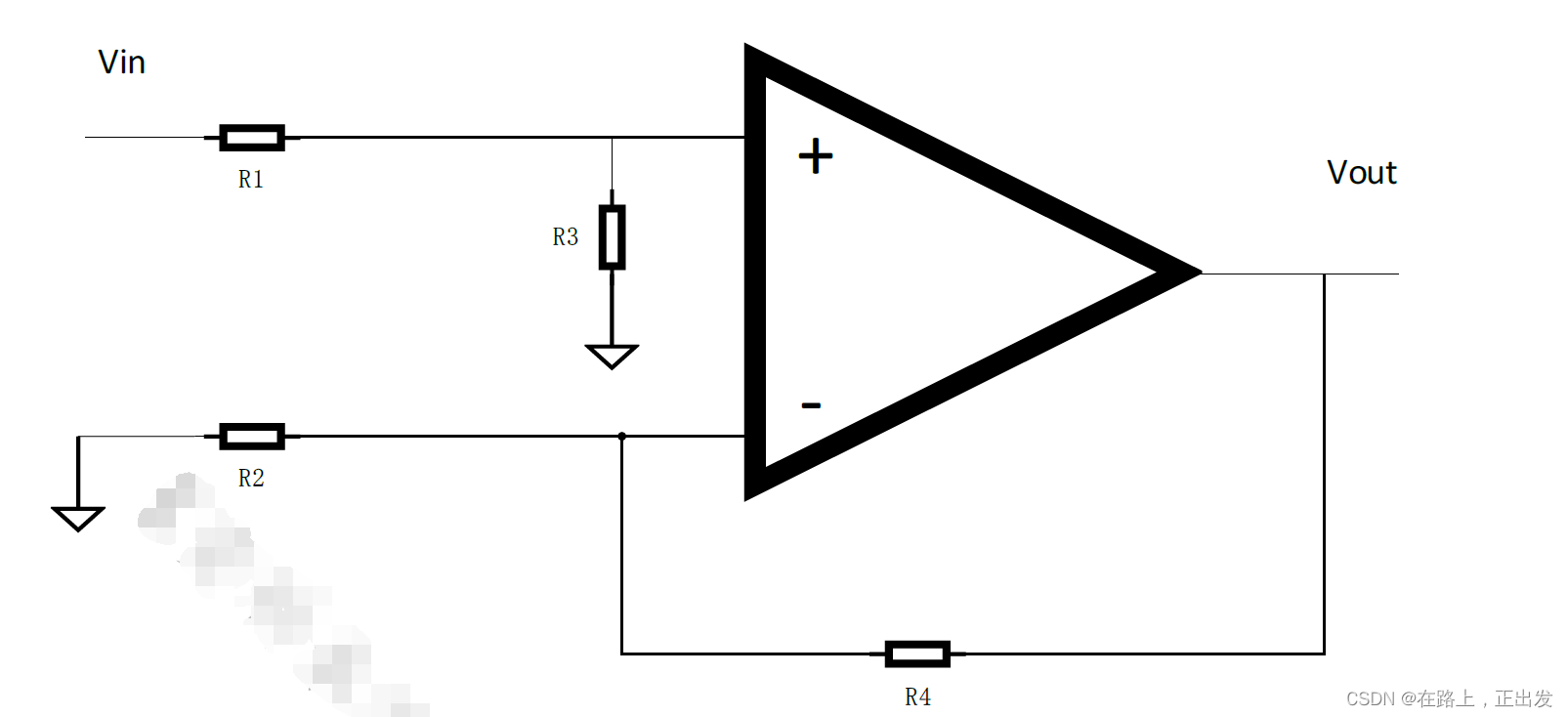

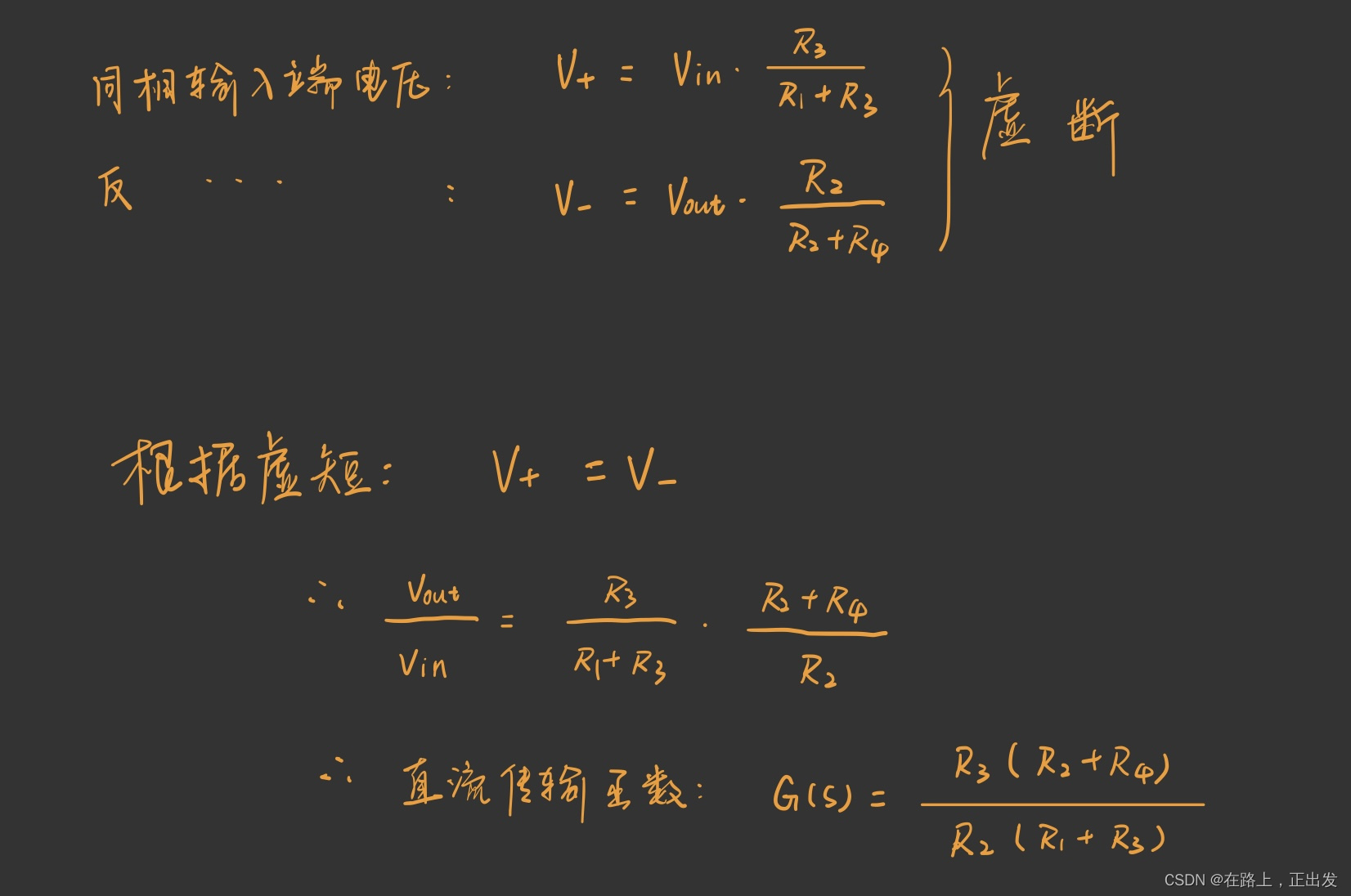

2、如下运放应用电路,请写出直流传输函数:

我的题解如下,主要运用了放大器的虚短虚断:

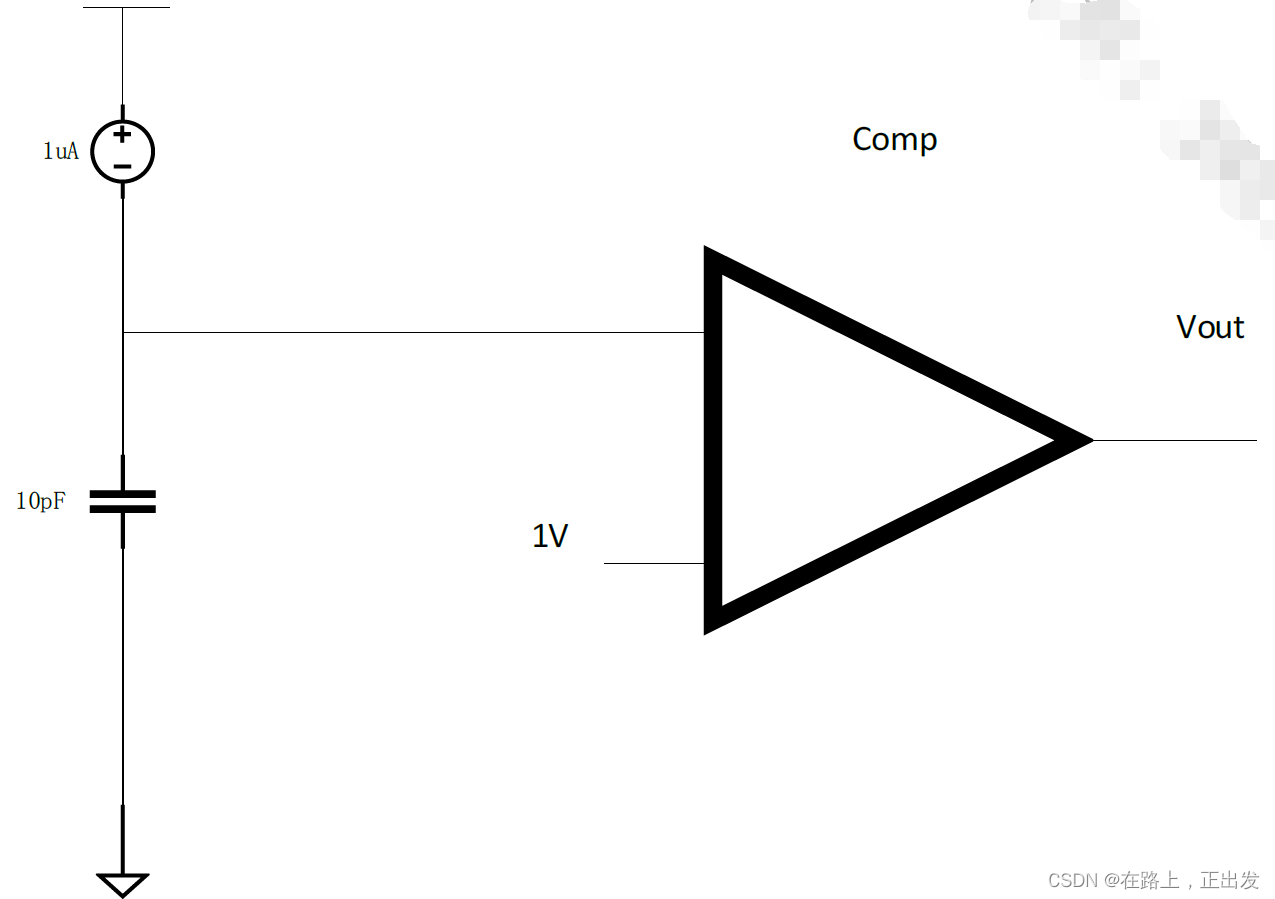

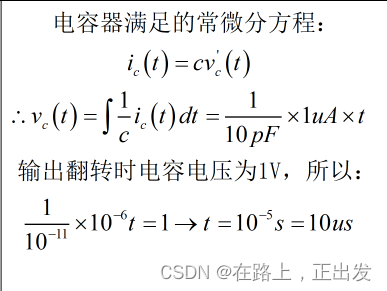

3、如下电容初始电压为0V,请根据图中参数计算出,电容充电到比较器翻转的时间:

我的题解如下,主要用到了电容充电的微分方程。

4、移位寄存器由8级触发器组成,用它构成的扭环计数器具有【】种有效状态;用它构成的环计数器具有【】种有效状态;构成线性反馈移位寄存器具有【】种有效状态。

【解析】假定触发器的级数为n,那么扭环计数器的状态数为2n,环形计数器的状态数为n,线性反馈移位寄存器的状态数为2^n-1。

5、TTL门电路组成的JK触发器,时钟端接5KHz脉冲,J与K悬空,则输出Q的频率为 2.5kHz

第一:TTL门输入引脚悬空,相当于高电平输入。

第二:JK触发器的表达式:Qn+1 = JQn* + K*Qn。(A* 表示 A非 逻辑)

第三:Qn+1 = Qn*,输出二分频。

6、满足换路定则的前提下:

电感电压可以跳变(突变),但是电流不能跳变;

电容电流可以跳变(突变),但是电压不能跳变;

7、已知某种计数制中有算术运算41/3=13成立,则该算数运算中操作数的基数是()

【解析】8。设基数为x,则有(41)x=4x+1,(3)x=3,(13)Xx+3。因此,4x+1=3(x+3),故x=8。

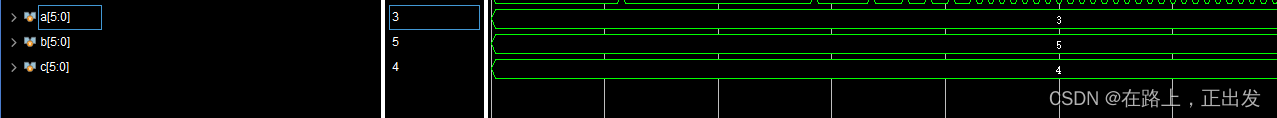

8、下列Verilog 代码执行后,a=() , b= () , c= ( ) 。

initial begin

a=0;b=1; c =2 ;

a = b+c;

b <= a+c ;

c = a +b ;

enda=3, b= 5,c=4。

说明: = 是阻塞赋值,立即进行赋值; <= 是非阻塞赋值,先计算右侧表达式,而后完成赋值。利用Vivado仿真验证的结果如下:

仿真代码(部分):

reg [5:0]a,b,c; initial begin a=0;b=1;c=2; a=b+c; b<=a+c; c=a+b; end

9、Unix系统下实现将a文件夹拷贝为b文件夹的命令()

cp a b -r

10、表征工艺特征的90nm、28nm或7nm 等数字,其代表的含义是什么?

长度指:MOS管栅极长度

11、假设 FIFO 的写时钟为 100MHZ,读时钟为 80MHZ。在 FIFO 写侧,每 100 个时钟,写入 80 个数据;FIFO 读侧,每个时钟读取一个数据。设计合理的 FIFO 深度,使 FIFO 不会溢出。

这个需要考虑极限背靠背的情况,即相邻的两组写入,前一组在后80个时钟写入,后一组在前80个时钟写入,即连续写入160个数据。在连续写入期间读出数据个数=160/(100M/80M)=128个,那么需要至少160-128=32个空间的数据存储。

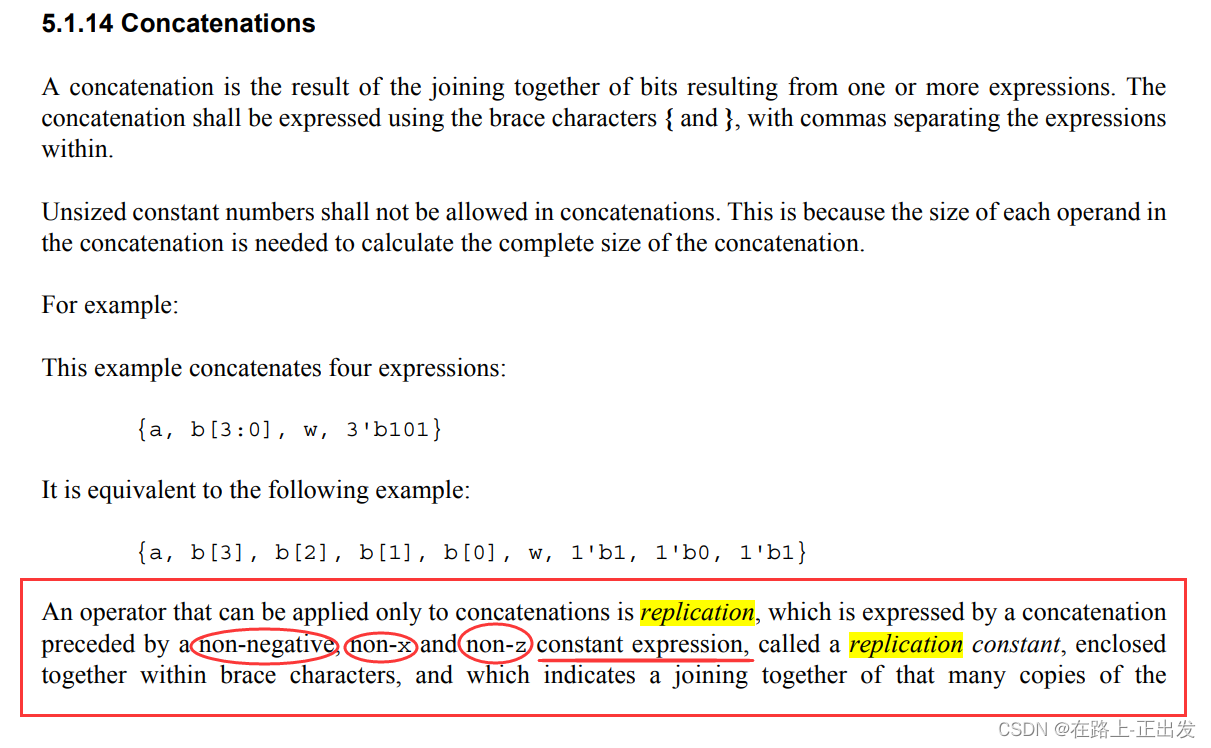

12、verilog仿真文件中,有如下代码块,问参数P取1~32之间的任意值都可以吗?

localparam P=32; wire [31:0]W_1 = 32'hFFFFFFFF; wire [31:0]TEST = {{{(32-P){1'b1}}},W_1[P-1:0]};答案是正确的,是可以的。P 取1时,有人会质疑 W_1[0:0]可以吗?答案是可以的,位索引是支持这样的。主要是当 P 取32时,有人就会犯嘀咕了,我当时也是,有点迟疑,verilog里面复制操作可以只复制0次嘛?答案还是肯定的。我在 IEEE的Verilog 标准 里面找到了答案。

另外,怎么说呢?实践出真知。你可以把这个代码放到Vivado里面或者任何支持Verilog语法的EDA里面仿真一下看看或不会出错就会知道答案。

我在Vivado 2018.3里面真正仿真测试过,没问题。

这篇文章记录了数字IC行业的招聘试题,涉及逐次逼近型A/D转换器的转换时间计算、运放电路的直流传输函数分析、电容充电时间的计算、移位寄存器的应用、JK触发器的工作原理、换路定则的理解、Verilog代码执行后的变量赋值以及Unix文件夹拷贝命令等。同时,文章讨论了FIFO深度设计问题和Verilog代码中的参数使用规则,并强调了实践验证的重要性。

这篇文章记录了数字IC行业的招聘试题,涉及逐次逼近型A/D转换器的转换时间计算、运放电路的直流传输函数分析、电容充电时间的计算、移位寄存器的应用、JK触发器的工作原理、换路定则的理解、Verilog代码执行后的变量赋值以及Unix文件夹拷贝命令等。同时,文章讨论了FIFO深度设计问题和Verilog代码中的参数使用规则,并强调了实践验证的重要性。

8363

8363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?