我在代码中,通过fifo的IP核实现数据的存储和延迟传输,将两个输入在乘法器对齐。

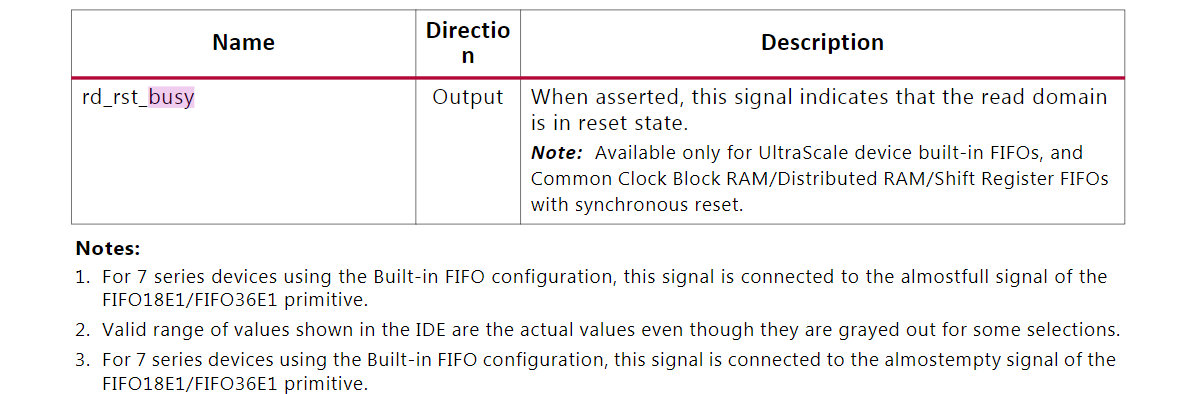

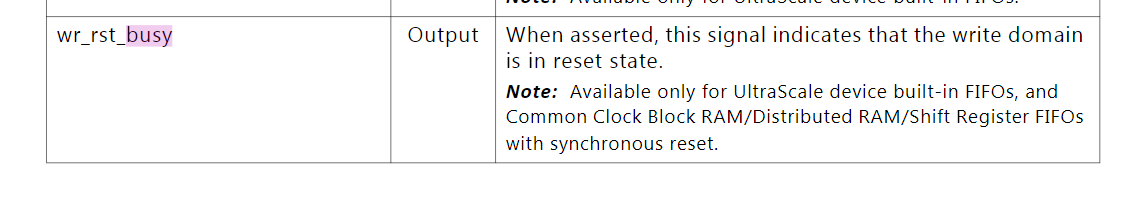

但是发现wr_rst_busy和rd_rst_busy一直会拉高,所以找到问题。

wr_rst_busy和rd_rst_busy的作用

用来指示,系统在复位。也就是IP核正在接收复位信号。

查看fifo generator输出的veo文件

发现代码中的srst应该是一个高电平有效的信号,虽然手册和veo文件中都没有写明,测试出来的结果说明他是一个高电平有效的信号,而不是低电平有效。

fifo_generator_2_n_clk your_instance_name (

.clk(clk), // input wire clk

.srst(srst), // input wire srst

.din(din), // input wire [511 : 0] din

.wr_en(wr_en), // input wire wr_en

630

630

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?