目录

Verilog HDL中总共有十九种数据类型,数据类型是用来表示数字电路硬件中的数据储存和传送元素 的。

四个最基本的数据类型,它们是: reg型、wire型、integer型、parameter型

常量:

整数:

在Verilog HDL中,整型常量即整常数有以下四种进制表示形式:

1) 二进制整数(b或B)

2) 十进制整数(d或D)

3) 十六进制整数(h或H)

4) 八进制整数(o或O)

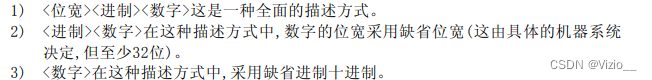

数字表达方式有以下三种:

在表达式中,位宽指明了数字的精确位数。例如:一个4位二进制数的数字的位宽为4,一个4位十六进制 数的数字的位宽为16(因为每单个十六进制数就要用4位二进制数来表示)。见下例:

![]()

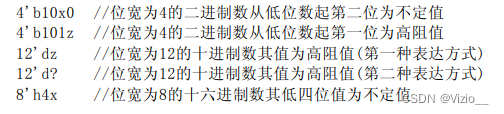

x和z值:

在数字电路中,x代表不定值,z代表高阻值。一个x可以用来定义十六进制数的四位二进制数的状态, 八进制数的三位,二进制数的一位。z的表示方式同x类似。z还有一种表达方式是可以写作?。在使用 case表达式时建议使用这种写法,以提高程序的可读性。见下例:

负数:

一个数字可以被定义为负数,只需在位宽表达式前加一个减号,减号必须写在数字定义表达式的最前 面。注意减号不可以放在位宽和进制之间也不可以放在进制和具体的数之间。见下例:

![]()

下划线(underscore_):

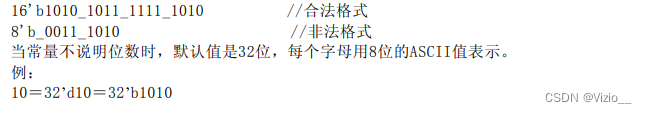

下划线可以用来分隔开数的表达以提高程序可读性。但不可以用在位宽和进制处,只能用在具体的数 字之间。见下例:

参数(Parameter)型:

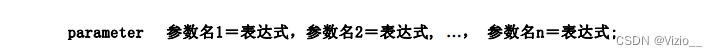

在Verilog HDL中用parameter来定义常量,即用parameter来定义一个标识符代表一个常量,称为符号 常量,即标识符形式的常量,采用标识符代表一个常量可提高程序的可读性和可维护性。parameter型 数据是一种常数型的数据,其说明格式如下:

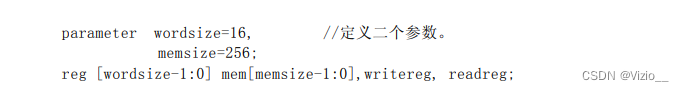

parameter是参数型数据的确认符,确认符后跟着一个用逗号分隔开的赋值语句表。在每一个赋值语 句的右边必须是一个常数表达式。也就是说,该表达式只能包含数字或先前已定义过的参数。见下例:

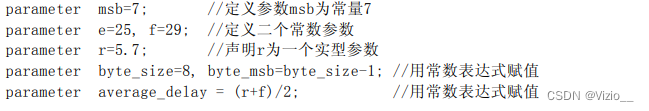

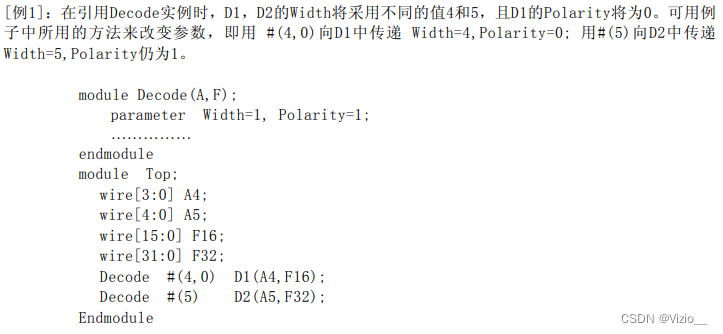

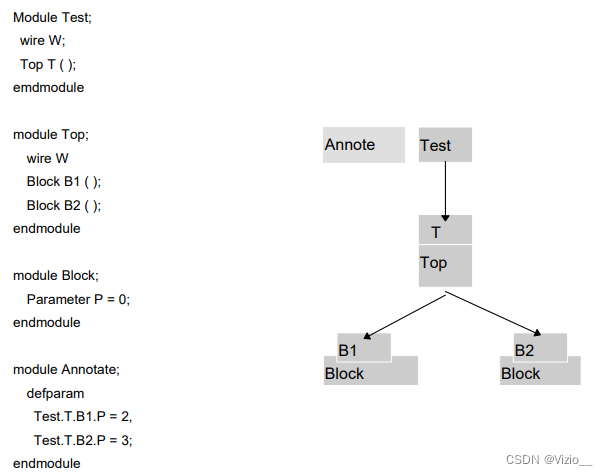

参数型常数经常用于定义延迟时间和变量宽度。在模块或实例引用时可通过参数传递改变在被引用模 块或实例中已定义的参数。下面将通过两个例子进一步说明在层次调用的电路中改变参数常用的一些用法:

变量:

网络数据类型表示结构实体(例如门)之间的物理连接。网络类型的变量不能储存值,而且它必需受到 驱动器(例如门或连续赋值语句,assign)的驱动。如果没有驱动器连接到网络类型的变量上,则该变 量就是高阻的,即其值为z。常用的网络数据类型包括wire型和tri型。这两种变量都是用于连接器件 单元,它们具有相同的语法格式和功能。之所以提供这两种名字来表达相同的概念是为了与模型中所 使用的变量的实际情况相一致。wire型变量通常是用来表示单个门驱动或连续赋值语句驱动的网络型 数据,tri型变量则用来表示多驱动器驱动的网络型数据。如果wire型或tri型变量没有定义逻辑强度 (logic strength),在多驱动源的情况下,逻辑值会发生冲突从而产生不确定值。

wire型:

wire型数据常用来表示用于以assign关键字指定的组合逻辑信号。Verilog程序模块中输入输出信号 类型缺省时自动定义为wire型。wire型信号可以用作任何方程式的输入,也可以用作“assign”语句 或实例元件的输出。

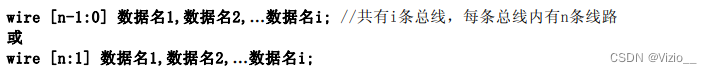

wire型信号的格式同reg型信号的很类似。其格式如下:

wire是wire型数据的确认符,[n-1:0]和[n:1]代表该数据的位宽,即该数据有几位。最后跟着的是 数据的名字。如果一次定义多个数据,数据名之间用逗号隔开。声明语句的最后要用分号表示语句结 束。看下面的几个例子。

reg型:

寄存器是数据储存单元的抽象。寄存器数据类型的关键字是reg.通过赋值语句可以改变寄存器储存的 值,其作用与改变触发器储存的值相当。Verilog HDL语言提供了功能强大的结构语句使设计者能有 效地控制是否执行这些赋值语句。这些控制结构用来描述硬件触发条件,例如时钟的上升沿和多路器 的选通信号。在行为模块介绍这一节中我们还要详细地介绍这些控制结构。reg类型数据的缺省初始 值为不定值,x。

reg型数据常用来表示用于“always”模块内的指定信号,常代表触发器。通常,在设计中要由“always” 块通过使用行为描述语句来表达逻辑关系。在“always”块内被赋值的每一个信号都必须定义成reg 型。

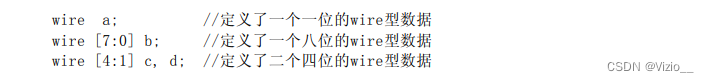

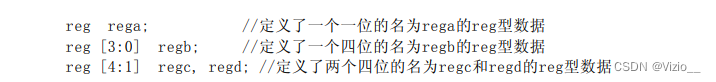

reg型数据的格式如下:

reg是reg型数据的确认标识符,[n-1:0]和[n:1]代表该数据的位宽,即该数据有几位(bit)。最后 跟着的是数据的名字。如果一次定义多个数据,数据名之间用逗号隔开。声明语句的最后要用分号表 示语句结束。看下面的几个例子:

对于reg型数据,其赋值语句的作用就象改变一组触发器的存储单元的值。在Verilog中有许多构造 (construct)用来控制何时或是否执行这些赋值语句。这些控制构造可用来描述硬件触发器的各种具 体情况,如触发条件用时钟的上升沿等,或用来描述具体判断逻辑的细节,如各种多路选择器。reg 型数据的缺省初始值是不定值。reg型数据可以赋正值,也可以赋负值。但当一个reg型数据是一个表 达式中的操作数时,它的值被当作是无符号值,即正值。例如:当一个四位的寄存器用作表达式中的 操作数时,如果开始寄存器被赋以值-1,则在表达式中进行运算时其值被认为是+15。

reg型只表示被定义的信号将用在“always”块内,理解这一点很重要。并不是说reg型信号一定是寄 存器或触发器的输出。虽然reg型信号常常是寄存器或触发器的输出,但并不一定总是这样。

memory型:

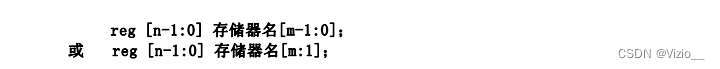

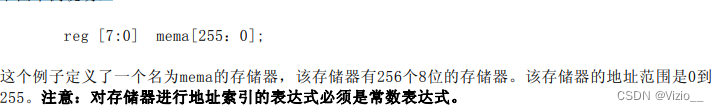

Verilog HDL通过对reg型变量建立数组来对存储器建模,可以描述RAM型存储器,ROM存储器和reg文 件。数组中的每一个单元通过一个数组索引进行寻址。在Verilog语言中没有多维数组存在。 memory 型数据是通过扩展reg型数据的地址范围来生成的。其格式如下:

在这里,reg[n-1:0]定义了存储器中每一个存储单元的大小,即该存储单元是一个n位的寄存器。存 储器名后的[m-1:0]或[m:1]则定义了该存储器中有多少个这样的寄存器。最后用分号结束定义语句。 下面举例说明:

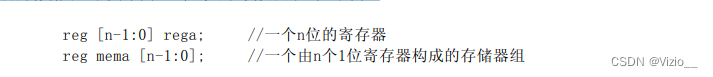

另外,在同一个数据类型声明语句里,可以同时定义存储器型数据和reg型数据。见下例:

尽管memory型数据和reg型数据的定义格式很相似,但要注意其不同之处。如一个由n个1位寄存器构 成的存储器组是不同于一个n位的寄存器的。见下例:

一个n位的寄存器可以在一条赋值语句里进行赋值,而一个完整的存储器则不行。见下例:

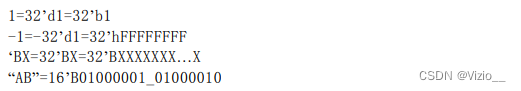

如果想对memory中的存储单元进行读写操作,必须指定该单元在存储器中的地址。下面的写法是正确的。

![]()

进行寻址的地址索引可以是表达式,这样就可以对存储器中的不同单元进行操作。表达式的值可以取决于电路中其它的寄存器的值。例如可以用一个加法计数器来做RAM的地址索引。

943

943

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?