对FPGA设计而言如果想速度更快则应当努力减少路径上LUT的个数,而不是逻辑级数。如果想面积更小则应当努力减少LUT的个数而不是逻辑门数。

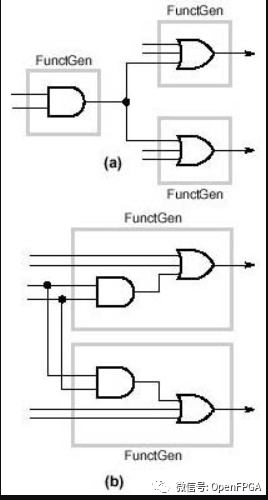

如下图:

采用图a结构,我们知道一个LUT只有一个输出,因此前面的2输入与门要占用一个LUT 后面的2个三输入或门要各占用一个LUT 总共占用3个LUT LUT级数是2级。

采用图b结构,其实现结果等效于图a结构,虽然增加了一个2输入与门并且逻辑级数与图a一样也是2级但我们根据LUT特点它只占用2个LUT:2输入与门和3输入或门由一个LUT实现LUT级数只有1级,这就是一个门数增加逻辑级数未变但资源占用减少速度更快典型案例

NOW现在行动!

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

| 文件名 | 主标题 | 内容简单介绍 | 是否有中文版 | |

| UG476 | 7 Series FPGAs GTX/GTH Transceivers | GTX和GTH介绍,PCIe、serdes等学习必备 | 否 | |

| UG471 | 7 Series FPGAs SelectIO Resources | 描述 7 系列 FPGA 中可用的 SelectIO资源。 | 否 | |

| UG1114 | PetaLinux Tools Documentaton | PetaLinux 工具文档 参考指南 | 是,V2019.2 | |

| UG949 | UltraFAST 设计方法指南(适用于 Vivado Design Suite) | 赛灵思® UltraFast™ 设计方法是用于为当今器件优化设计进程的一套最佳实践。这些设计的规模与复杂性需要执行特定的步骤与设计任务,从而确保设计每一个阶段的成功开展。依照这些步骤,并遵循最佳实践,将帮助您以最快的速度和最高的效率实现期望的设计目标 | 是,V2018.1 | |

| IP手册 | pg057 | FIFO Generator | FIFO生成器IP使用手册 | 否 |

| pg104 | Complex Multiplier | 复数乘法器IP使用手册 | 否 | |

| pg122 | RAM-Based Shift Register | 移位寄存器IP使用手册 | 否 |

推荐阅读

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程

Github 上有哪些优秀的 VHDL/Verilog/FPGA 项目

高速串行通信常用的编码方式-8b/10b编码/解码

Verilog计时(微秒、毫秒和秒)脉冲的产生及同步整形电路

再说System Verilog 与 Verilog 的关系

2981

2981

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?