`timescale 1ns/1ns

module encoder_83(

input [7:0] I ,

input EI ,

output wire [2:0] Y ,

output wire GS ,

output wire EO

);

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);

assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];

assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

//assign GS = EI&(| I);

endmodule

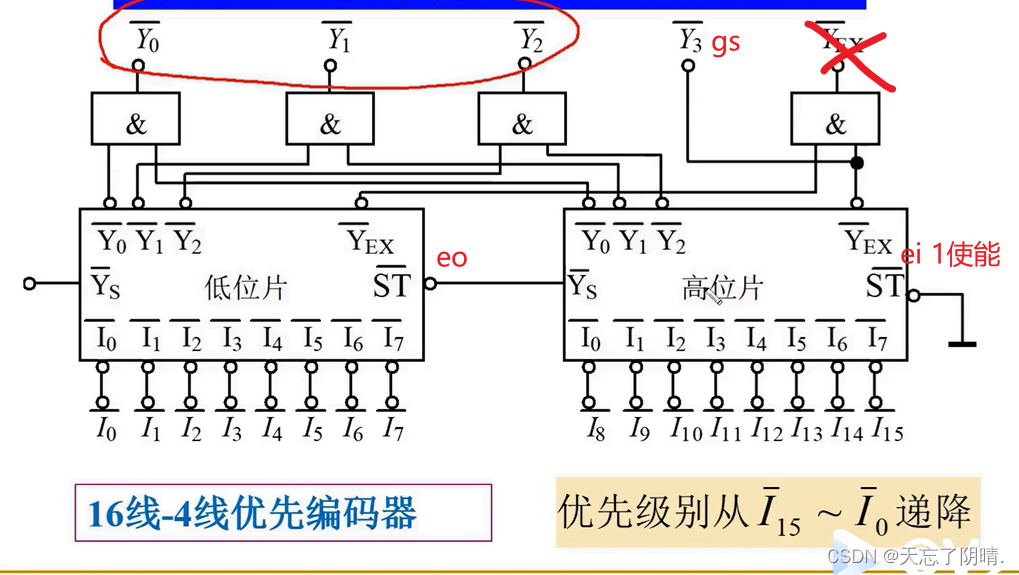

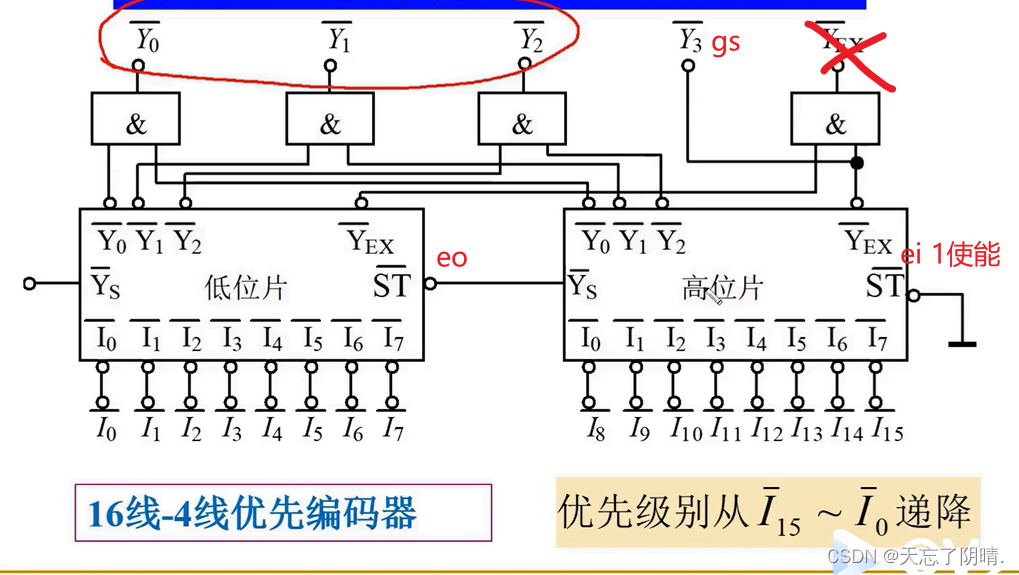

module encoder_164(

input [15:0] A ,

input EI ,

output wire [3:0] L ,

output wire GS ,

output wire EO

);

wire EO1;

wire EO2;

wire [2:0] Y1;

wire [2:0] Y2;

wire GS1;

wire GS2;

encoder_83 u1(//高位片

. I (A[15:8]),

. EI (EI),

. Y (Y1),

. GS (GS1),

. EO (EO1)

);

encoder_83 u2(//低位片

. I (A[7:0]),

. EI (EO1),

. Y (Y2),

. GS (GS2),

. EO (EO)

);

assign L[3] = GS1;

assign L[2] = Y1[2] | Y2[2];

assign L[1] = Y1[1] | Y2[1];

assign L[0] = Y1[0] | Y2[0];

assign GS= GS1 | GS2;

endmodule

//默认是1 所以想与

//EI是否使能

//EO判断是否为0

//GS为是否按下按键

//注意assign的写法

//高位片时8+x

//低位片 时x

4686

4686

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?