AXI Block RAM (BRAM) 控制器是一个软件IP核,专为与Xilinx Vivado设计套件一起使用而设计。该IP核被设计为AXI端点从设备IP,用于与AXI互联和系统主设备集成,以便与本地块RAM进行通信。

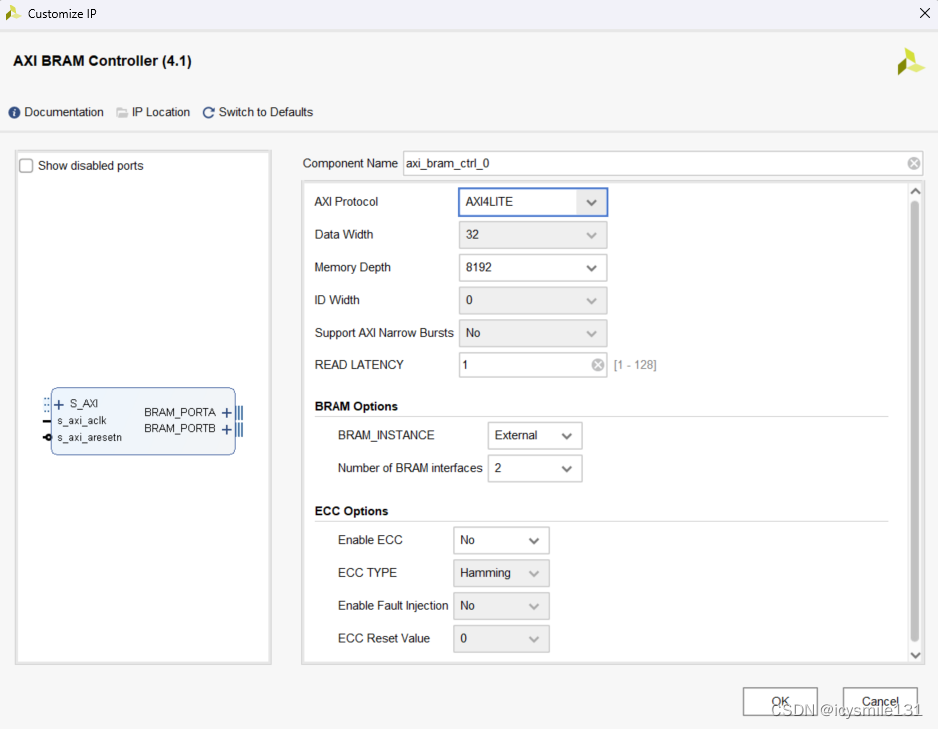

AXI BRAM控制器IP核可以通过设置设计参数C_S_AXI_PROTOCOL = AXI4LITE来配置为简化版的IP核。在这种配置下,AXI BRAM控制器可以配置为与单端口或双端口BRAM接口。在单端口模式下,对块RAM的所有仲裁都在AXI写地址(AW)和读地址(AR)通道上进行。IP核中一次只允许一个活动操作。当AXI BRAM控制器的AW和AR通道接口同时接收到ARVALID和AWVALID信号的断言时,会优先处理读通道,以确保AXI BRAM控制器与任何AXI4-Lite主设备兼容。

当AXI BRAM控制器在包含AXI互联IP的系统拓扑中创建时,AXI互联确保ARVALID和AWVALID不会同时断言,并且AXI互联处理写和读通道之间的仲裁。AXI互联通过在构建过程中复制ARADDR和AWADDR信号来优化AXI BRAM控制器核心。

AXI4-Lite BRAM控制器设计为最小限度地使用FPGA资源。仅使用最少的寄存器,这些寄存器仅用于支持根据标准将寄存器输出到AXI4-Lite接口。

1 AXI4-Lite Single Write

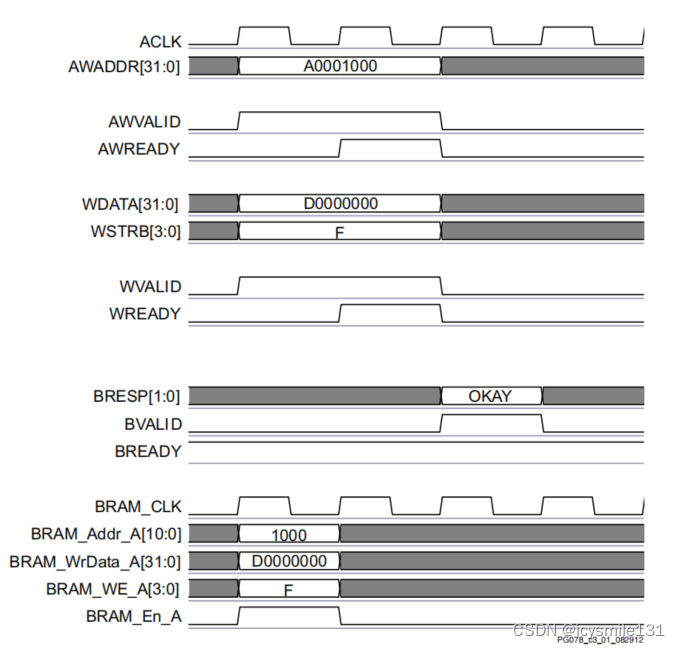

在AXI4-Lite接口中,对于单写操作(AXI4-Lite Single Write),图1展示了AXI4-Lite接口在AW(Address Write)和W(Write Data)通道上的时序,并且假设在AXI AR(Address Read)和R(Read Data)通道上没有有效的传输活动(因为读操作与写操作是分开的)。

图1 AXI4-Lite 写时序

(1)地址写通道(AW)

● 主设备(Master)在AWVALID信号上发送有效信号,指示地址和写保护信息(如果有的话)是有效的。

● 主设备在AWADDR信号上发送目标内存地址。

●(可选)主设备可以在AWPROT信号上发送写保护信息(如果AXI4-Lite接口支持写保护)。

● 从设备(Slave,即AXI BRAM控制器)在AWREADY信号上发送有效信号,表示它已准备好接收下一个地址或开始写入操作。

(2)写数据通道(W)

● 一旦AW通道上的传输完成,主设备可以在WVALID信号上发送有效信号,并在WDATA信号上发送数据。

●(可选)主设备可以在WSTRB信号上发送字节使能信号,以指示WDATA中的哪些字节是有效的。

●(可选)主设备可以在WLAST信号上发送有效信号,以指示这是当前写突发(burst)的最后一个数据项。

● 从设备在WREADY信号上发送有效信号,表示它已准备好接收下一个数据项或完成写操作。

(3)写响应通道(B)

● 写操作完成后,从设备通过BVALID信号发送写响应有效信号,并在BRESP信号上发送响应状态(通常是OKAY表示成功)。

● 主设备在BREADY信号上发送有效信号,表示它已准备好接收写响应。

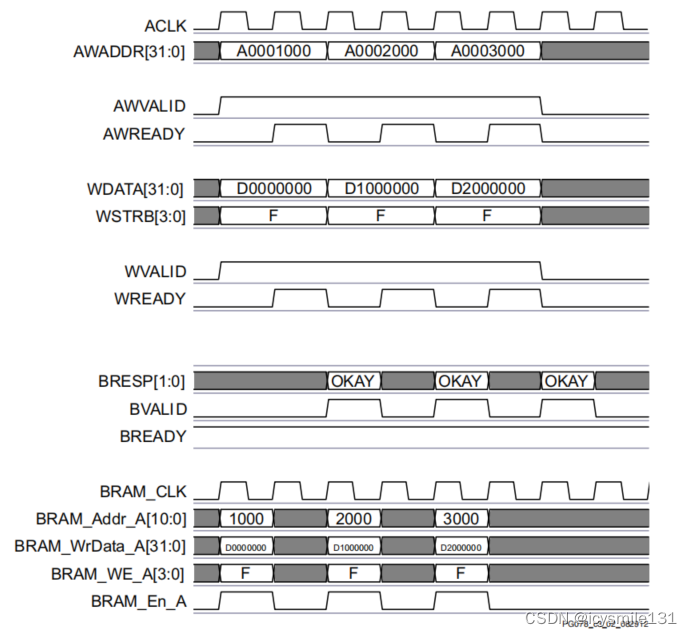

2 AXI4-Lite Multiple Write

当AXI4-Lite BRAM控制器能够连续接受单个写操作(Single Write Operations)时,这通常意味着它支持一种写突发(Write Burst)模式,即使这些写操作在逻辑上是连续的单个写事务(Single Write Transactions)。。

在AXI4-Lite协议中,写突发(Burst)的概念可能不像在AXI4或AXI Stream等更高级协议中那样明确定义,因为AXI4-Lite是一个轻量级的接口,主要关注于简单的读写操作。然而,连续的单个写操作仍然可以通过连续发送AW(Address Write)和W(Write Data)通道上的数据包来实现。

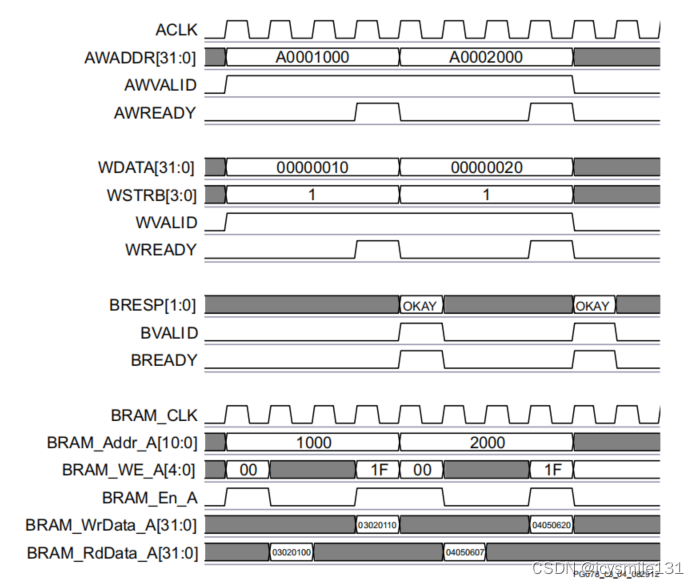

如图2所示。

图2 AXI4-Lite多个写事务时序

(1)第一个写事务

● 主设备(Master)发送一个AW通道的数据包,其中包含要写入的内存地址和其他控制信息(如写保护)。接着,主设备在W通道上发送写数据(WDATA),并可能包括字节使能(WSTRB)和最后一个数据(WLAST)的标志。

● BRAM控制器(Slave)在AWREADY和WREADY信号上发送有效信号,以确认接收到了地址和数据。

● 当写操作完成后,BRAM控制器在B通道上发送写响应(BRESP),主设备在BREADY信号上发送有效信号以确认接收到了响应。

(2)第二个及后续写事务

一旦主设备接收到第一个写事务的响应,它可以立即开始下一个写事务,无需等待前一个事务完全完成。

重复上述步骤,发送新的AW、W和B通道的数据包,以进行下一个内存地址的写入操作。

在连续进行多个写事务时,需要注意以下几点:

- 流水线操作:AXI协议支持流水线操作,这意味着主设备可以在等待前一个事务的响应时开始下一个事务。这可以显著提高数据传输的吞吐量。

- 地址和控制信息的正确性:每个写事务都需要正确的地址和控制信息。确保在发送新的AW通道数据包之前,已经正确处理了前一个事务的响应。

- 数据一致性和同步:由于写事务是独立的,因此需要确保在多个事务中写入的数据保持一致性和同步。这可能需要在应用层或更高层协议中进行额外的管理。

总之,AXI4-Lite接口支持多个连续的写事务,通过流水线操作可以提高数据传输的效率和吞吐量。在设计和实现时,需要注意地址、控制信息的正确性以及数据的一致性和同步。

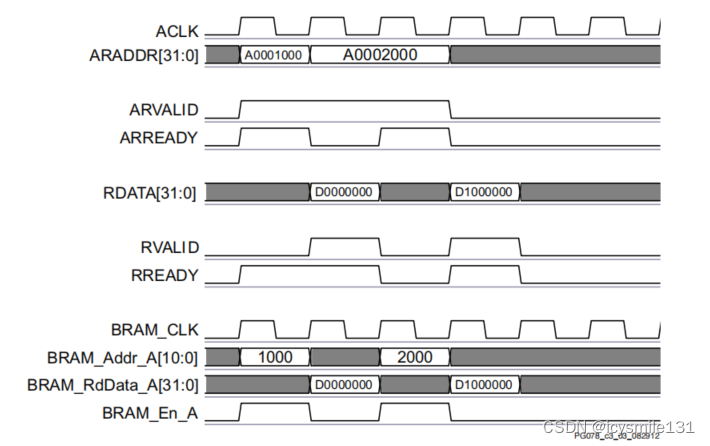

3 AXI4-Lite Single Read

对于AXI4-Lite的单读操作,其数据读取路径的时序在图3中有所展示。这张图描述了AXI4-Lite事务中控制器和BRAM接口上多个读请求操作的时序。

图3 AXI4-Lite读时序

(1)读地址通道(AR)

● 当主设备(Master)想要从BRAM读取数据时,它会首先通过读地址通道(AR)发送读请求。这包括将ARVALID信号置高,表示地址有效,并发送目标内存地址(ARADDR)。

● 从设备(Slave,即BRAM控制器)在接收到ARVALID信号后,如果它准备好接收读请求,会将ARREADY信号置高。

● 一旦ARVALID和ARREADY信号同时为高,主设备会发送具体的地址信息(ARADDR),并在发送完地址后,将ARVALID信号置低。

(2)读数据通道(R)

● 当从设备准备好发送读取的数据时,它会将RVALID信号置高,并在RDATA信号上发送实际的数据。

● 主设备在检测到RVALID信号为高时,会读取RDATA信号上的数据,并将RREADY信号置高以确认数据的接收。

● 如果这是读取突发(Burst Read)中的最后一个数据,从设备会将RLAST信号置高,以指示主设备该突发读取已完成。

4 AXI4-Lite Write with ECC

AXI4-Lite在启用了ECC(错误检查和纠正)的情境下进行写操作时,涉及一个读-修改-写(RMW)的序列,如图4所示。当C_ECC(ECC使能位)设置为1时,AXI4-Lite接口上的写传输会采用这种RMW序列。由于AXI4-Lite BRAM控制器为了节省资源,不会对AWADDR(地址写)和WDATA(写数据)进行寄存器操作,因此AWREADY(地址接收有效)和WREADY(数据写入有效)的输出标志断言会被延迟,直到RMW序列完成。

图4 带ECC的AXI-Lite写事务

在RMW序列中,以下是主要步骤:

读操作:首先,控制器会读取目标地址的数据。这是因为ECC需要在写入新数据之前检查原始数据,以便在必要时进行错误纠正。

修改操作:一旦读取了原始数据,控制器就会根据需要进行修改。这包括应用新的数据值,并可能进行ECC编码。

写操作:最后,控制器会将修改后的数据(包括新的ECC值)写回到目标地址。

2687

2687

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?