截自Laung-Terng Wang, Yao-Wen Chang, Kwang-Ting (Tim) Cheng - Electronic Design Automation_ Synthesis, Verification, and Test (Systems on Silicon)-Morgan Kaufmann (2009)中的Chapter 10-Floorplanning

关于本章

这章介绍了floorplanning问题,介绍了两种常用的floorplanning方法:模拟退火和解析法。介绍了三种常用的floorplan表示方法,normalized Polished表示,B*树和序列对。此外还介绍了现代布局问题例如soft modules,固定外框约束和大规模设计。

10.1 介绍

10.1.1 floorplanning基础

模拟退火依赖于modules之间的相对位置关系(三种表示方法),而解析法直接考虑绝对位置关系。布局的拓扑表示影响模拟退火过程的复杂度,三种常见的floorplan表示,标准波兰表示法、B*树和序列对,这些表示方法可以有效表示module的几何相对位置(左、右、上和下的关系)。

解析法使用目标函数和一组约束的数学规划来解决布局问题。目标函数建模布局优化问题的成本指标(例如面积和线长),约束用来控制几何和尺寸约束(例如非重叠和长宽比)。这章特别介绍混合整数线性规划(ILP),通过线性成本函数近似建模面积,非重叠和长宽比约束建模成一组线性方程,还用了一种连续增强方法解决ILP的时间复杂度高的问题。

除了最小化芯片面积之外,现代VLSI布局还需要处理很多别的问题例如soft modules、固定外框约束。不像hard module有一个固定尺寸(宽、高),soft module的形状在布局时候决定,虽然面积是固定的,因此需要找到每一个soft module的所需的长宽比来优化布局成本。现代VLSI设计基于固定的die面积的floorplan,就是固定外框约束(fixed-outline),而不是可变的die尺寸,之前的优化面积但是不满足固定外框约束的布局方法学就没啥用了。所以现代布局问题要能解决固定外框约束。

现代设计规模越来越大,高效的布局方法变得越来越重要,布局框架需要考虑设计复杂度大的问题。本章也介绍大规模设计所需的多级框架。

10.1.2 问题陈述

布局问题可以描述为:B={b1,b2,…,bm}为m个矩形模块的集合,每个模块的宽,高和面积用wi,hi和ai表示,1<=i<=m。每个模块可以自由翻转。(xi,yi)表示模块bi左下角的坐标。布局F是给每个模块指定(xi,yi)位置,同时不能存在模块重叠的情况。布局的目标是优化预先定义好的成本指标例如面积(布局的最小外边框矩形面积)和线长(所有模块间互连线的长)的组合。现代布局还可能要考虑可布线性、功耗、热指标等。

10.1.3 布局建模

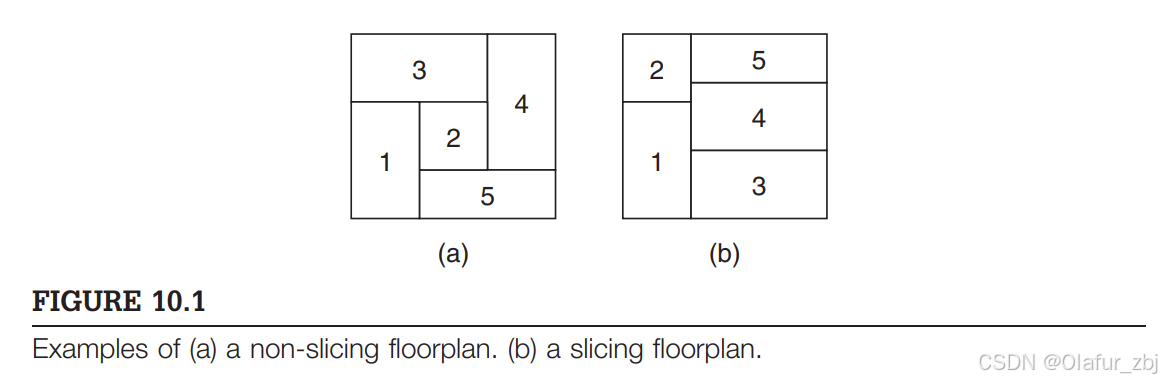

我们将布局分为两类讨论:(1)切片布局(2)非切片布局。切片布局可以通过对画布的重复的水平或垂直切分得到,非切片布局不行。预先给定的每个模块的尺寸必须保持不变。所有模块可以自由翻转,如果翻转意味着它的长和宽交换。

图10.1展示了切片布局和非切片布局。

10.1.3.1 切片布局

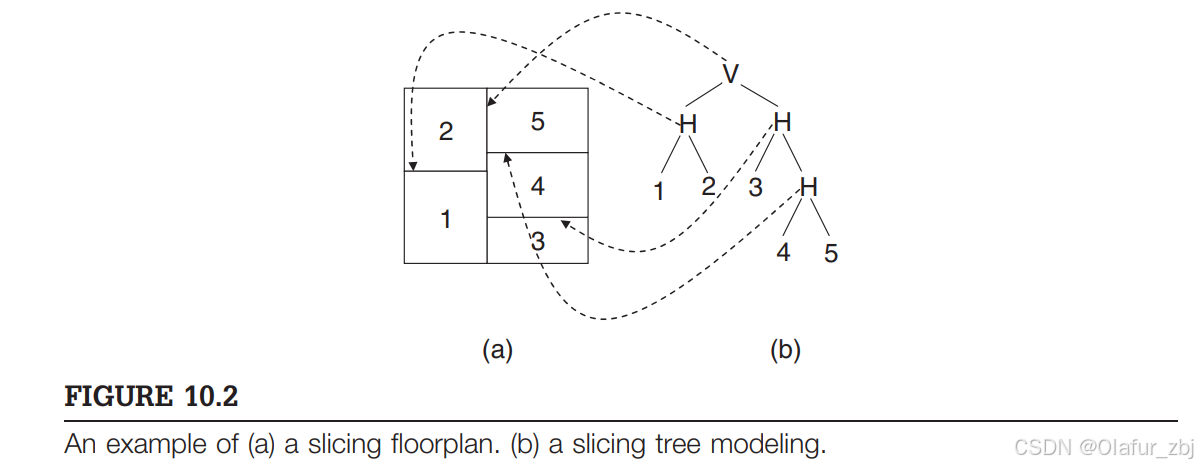

切片布局的基本特性是可以使用二叉树来表示布局。切分树是一个二叉树,模块在叶节点,切分是内部节点。有两种切分,水平H和垂直V。H切分将布局横向切开,左右子节点表示上下的子布局。V同理。

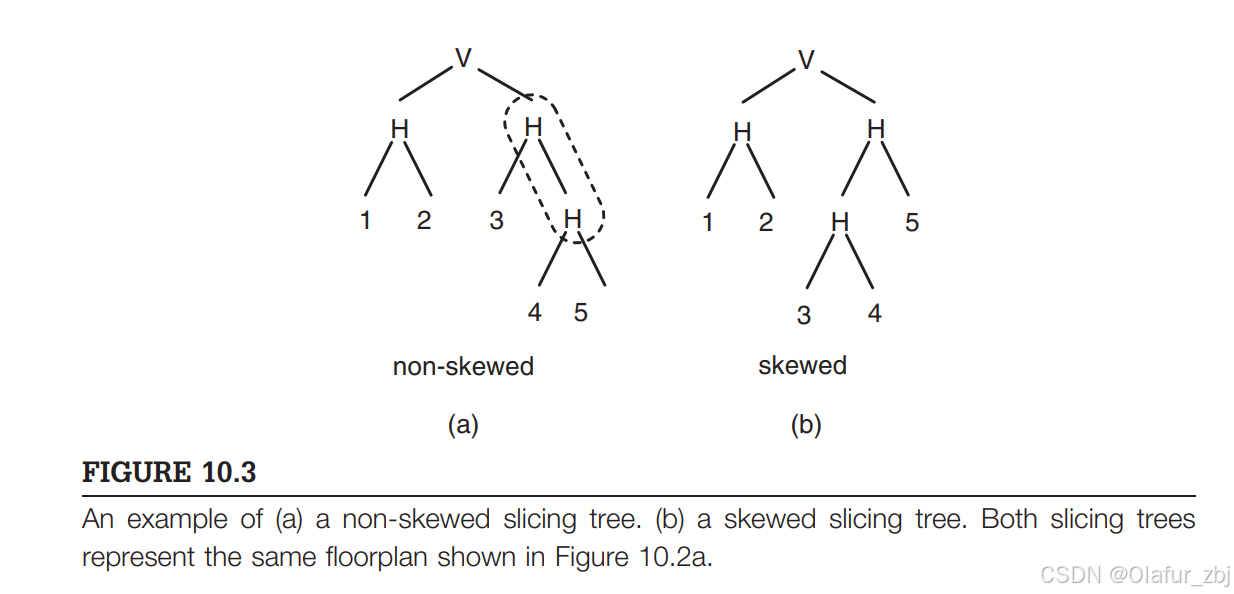

切分布局可能对应多种切分树,因为切的顺序可以不同。这种重复表示会让解空间变得很大,复杂化优化过程。因此,需要将冗余的表示修剪掉。约定相同的切分树,右子节点为空的是偏斜切分树(skewed slicing tree),这样布局的切分树表示就唯一了。

图10.2展示了切分布局和对应的切分树模型,图10.3展示了同一切分布局对应的两种切分树模型,其中右边的是偏斜切分树。

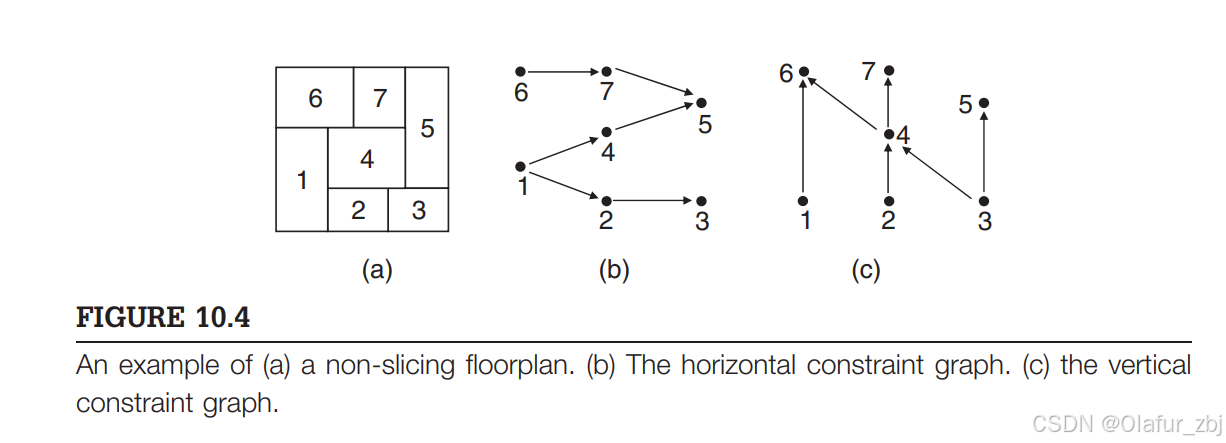

10.1.3.2 非切片布局

非切片布局相比切片布局更通用。但是由于非切片结构,我们不能使用切片树建模,所以用水平约束图(HCG)和垂直约束图(VCG)来表示非切片布局。水平约束图描述了模块水平方向上的相对位置关系,垂直约束图同理。每个节点表示一个模块,如果在HCG图中右从节点A到节点B的边,则表示模块A在模块B的左侧,VCG同理。

图10.4展示了非切片布局和其对应了HCG、VCG表示。

10.1.4 布局优化问题的成本函数

布局的目标是优化预先定义的成本函数,例如布局结果的最小外框矩形的面积。布局面积直接对应芯片硅的成本和良率。面积越大,硅成本越高,良率越低。布局外框矩形中没有被任何模块覆盖的区域为white space或dead space死区。

其他的成本函数项例如线长也需要考虑。更短的线长不仅降低信号延时也利于绕线阶段的线互连。布局的目标函数是组合成本,例如面积加线长。

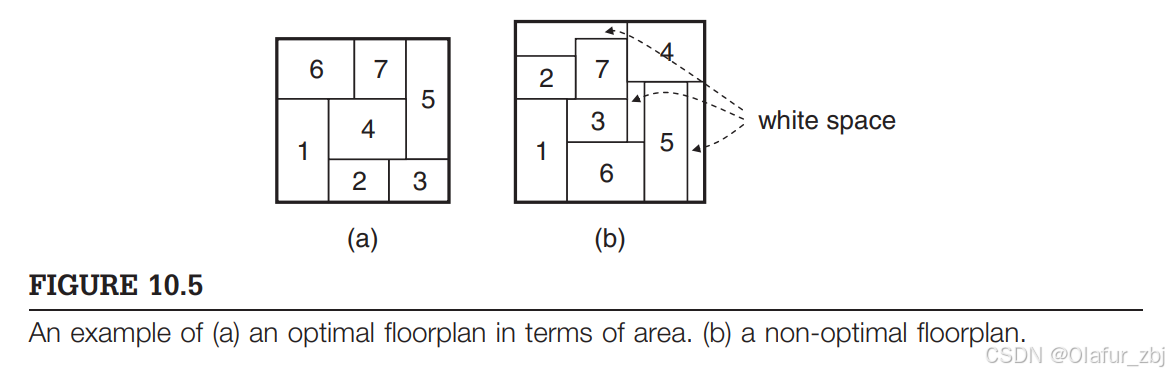

图10.5表示两个布局结果。如果只考虑面积,左边的更优,右边的非最优,死区面积较大,芯片面积更大。

优化目标函数找到最优布局,有两种流行方法,模拟退火和解析法,下面介绍。

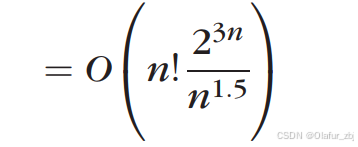

10.2 模拟退火方法

模拟退火可能是最流行的布局优化方法。它可以简单地在目标函数中合入优化目标。用SA来做布局首先要编码不同的布局结果,叫做布局表示,建模了布局中module的相对位置关系。布局表示不仅直接影响所有可行解的解空间,也影响SA优化时的解结构。有三种表示法,标准波兰表示法,B*树和序列对,此外还有一些常见的近期文献中出现的表示法。

10.2.1 模拟退火基础

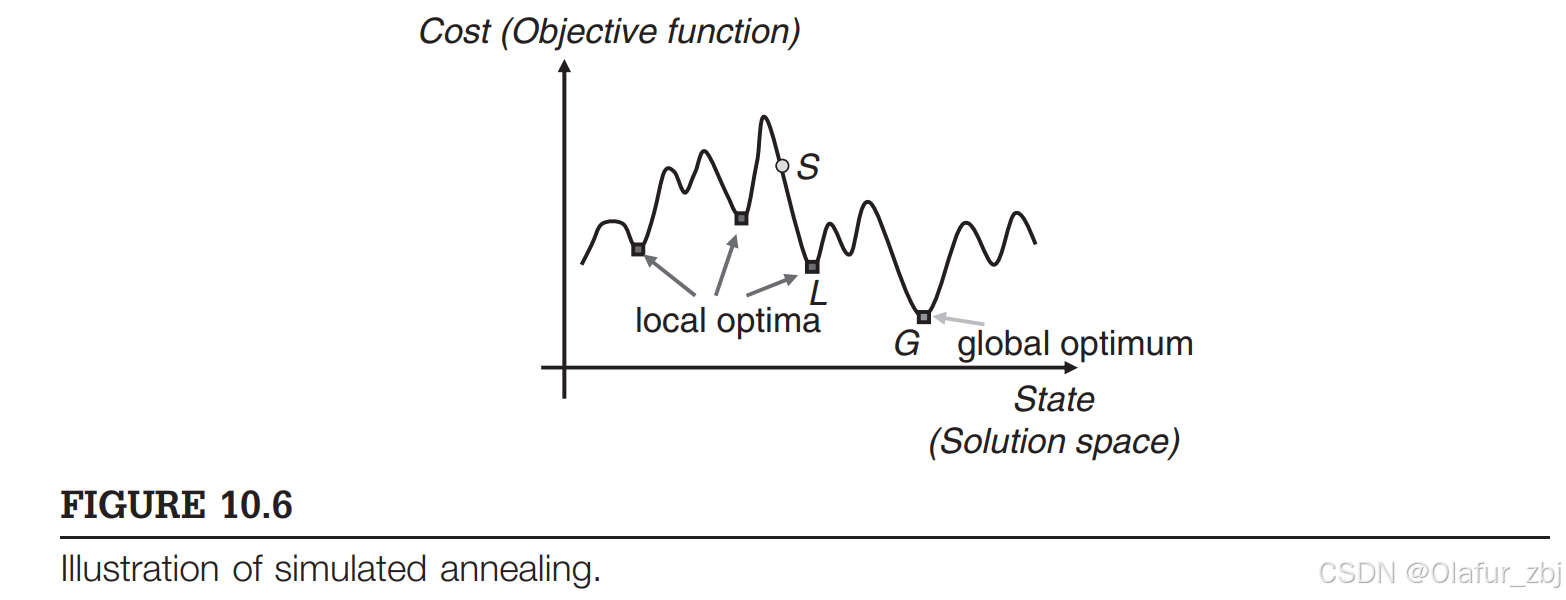

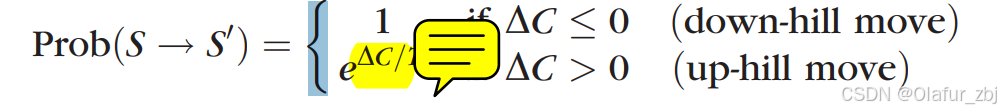

上图展示了模拟退火过程。纵坐标表示布局的成本cost,是布局的函数。基于一个初始解S,SA试图去寻找成本最低的全局最优布局解。贪婪的方法会不停寻找附近低于当前解成本的解指导找不到。这种贪婪的机制很可能陷入到局部最优L。只要陷入到局部最优L,就不会在跳出来因为附近没有比他更低成本的解。SA采用了爬山的方法来跳出局部最优L。基于一个解,SA提供一定的可能性跳出当前解选择附近的成本更高的解。有了这种爬坡能力,SA能够抵达全局最优G不论初始解是啥。接受附近解的概率基于两个因素:(1)上山移动的幅度(2)搜索时间。概率如下:

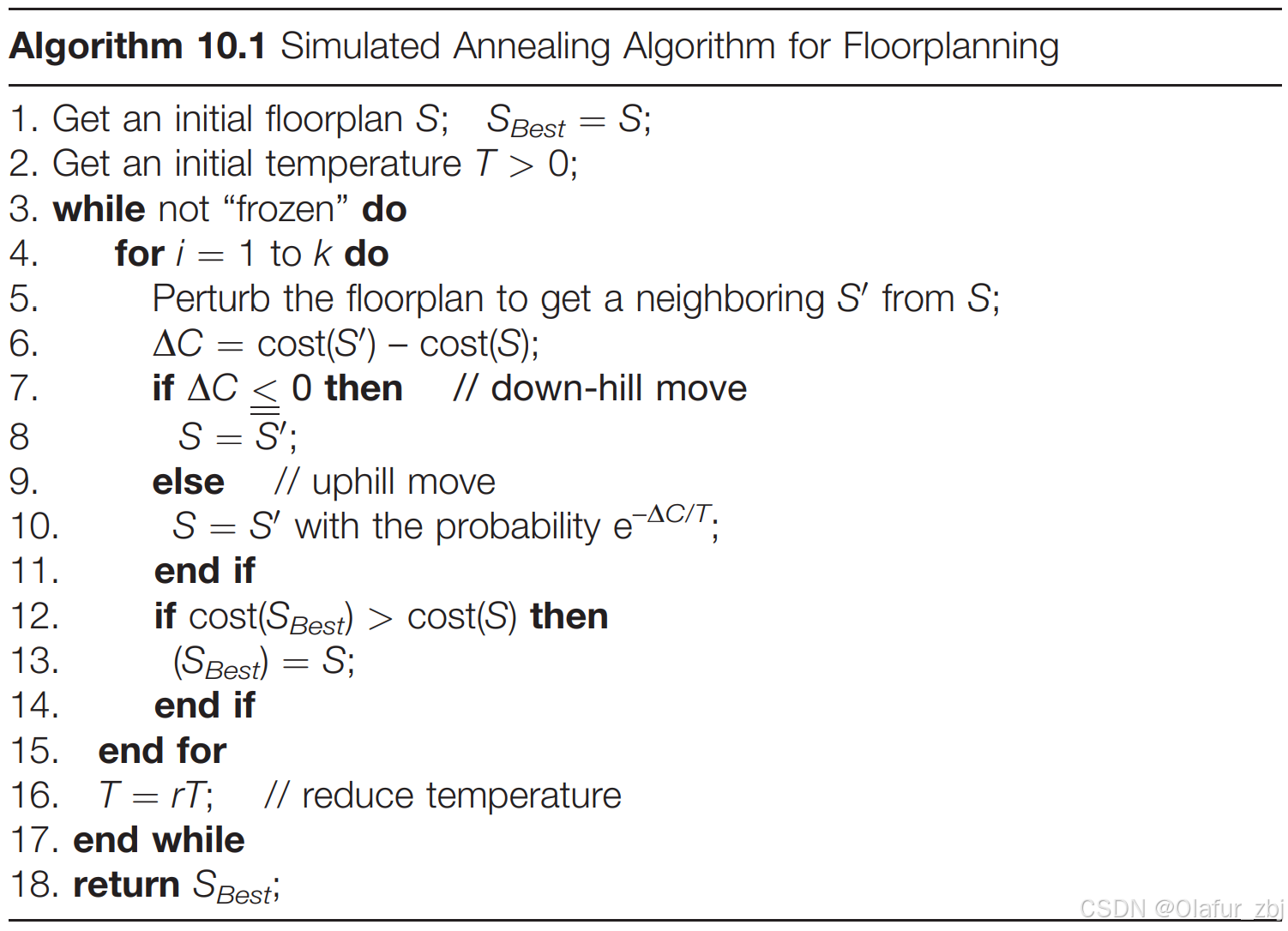

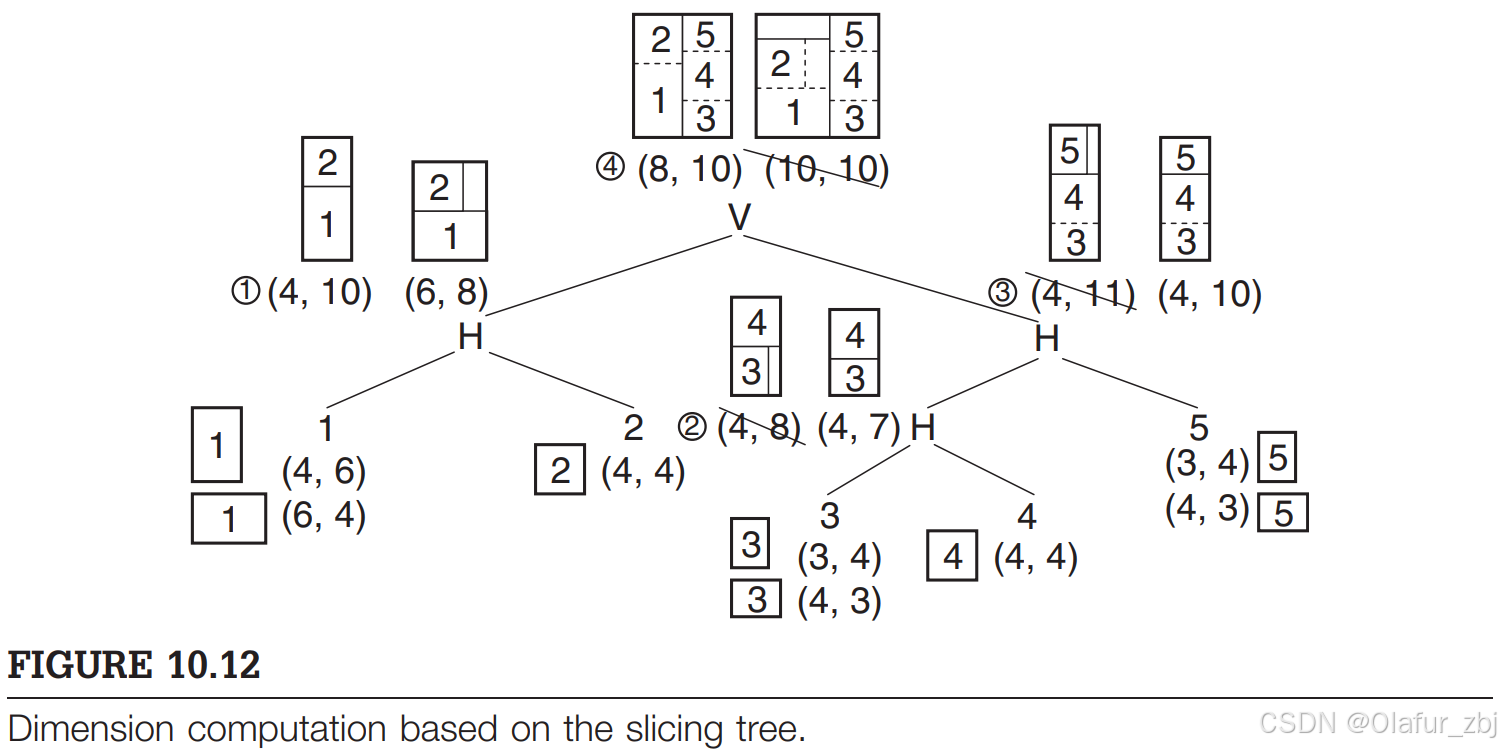

ΔC=cost(S’)-cost(S),T是当前温度。上山概率依赖于cost差和搜索时间(退火温度)。SA过程的温度以固定比例下降,例如0.9.在每个温度下,我们扰动当前的解方案以搜索多个相邻解方案K次,其中K是用户定义的值,并保留迄今为止找到的最佳解决方案。指导温度到达稳态或达成中止条件。很显然,如果成本增加较小或当前温度T较高,则接受较差解决方案的概率更高。实际应用中SA在搜索期望解时很有效,整个过程类比了金属退火过程,这也是SA名字的由来。温度降低,原子排列到稳态,金属成型。算法10.1总结了SA的算法。

SA的基本组成包括(1)解空间(2)邻近结构(3)成本函数(4)退火机制。布局表示定义了解空间和邻近结构,成本函数有优化目标定义,退火机制影响退火过程的温度改变。

SA的基本组成包括(1)解空间(2)邻近结构(3)成本函数(4)退火机制。布局表示定义了解空间和邻近结构,成本函数有优化目标定义,退火机制影响退火过程的温度改变。

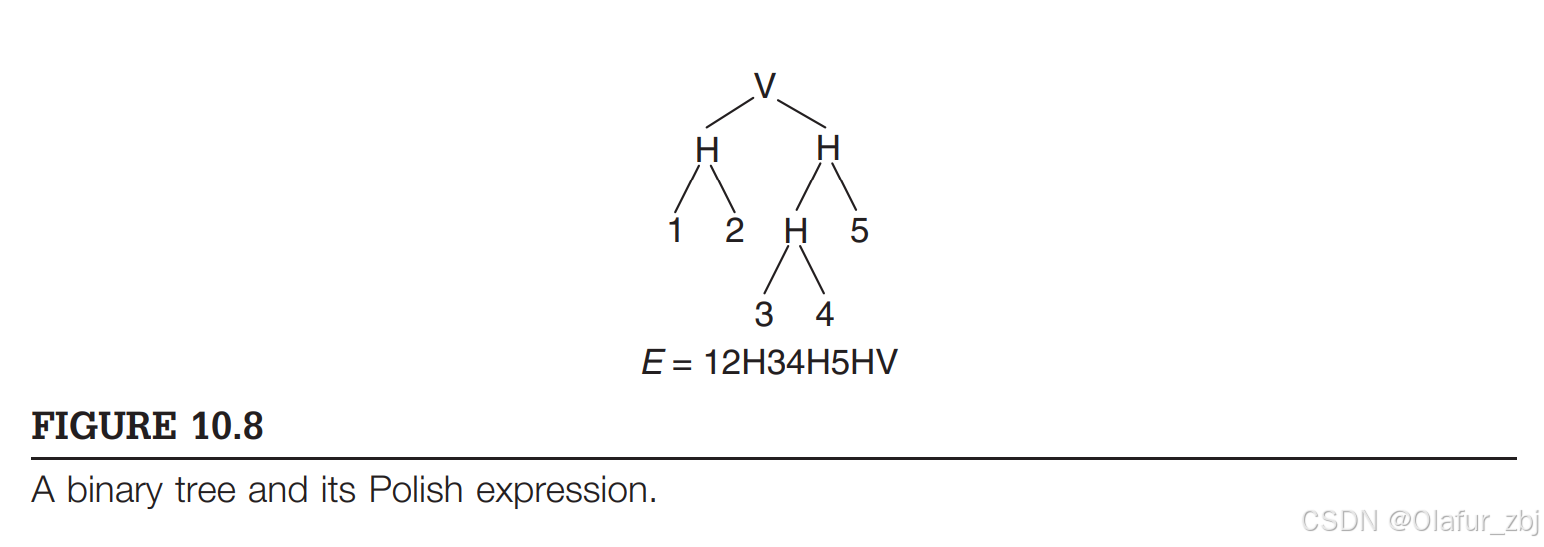

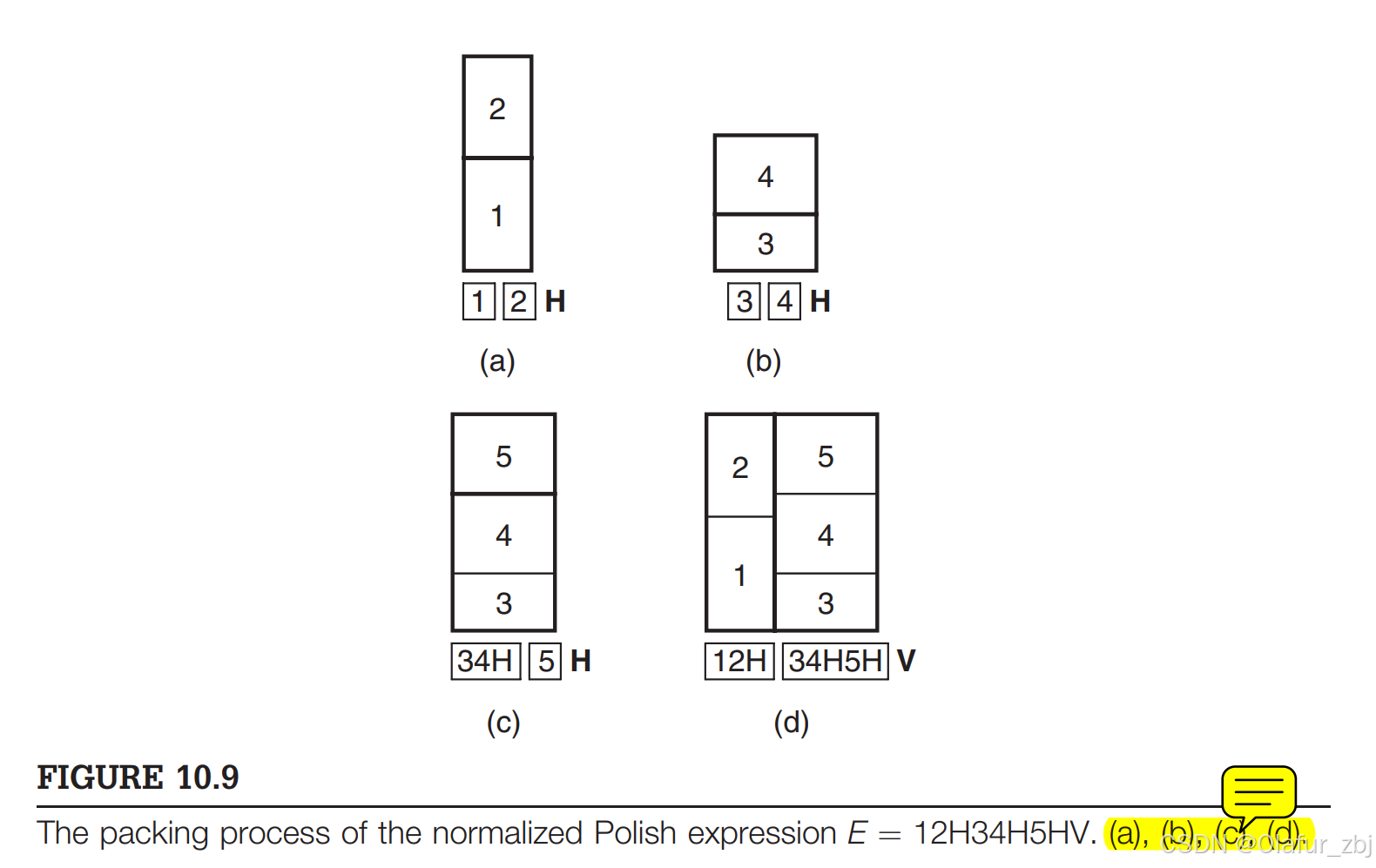

10.2.2 切分布局的标准波兰表示法

这部分跳过,用这种的比较少了。。。

解空间:

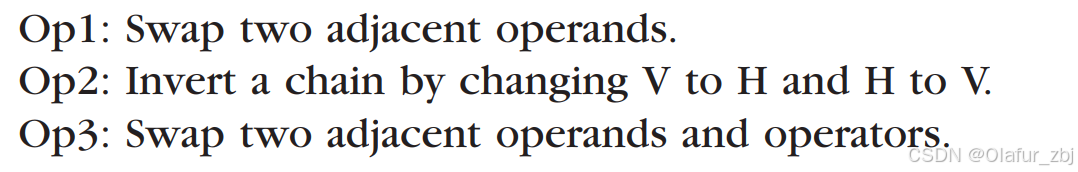

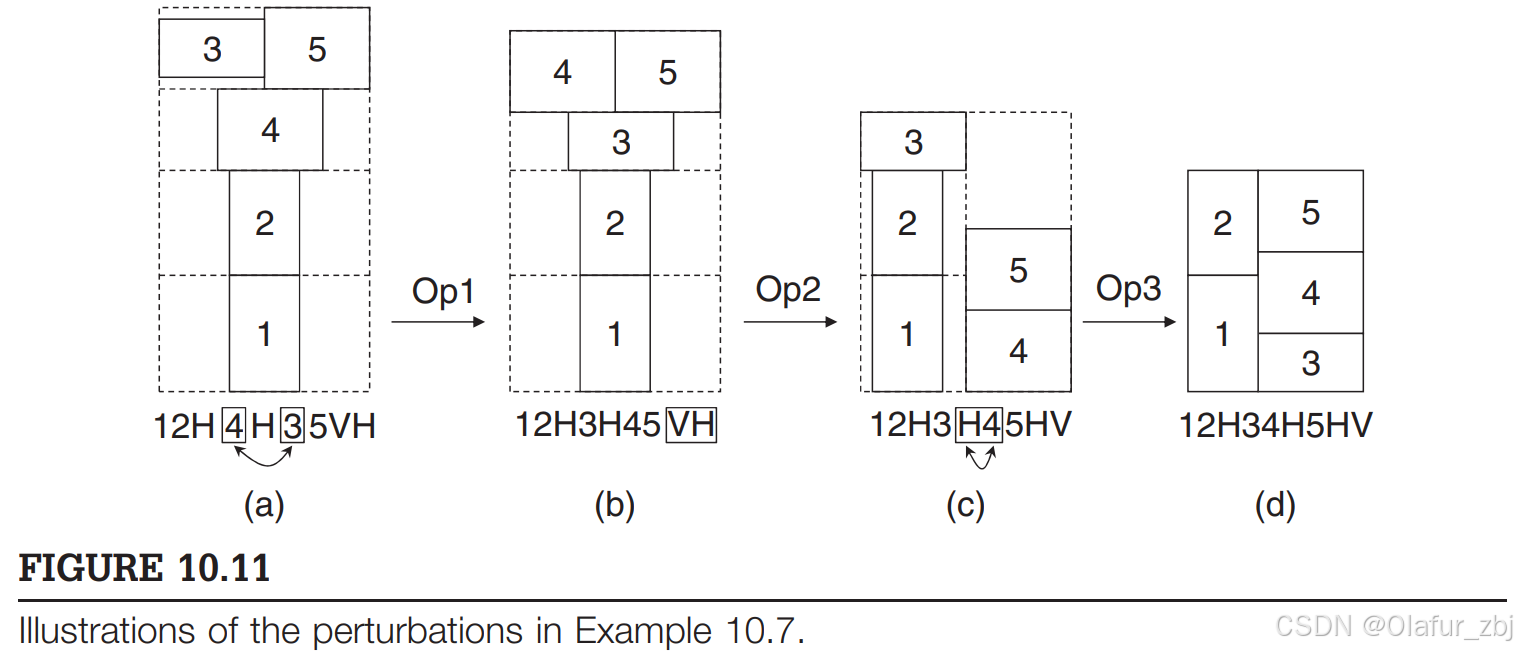

邻近结构(模拟退火的邻近扰动):

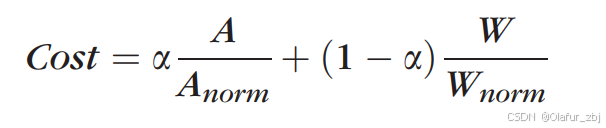

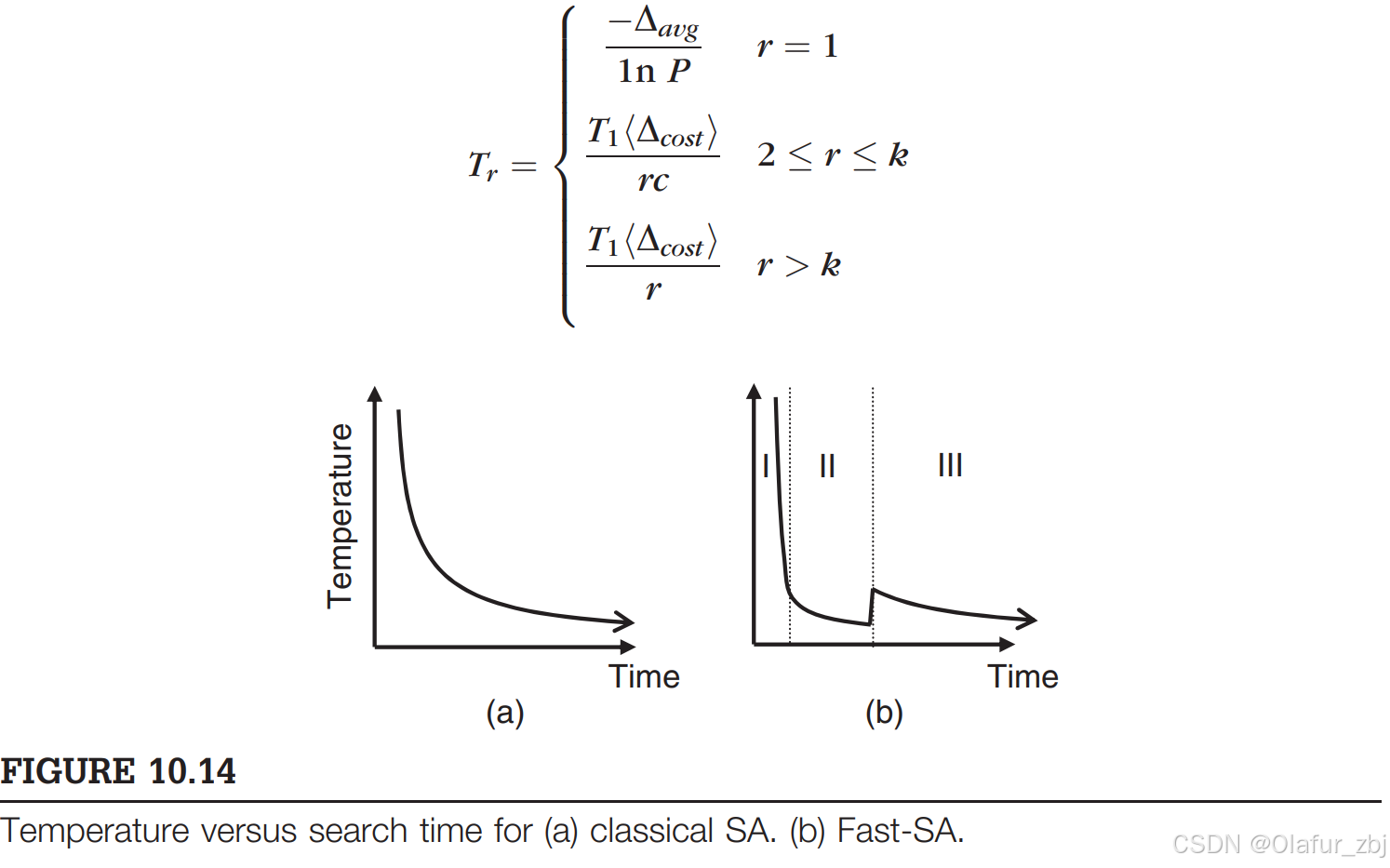

目标函数:

面积和线长。Anorm是平均面积,Wnorm是平均线长,为啥要用平均归一化下???α来控制二者权重。计算Anorm和Wnorm,我们需要对初始标准波兰表示法结果进行扰动,使用三个扰动方式扰动m次,获得m个布局,计算平均面积和平均线长。

线长的计算就使用模块中心位置之间的HPWL

退火机制:

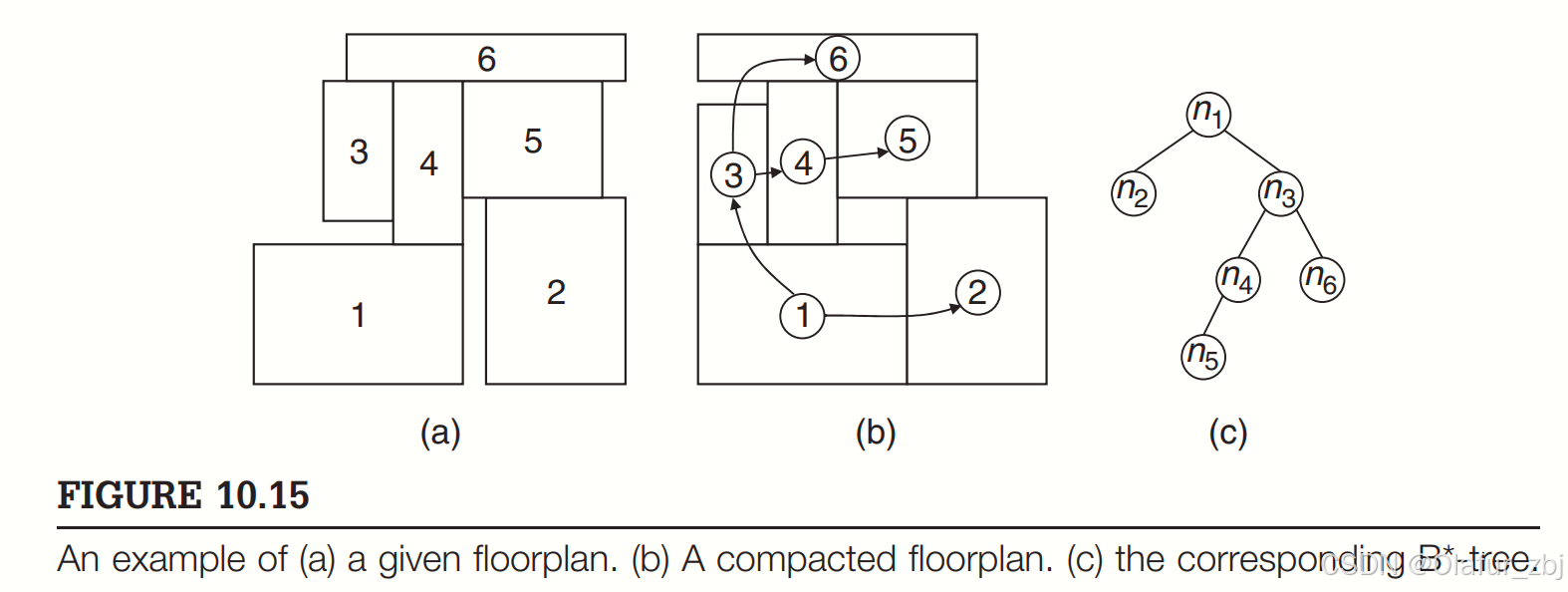

10.2.3 B*树表示的紧凑布局

B树基于有序二叉树来对紧凑的布局进行建模。所谓紧凑,就是左右模块都不能再向平面图的左侧或底部移动,类似于2048游戏所有方块全部移动到左下。因此,面积最优的布局规划时钟对应于某个B树。B树继承了有序二叉树的优良特性,非常容易实现,可以分别在常数、常数和线性时间内执行搜索、插入和删除三种原始树操作。

不像切分布局和其对应的切分树那样,紧凑布局和B树可以唯一对应。换句话说,给定紧凑布局F,我们可以构建一个F对应的B树,并且B树再反构建出的布局就是F。这个良好的唯一对应性质防止冗余表示导致的解空间大的问题,并且保证了面积最优的布局结果可以通过搜索B*树寻找到。

10.2.3.1 通过布局生成B*树

首先将所有模块移动到左下角获得紧凑布局,因为B树只能建模紧凑布局。B树是有序二叉树,根节点对应最下角的module。类似DFS深度优先搜索过程,我们用递归方式构建B*树T:从根节点开始,首先递归构建左子树然后是右子树。Ri表示在右边的与模块i相邻的模块集合。节点ni的左子节点对应Ri里最低的、没有遍历过的模块。节点ni的右子节点表示最低的、跟模块i有相同x坐标的模块。注:这里的最低就是坐标最小,最靠近左下角。

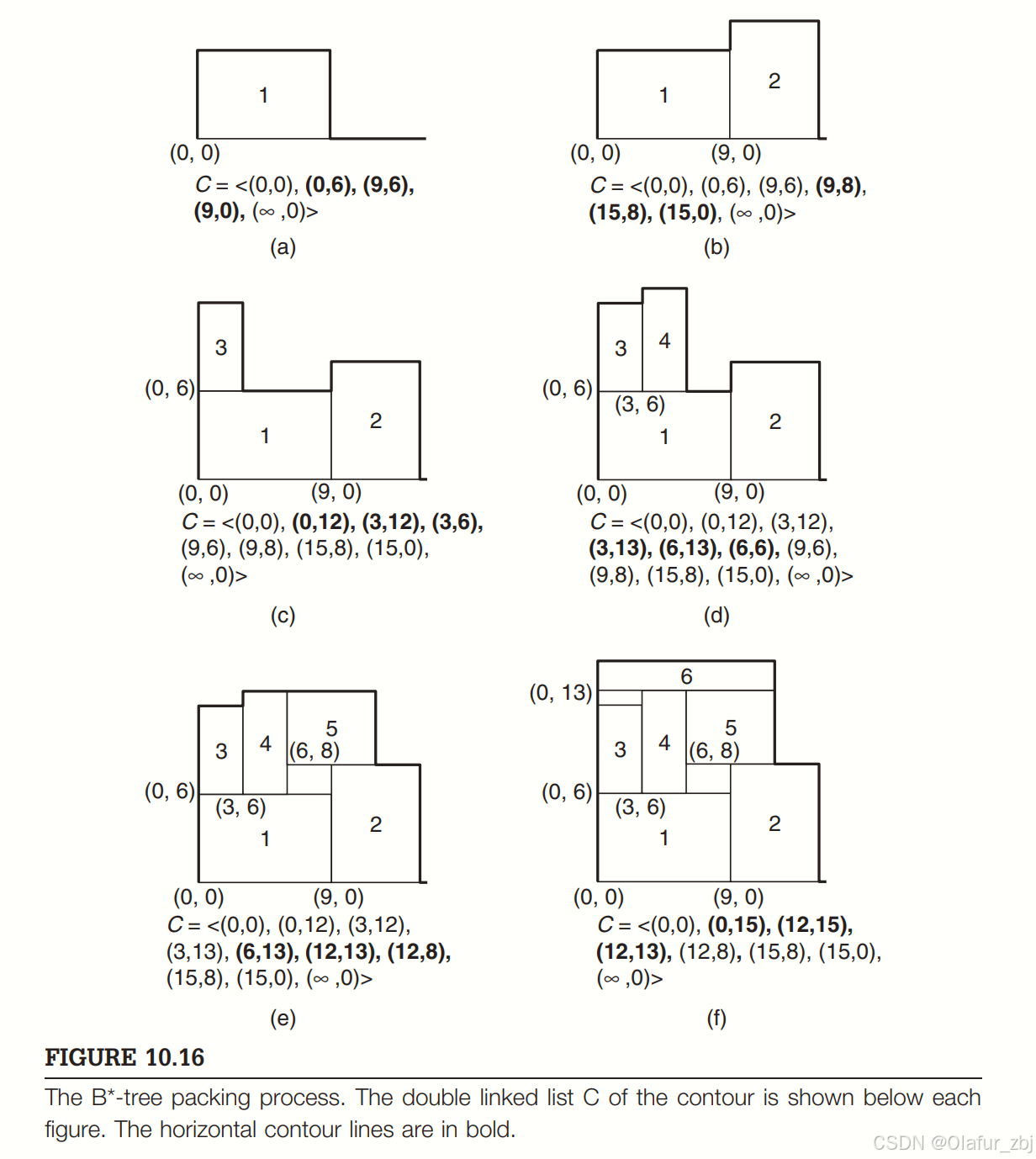

10.2.3.2 通过B*树生成布局

给定一个B树T,根节点表示左下角的模块。如果节点nj是节点ni的左子节点,模块j摆放在右边且贴着模块i,xj=xi+wi。否则,节点nj是节点ni的右子节点,模块j在模块i上方,有相同的x坐标,xj=xi。因此,给定一个B树,所有模块的x坐标可以在线性时间内遍历得到。

为了高效计算B*树的y坐标,轮廓数据结构应运而生。轮廓结构是一个双链表,存储了轮廓曲线在当前压实方向上的坐标。水平轮廓可以减少计算新插入模块的y坐标的运行时间。如果没有轮廓,确定新插入模块的y坐标的运行时间将与模块的数量成线性关系。然而,用过维护轮廓结构,可以在O(1)时间内计算模块y的坐标。

简而言之就是往最左下角贴,然后寻找x跨度内的轮廓线y的最大值,模块的y坐标就是这个y的最大值,如果没有这一步,上图e中的模块5就会和2 overlap在一起。。。

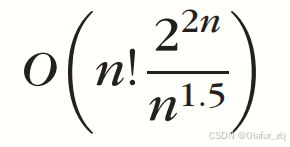

10.2.3.3 解空间

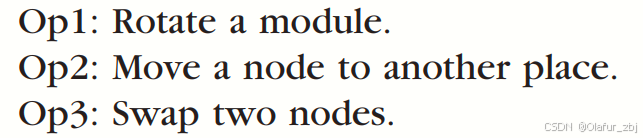

10.2.3.4 邻近结构

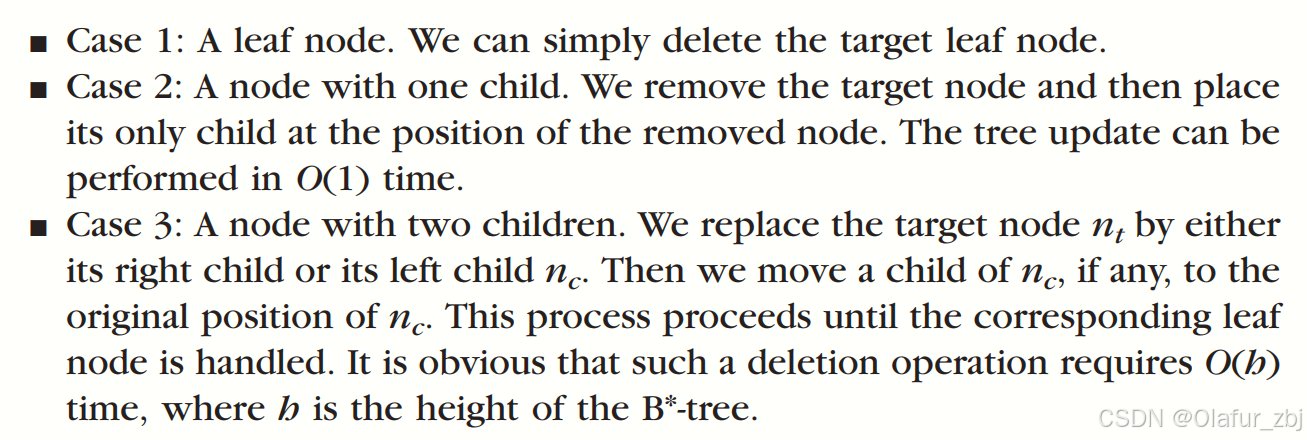

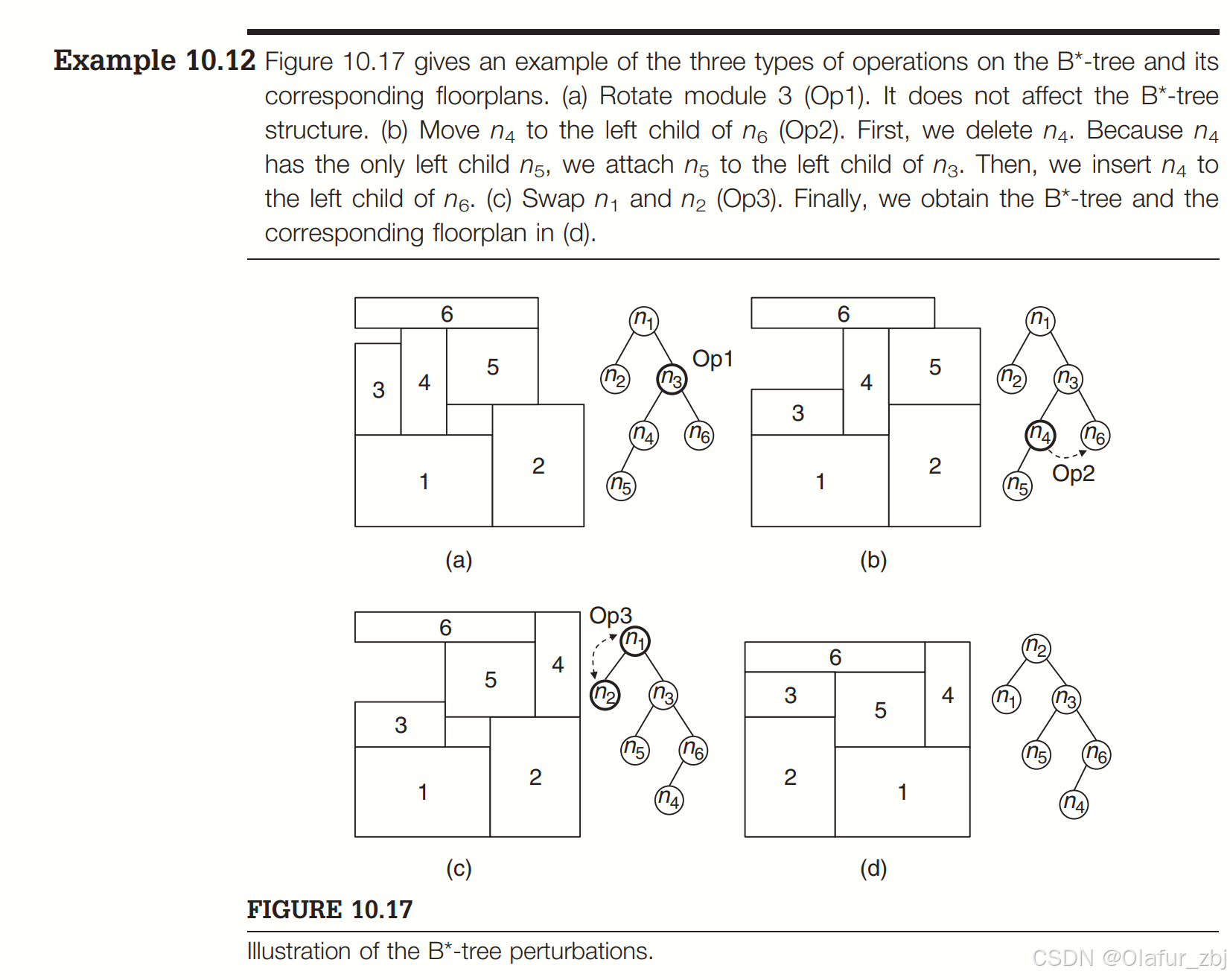

通过以下微扰方式获得邻近解:

op1旋转module不影响B*树结构。op2包含两步,删除和插入。op3交换。删除操作分为三种情况,2和3中操作后模块的相对位置可能会变化,因此需要重建布局。

可以在内部或外部插入新节点:

10.2.3.5 成本函数

同上节中的成本函数。

10.2.3.6 退火机制

传统SA或者Fast SA,同上节。

10.2.4 通用布局的序列对表示法

序列对SP是一种灵活的表示法表示布局结果。序列对包含一对有序的模块名称序列。例如(124536,326145)可以表示六个模块的一种布局。

感兴趣的自己看吧,序列对现在用的也少了。。。

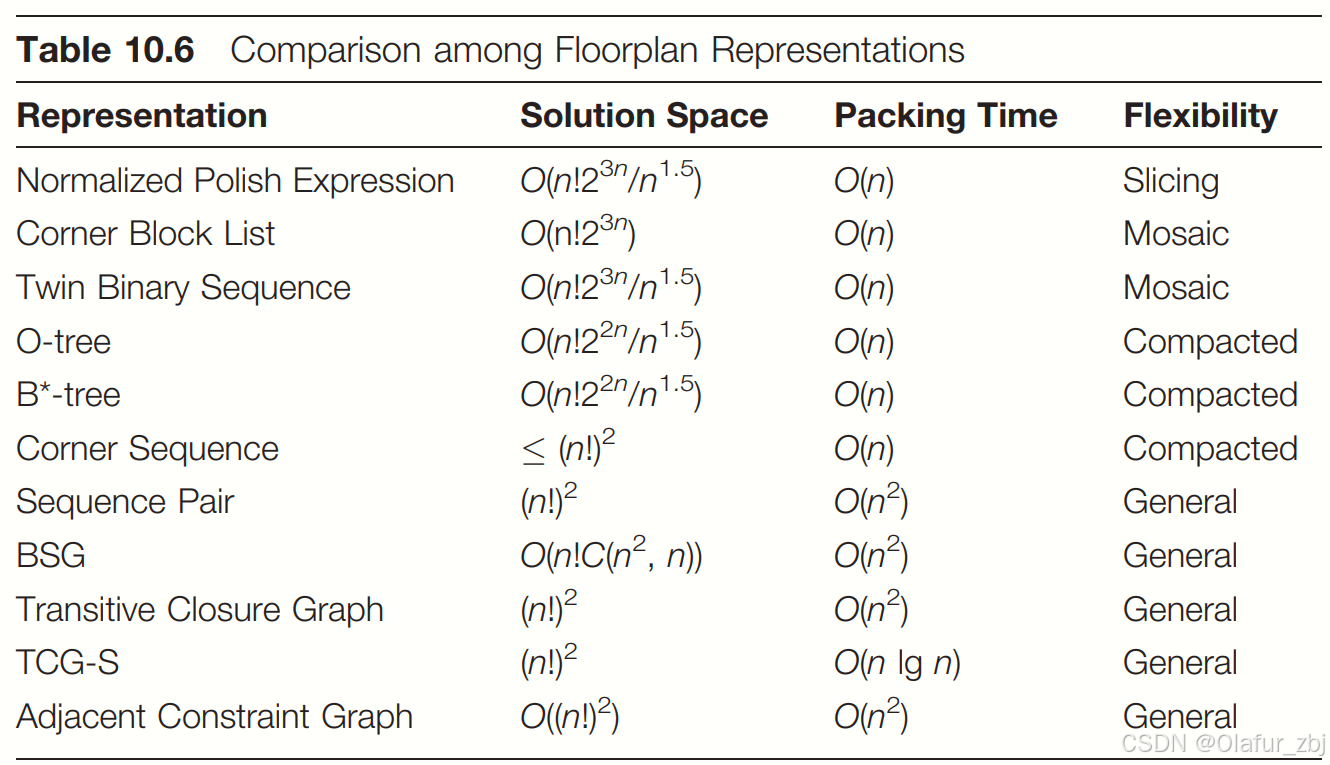

10.2.5 各种布局表示比较

通用布局表示最高的灵活性,其次是紧凑布局,然后是马赛克布局,最后是切分布局。

packing time也就是从表示法恢复出布局的时间。

评估布局表示需要衡量多个维度(1)表示的定义和特性(2)解空间结构(3)邻近扰动操作。不能只通过某一方面衡量哪个表示法更好。。。

10.3 解析法布局

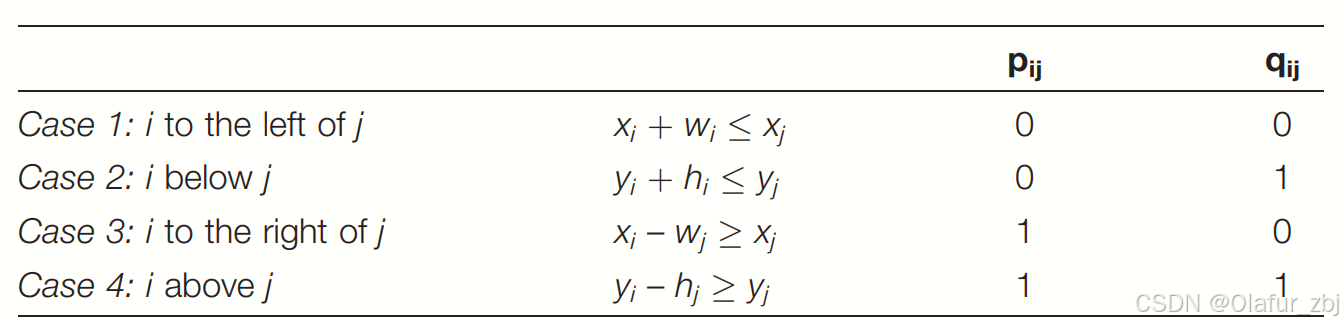

解析法是一种带约束的目标函数优化过程,通常用数学规划方法。对于布局问题,考虑两种基本约束:(1)模块非重叠约束(2)尺寸约束

如果至少满足以下情况之一,则称module i、j不重叠:

引入二元变量pij和qij来表示上述不等式。例如,pij=0和qij=1,表达式yi+hi<=yj成立。

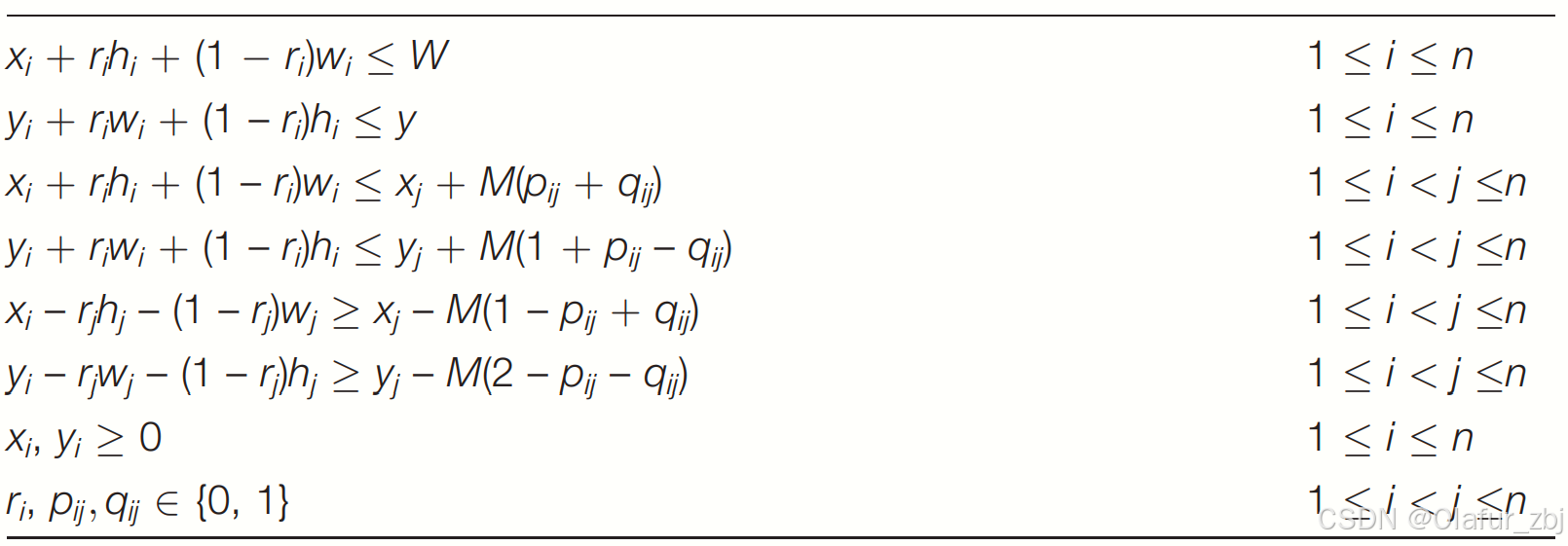

W和H代表布局的外框宽和高。模块非重叠的线性约束如下:

其中1<=i<=j<=n

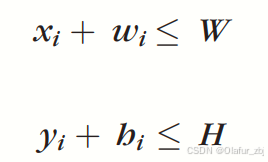

对于尺寸约束,每个模块必须在W、H的画布内。

其中1<=i<=j<=n

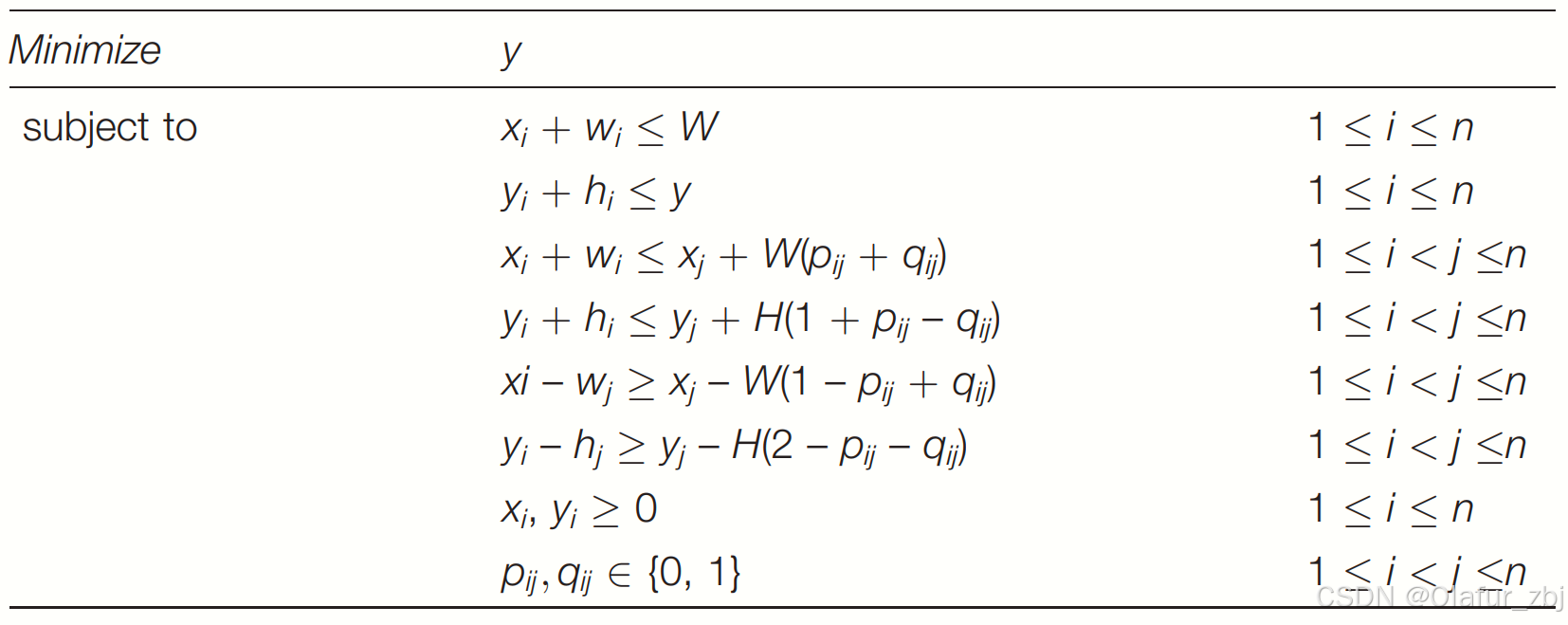

我们的目标是最小化布局面积,xy,x和y是布局的宽和高。面积xy是非线性,非线性优化比线性优化要难,可以转换为:固定布局宽度为W,然后最小化高度y,这样就变成了线性优化问题。修改尺寸约束xi+wi<=W,yi+hi<=y,其中1<=y<=n,y是布局的高度。因此有以下约束:

- 模块之间的非重叠约束

- 模块在画布内的位置约束

- 坐标非负约束

- pij,qij∈{0,1}

这是个混合整数线性规划问题,目标函数和约束都是线性的,问题变成了在给定宽度W下最小化高度y,同时满足下述的不等式约束。

对于n个模块的混合ILP大小,连续变量的数量为O(n),整数变量的数量为O(n2),线性约束的数量为O(n2)。有很多混合ILP的求解器,例如GLPK、CPLEX、LINDO,lp_solve等等。最差时候是指数的时间复杂度,因此大规模的布局问题是很耗时间的,可以divide-and-conquer或者渐进式方法处理。

对于旋转的情况,可以引入二元变量ri,0时不旋转,1时旋转。不等式约束变为:

M=max{W,H}

10.4 现代布局方法

随着设计复杂度的提升,现代布局问题考虑的更多。(1)软模块(2)固定边界约束(3)大规模布局

10.4.1 软模块

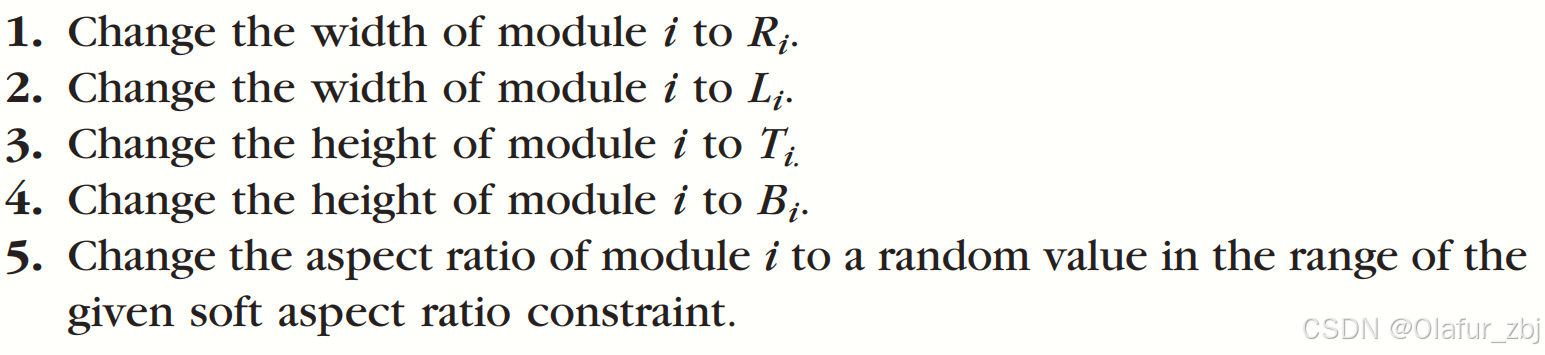

软模块的宽和高是可变的,面积保持不变,因此模块长宽比是一个约束。模拟退火的时候可以改变模块的宽、高:

10.4.2 固定轮廓约束

现代VLSI设计常用固定die尺寸的布局,而不是可变die尺寸布局,单纯优化面积的不考虑固定轮廓的方法可能没啥用,因为到最后可能放不到有限的die面积内。

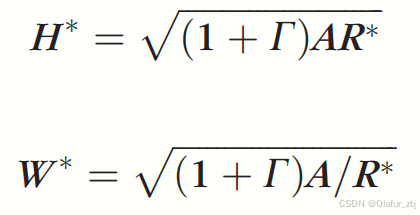

首先构建一个固定轮廓,长宽比是R*,给定的总面积是A,最大死区面积占比是Г,布局长和宽可以表示为:

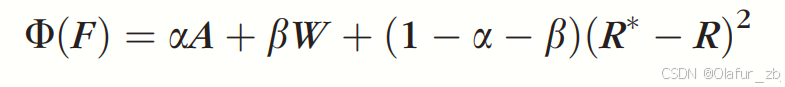

对于固定轮廓的布局,我们调整成本函数,除了线长和面积,还要加入长宽比惩罚。理由(rationale)是如果布局的长宽比跟轮廓的长宽比相似,并且布局的死区空间小于最大百分比Г,那么这个布局可以实现。假设当前布局的长宽比是R,定义布局F的成本函数Φ为:

R*是期望的布局长宽比,R是当前布局的长宽比。

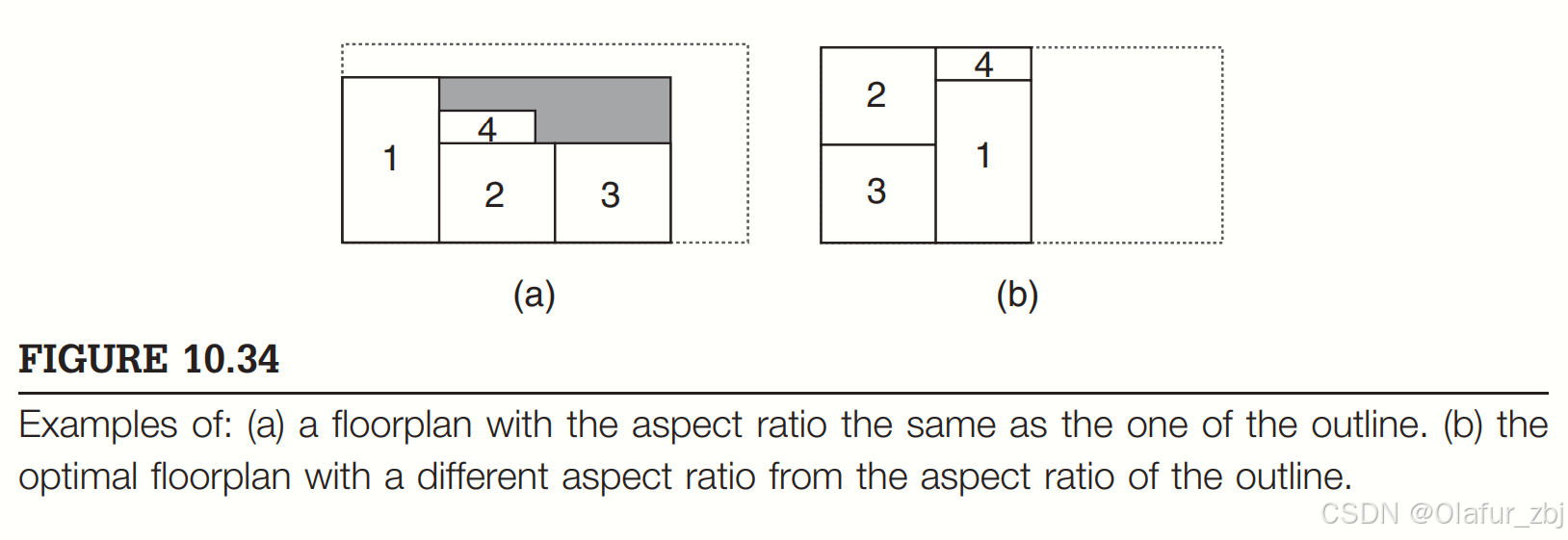

有时候布局的最佳长宽比可能跟外框长宽比差得比较远,例如图10.34.这时候可以降低长宽比惩罚,更多的考虑线长和面积项。可以使用一些自适应方式来做。

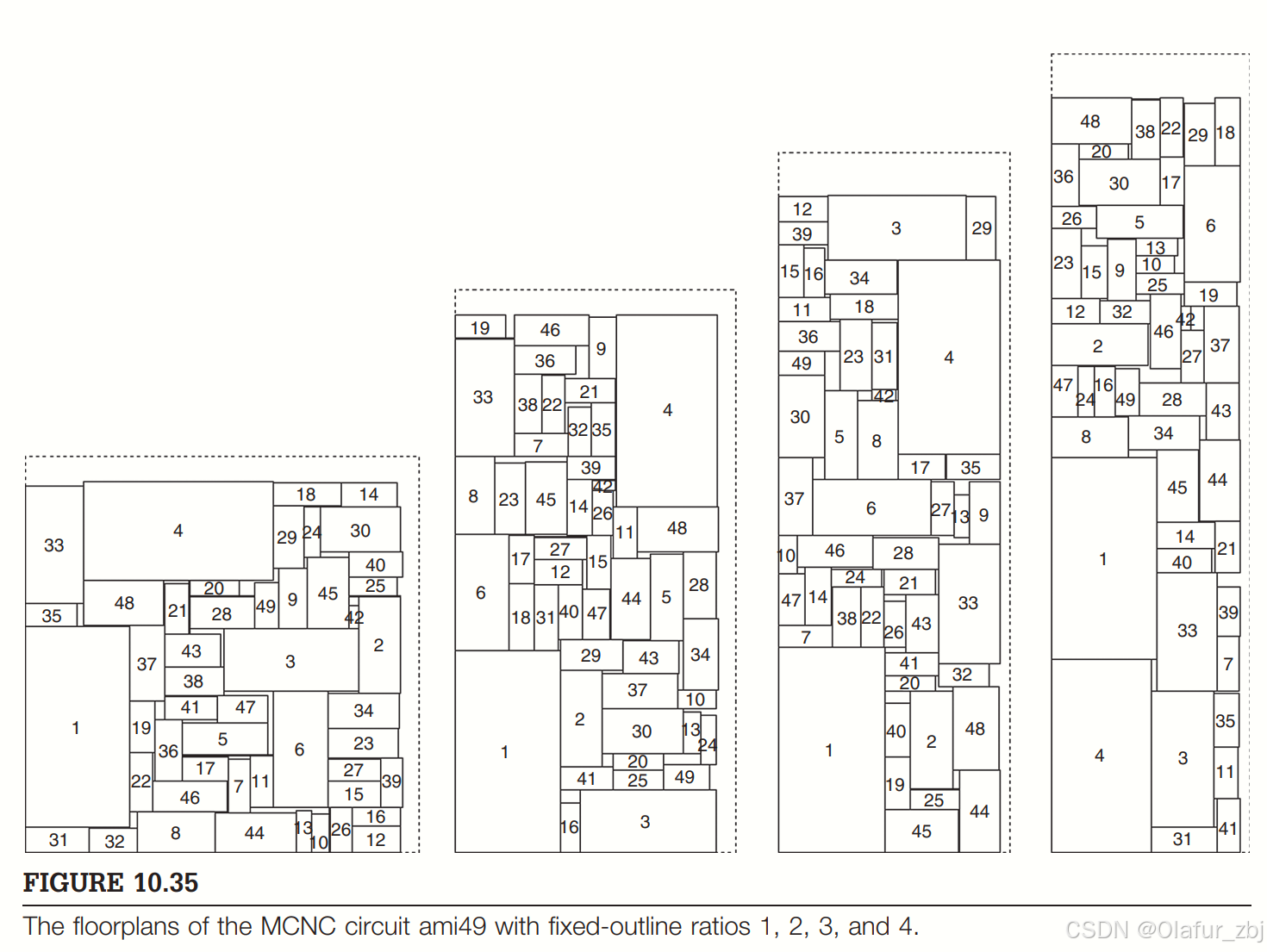

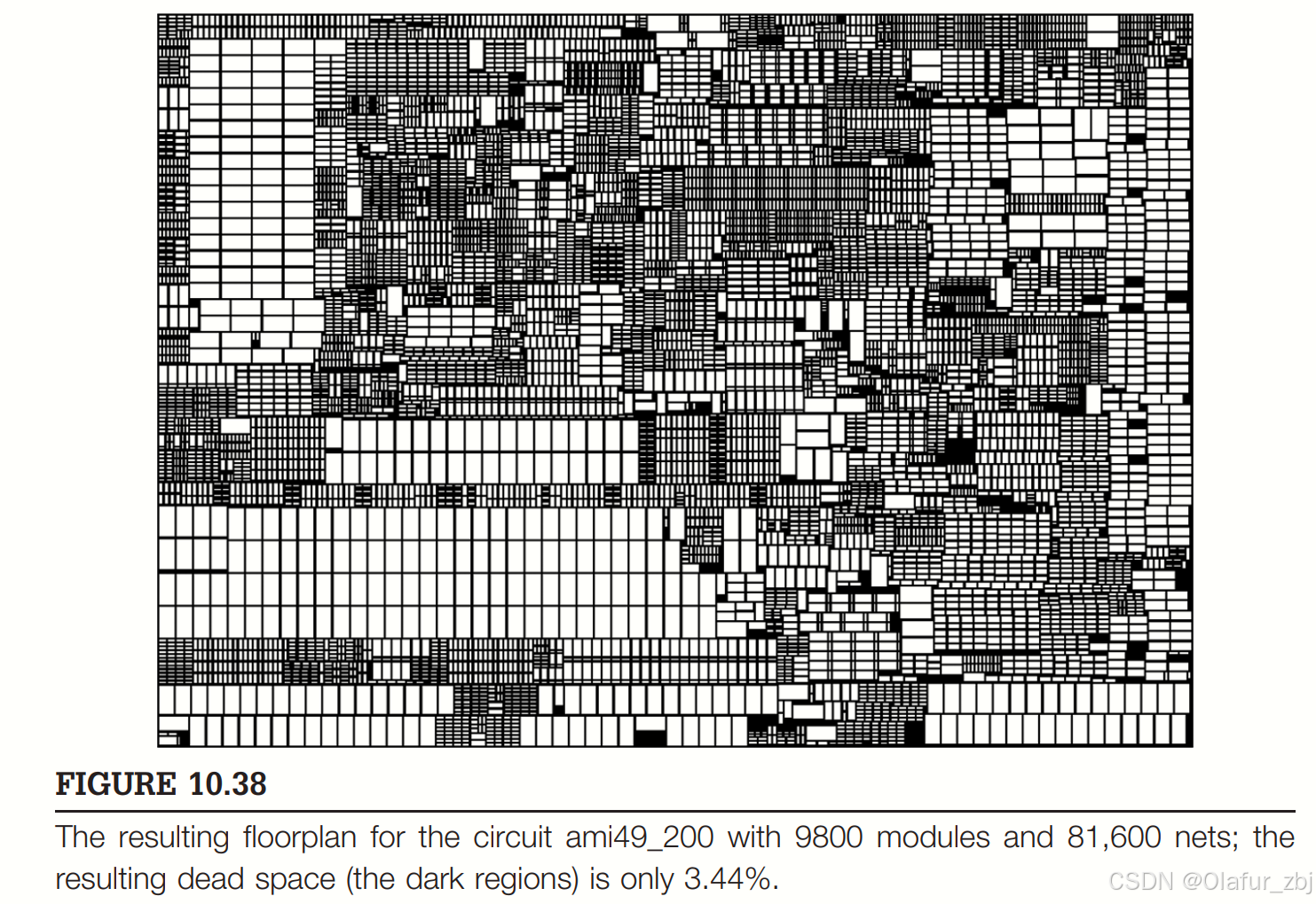

图10.35展示了MCNC电路ami49的不用长宽比ratio的布局结果,有49个module。

10.4.3 大规模电路布局

随着工艺进步,芯片上module的数量越来越多。模拟退火不能高效处理大规模布局问题,层次化的布局方法提出。层次化方法迭代地将布局区域划分成多个子区域然后独立的解这些子问题。Patoma是快速层次化布局器,它基于迭代划分的方法,但是由于子区域是各自独立求解,他们之间的关系无法交互,全局信息丢失。

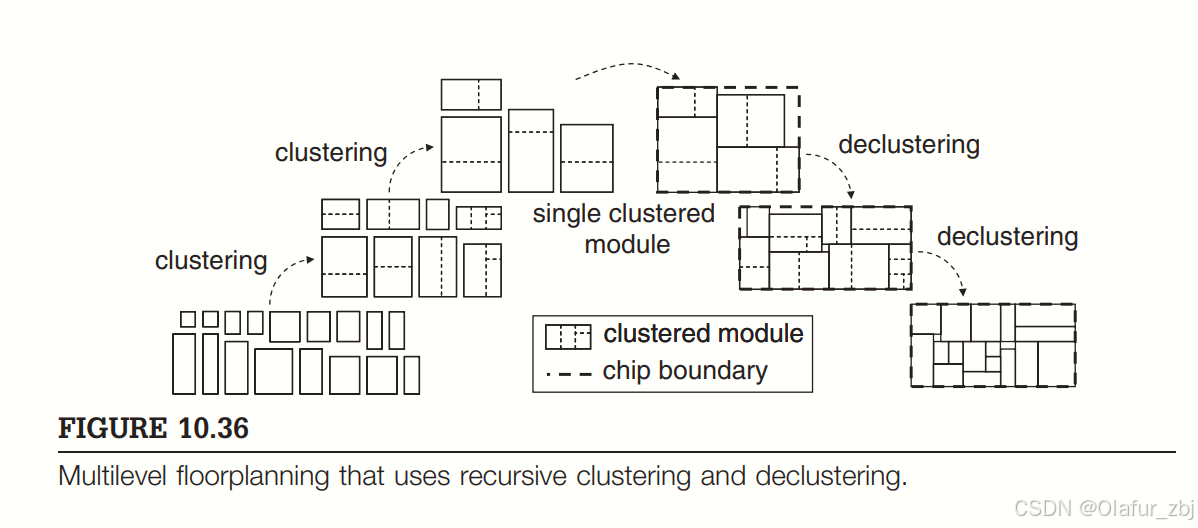

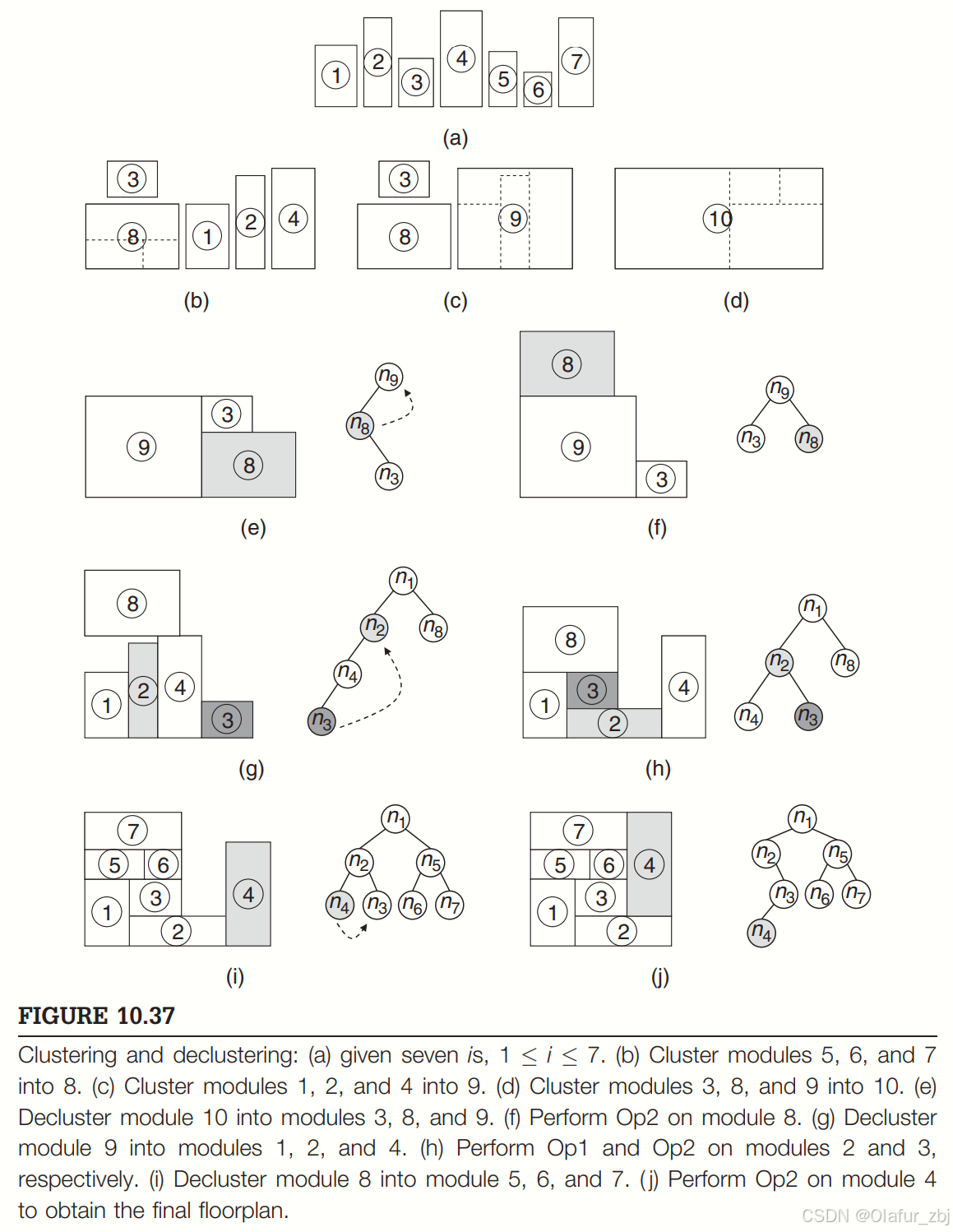

多级布局方法提出,使用自底向上coarsening和自顶向下的uncoarsening方法,如图10.36所示。

先聚类在declustering的方式叫∧-shaped的多级布局,先划分再merge的方式叫V-shaped的多级布局,后者在全局信息的优化上由于前者,因为后者在一开始考虑了全局的配置,全局效应可以在早期被考虑到。

10.4.4 其他

此外还提到了和布局相关的一些内容:

衬底噪声耦合

互连、pipeline

总线驱动的布局

IR驱动的布局

3D布局

603

603

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?