声明

本人经验之谈,仅供参考。

引言

一般来说,我们是不用ila去查看时钟波形的。这会带来时序上的困难。但是在Debug时,我们可能需要判断FPGA内部的某个时钟信号有没有正常工作。在不增加输出管脚的情况下,还是用ila比较方便。

这里分析一下,ila抓取时钟波形需要注意的地方和对时序路径的一些分析。

ila的时钟频率

dubug_hub时钟频率和ila_core时钟频率的关系

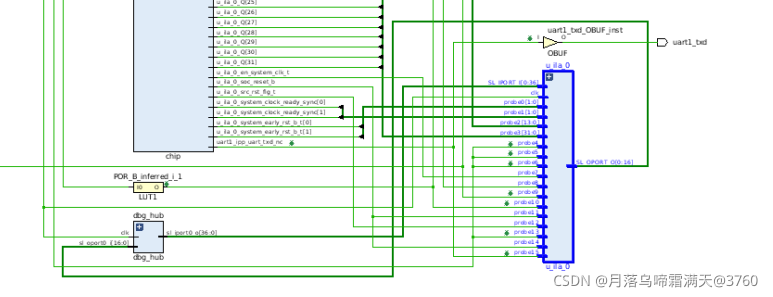

首先vivado在synthesis之后可以在网表中对想查看的信号标记Debug属性。然后工具会根据你选择信号的时钟域的不同生成一个或多个ila_core。每个ila_core只有一个时钟。如果有多个ila_core或者ila_core的时钟频率和dbg_hub的时钟频率不同,那么这些ila_core,会连接到dubug_hub上面。这才构成了完成的ila 网表。如下图所示

duhub_hub的时钟频率会默认和ila_core中最低的时钟频率相同。这个可以在xdc文件或者gui界面进行更改。

dubug_hub的时钟频率和JTAG时钟频率的关系

在上板调试的时候,我们是通过JTAG时钟和fpga通信的。相关的ila波形数据,位流的下载也是通过JTAG进行的。

ila对JTAG时钟频率有要求:dubug_hub的时钟频率应该是JTAG时钟频率的2.5倍之上。

JTAG时钟频率可以在vivado界面调整。但是过低的JTAG时钟频率会导致下载位流的时间过长,这是我们无法忍受的。

JTAG默认时钟频率15M,算出dubug_hub最低时钟37.5M.

所以在进行设计的时候,应该保证上述时钟频率关系。

ila时钟频率和被采样时钟频率

根据采样定理ila时钟频率最好时被采样时钟频率的4倍以上,才可以得到比较好的时钟波形。但是我们只要看时钟是否work就行。只要ila时钟频率比被采样时钟频率高2倍就可以了。

时钟路径时序报告分析

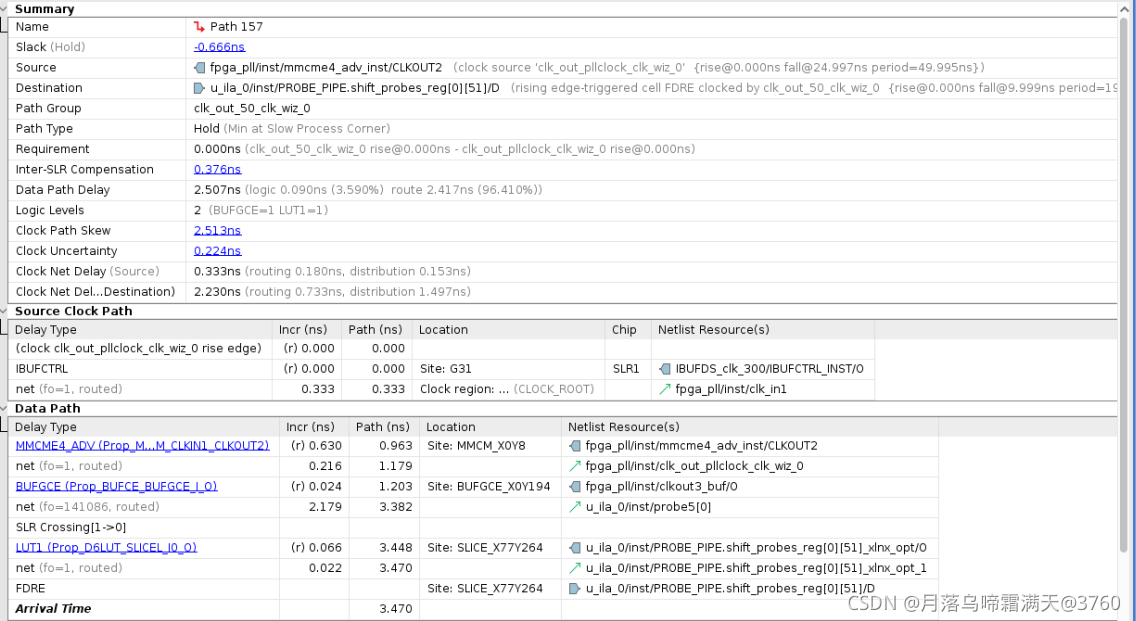

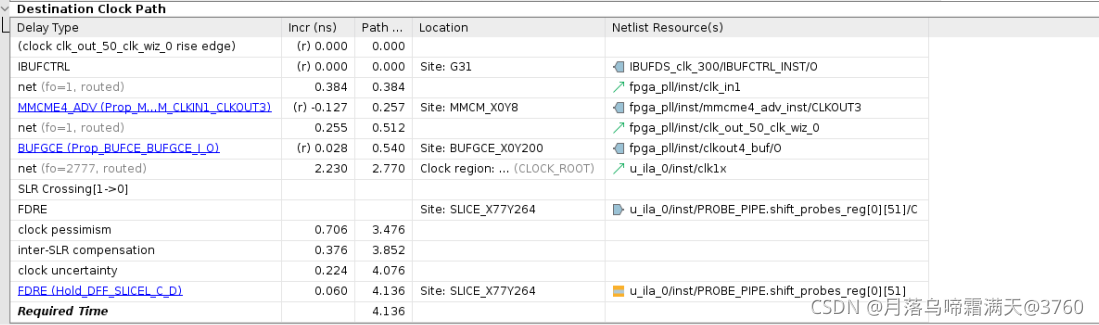

下图时ila对时钟进行采样的路径的时序报告。

他的源时钟路径和数据路径和我们平常看到的路径有点不同。

我们将时钟当作数据进行采集,因此原时钟路径中不包括MMCM,只有IBUFCTRL.

MMCM BUFGCE经常出现在其他时序路径的源时钟路径中,但此处被算到了数据路径中。

本文详细探讨了ILA(Integrated Logic Analyzer)在FPGA设计中的应用,特别是在时钟频率配置和时序分析方面。ILA的时钟频率至少应为被采样时钟的2倍,以确保有效的时钟波形捕获。同时,debug_hub的时钟频率默认与ILA_core中最低时钟相同,但可通过xdc文件或GUI调整,并且该频率应为JTAG时钟的2.5倍以上。此外,ILA的采样率应遵循采样定理,以保证高质量的时钟波形。时序报告分析揭示了ILA如何处理时钟路径的独特性,对于理解和优化FPGA内部时序至关重要。

本文详细探讨了ILA(Integrated Logic Analyzer)在FPGA设计中的应用,特别是在时钟频率配置和时序分析方面。ILA的时钟频率至少应为被采样时钟的2倍,以确保有效的时钟波形捕获。同时,debug_hub的时钟频率默认与ILA_core中最低时钟相同,但可通过xdc文件或GUI调整,并且该频率应为JTAG时钟的2.5倍以上。此外,ILA的采样率应遵循采样定理,以保证高质量的时钟波形。时序报告分析揭示了ILA如何处理时钟路径的独特性,对于理解和优化FPGA内部时序至关重要。

4824

4824

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?