标题

Demonstration of 1.2-kV Rated Novel Power Poly-Si/4H-SiC Heterojunction Diode With Record Low Forward Voltage Drop(TED 24年)

文章的研究内容

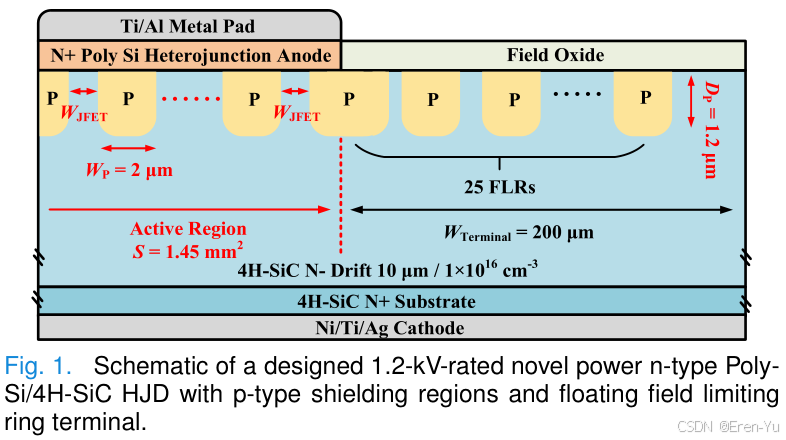

文章的研究内容为开发并实验验证一种新型的1.2千伏额定电压多晶硅(Poly-Si)/4H-碳化硅(SiC)异质结二极管(HJD)。该二极管采用n型离子注入多晶硅阳极,通过优化异质结势垒高度(低至0.804 eV)和引入p型屏蔽区域,实现了创纪录的低正向电压降(1.080 V@2.5 A/mm²),较传统钛金属阳极4H-SiC二极管降低25%。同时,该设计通过以下创新提升了综合性能:

- 反向电流抑制:在800 V反向电压下,室温(298 K)和高温(423 K)下的反向电流密度分别低至1.47 μA/mm²和231 μA/mm²,且雪崩击穿电压超过1500 V。

- 动态性能:双脉冲开关测试表明,二极管具有几乎为零的反向恢复电荷,动态损耗极低。

- 兼容性制造工艺:采用全兼容4H-SiC器件制造流程(如LPCVD沉积、高能离子注入等),确保高质量异质结界面(理想因子n=1.026),避免金属阳极的复杂工艺问题。

研究还通过仿真优化了JFET区域宽度(WJFET=0.75 μm)和p型屏蔽区参数,进一步验证了未来降低高温下反向电流(优化后可达31.8 μA/mm²@423 K)并逼近4H-SiC材料极限的潜力。该二极管在电力电子系统中展现出高效、低损耗的应用前景,是下一代碳化硅功率器件的关键技术突破。

文章的研究方法

1. 器件设计与结构优化

- 异质结界面设计:采用n型多晶硅(Poly-Si)阳极与4H-SiC外延层形成异质结,通过调节多晶硅掺杂浓度降低势垒高度至0.804 eV,从而减少正向电压降(VFV_FVF)。

- p型屏蔽区域:通过高能Al离子注入形成p型区域,抑制反向电流密度(JRJ_RJR)的指数增长,同时提升雪崩击穿电压至1500 V以上。

- JFET区域优化:调整JFET宽度(WJFETW_{\text{JFET}}WJFET)以平衡正向导通电阻(RSR_SRS)与反向泄漏电流,最终确定WJFET=0.75 μmW_{\text{JFET}} = 0.75 \, \mu mWJFET=0.75μm为最优解。

2. 制造工艺开发

- 全兼容工艺:采用与4H-SiC MOSFET兼容的制造流程,包括:

- 多晶硅沉积:低压力化学气相沉积(LPCVD)在700°C下制备500 nm厚n型Poly-Si。

- 高温退火:在1700°C下退火30分钟,激活p型屏蔽区域的Al离子注入。

- 界面处理:牺牲氧化工艺减少表面缺陷,确保异质结界面的高质量(理想因子(n=1.026))。

- 阴极金属化:背面溅射Ti/Ni/Al金属层,并通过激光退火形成欧姆接触。

3. 实验测试与参数提取

- 静态电性能测试:

- 使用Agilent B1505A功率器件曲线示踪仪测量正向III-VVV特性(VF(V_F(VF、RSR_SRS)和反向III-VVV特性(JRJ_RJR、击穿电压)。

- 温度依赖性测试:在298 K至423 K范围内评估高温对JRJ_RJR和VFV_FVF的影响。

- 动态性能测试:

- 双脉冲开关测试平台:验证反向恢复特性,结果显示几乎为零的反向恢复电荷。

- UIS(非钳位电感应力)测试:评估二极管在雪崩状态下的耐压能力。

- 接触电阻测试:通过传输线模型(TLM)测量多晶硅与SiC P+区的接触电阻(RC,sp=1 Ω⋅cm2R_{C,sp} = 1 \, \Omega \cdot cm^2RC,sp=1Ω⋅cm2)。

4. 仿真分析与优化

- TCAD仿真工具(Silvaco):

- 模型校准:基于实验数据校准反向电子隧穿模型和高温载流子行为。

- 参数优化:调整异质结势垒高度(φHJD\varphi_{\text{HJD}}φHJD)、p型屏蔽区的掺杂浓度(1×1018 cm−31 \times 10^{18} \, \text{cm}^{-3}1×1018cm−3至5×1018 cm−35 \times 10^{18} \, \text{cm}^{-3}5×1018cm−3)及深度,进一步降低高温下JRJ_RJR(优化后达31.8 μA/mm²@423 K)。

- 关键参数提取:

- 使用修正的Richardson图(图4(a))提取实际Richardson常数(A∗=157.12 A/(K2cm2)A^* = 157.12 \, \text{A}/(\text{K}^2 \text{cm}^2)A∗=157.12A/(K2cm2))和势垒高度。

- 分析JFET电阻(RJFET,spR_{\text{JFET,sp}}RJFET,sp)对RSR_SRS的贡献(图5)。

5. 对比实验与性能验证

- 与传统JBS二极管对比:

- 正向电压降降低25%(1.080 V vs. 1.400 V)。

- 反向电流密度在高温(423 K)下仍低至231 μA/mm²(传统器件高1-2个数量级)。

- 结构验证:

- SEM图像(图2(b))显示清晰的Poly-Si/SiC界面,无金属合金化反应。

- 雪崩测试(图7©)验证终端结构(25个浮置场限环)的耐压能力(BV > 1500 V)。

6. 材料与界面表征

- SEM与能谱分析:确认异质结界面质量及p型屏蔽区域的几何参数(图2(a)-©)。

- 能带分析:通过能带图(图6(b))解释电子单极传导机制,避免空穴注入导致的双极损耗。

文章的创新点

-

提出了一种新型的低势垒高度(0.804 eV)n型多晶硅/4H-SiC异质结二极管(HJD):这种二极管在2.5 A/mm²的正向电流密度下实现了创纪录的低正向电压降(VF)为1.080 V,比传统的使用钛金属阳极的4H-SiC功率二极管降低了25%。这主要是通过引入和优化p型屏蔽区来实现的,该区域不仅有助于提高雪崩击穿电压至超过1500V,还能有效抑制反向漏电流密度(JR)的增长。

-

展示了与传统材料相比的优势:文章指出,纯金属如钛、铝、钼和镍等由于其较高的功函数,不能满足降低势垒高度的需求。而多晶硅由于其可通过掺杂调整费米能级的特点,能够提供更低的异质结势垒高度,并且具有高熔点和热稳定性,适合制造过程中的高温退火处理。

-

开发了完全兼容的制造工艺:研究中提出的HJD采用了成熟的多晶硅栅电极关键制造工艺,包括沉积、掺杂和蚀刻过程,无需引入额外的制造兼容性问题。这表明n型多晶硅阳极相比于Mo-N薄膜阳极,可以提供一条更为兼容的技术路线,以实现低损耗的4H-SiC功率二极管。

-

性能评估与优化:通过实验验证和Silvaco TCAD仿真分析,进一步优化了异质结势垒高度(ϕHJD)和p型屏蔽区的掺杂浓度及深度,使得在高温下的VF低于1.400 V,同时将423 K温度下的JR显著降低到约31.826 µA/mm²,相较于WJFET为0.75 µm的制造HJD分别减少了18.5%和86.2%。

文章的结论

-

首次实验验证了低势垒高度(0.804 eV)n型多晶硅阳极与p型屏蔽区结合的1.2-kV额定4H-SiC功率异质结二极管(HJD):

- 这种新型HJD在室温(T=298 K)下的正向电压降(VF)达到了创纪录的低值1.080 V。

- 理想因子(n)为1.026,表明该二极管具有近乎理想的整流界面和低缺陷制造工艺。

-

成功提取了n型多晶硅/4H-SiC界面的理查森常数(A)*:

- 提取得到的A*值为157.12 A/(K²cm²),这为未来4H-SiC异质结的研究提供了参考依据。

-

p型屏蔽区的作用显著:

- p型屏蔽区不仅使雪崩击穿电压(BV)保持在1500 V以上,还能有效降低反向漏电流密度(JR)。特别是在高温度(T=423 K)和800 V反向电压下,JR被抑制到231 µA/mm²。

-

通过校准仿真进一步优化性能:

- 通过调整异质结势垒高度(ϕHJD)和p型屏蔽区的掺杂浓度,可以在保持室温下VF低于1.000 V的同时,将高温(T=423 K)下的VF降至1.400 V以下,并将JR显著降低至约31.826 µA/mm²,相较于WJFET为0.75 µm的制造HJD分别减少了18.5%和86.2%。

-

展示了几乎零反向恢复特性和类似的动态性能:

- 双脉冲开关测试平台验证了这种二极管具有几乎零反向恢复特性和类似的动态性能,这对于电力电子应用中的高效能至关重要。

-

Ron,sp指标证明了其作为下一代4H-SiC功率二极管的潜力:

- 文章指出,所提出的HJD作为一种下一代4H-SiC功率二极管,在降低损耗方面具有巨大的潜力。Ron,sp(特定导通电阻)指标显示,这种新型HJD在降低VF和提升整体功率损失优势方面表现出色。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?