实现步骤

1、建立工程

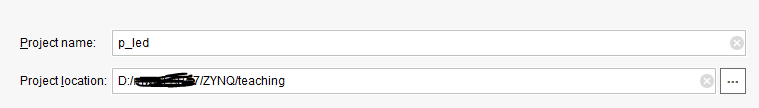

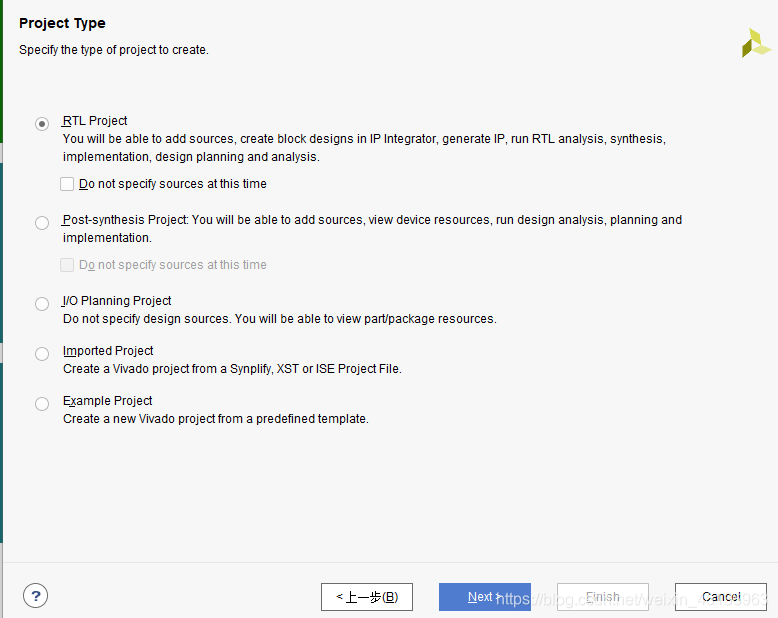

create Project----------Next------工程命名为p_led,并选择文件保存路径

-----------Next

-----------Next-----------Next--------器件选择(按照直接的开发板信号进行选择)

-----------Next-----------finish

2、添加源文件

Add source-------Add or create design sources-------next-------create file ------

--------OK-----------finish--------OK--------YES

3、编写源文件

`timescale 1ns / 1ps

//

四个灯一起闪烁

//module led(

// input sys_clk,

// input rst_n,

// output reg [3:0] led

// );

// reg [31:0] timer_cnt;

// always @(posedge sys_clk or negedge rst_n)

// begin

// if(!rst_n)//复位

// begin

// led<=4'd0;

// timer_cnt<=32'd0;

// end

// else if (timer_cnt>=32'd49_999_999)

// begin

// led=~led;

// timer_cnt<=32'd0;

// end

// else

// begin

// led<=led;

// timer_cnt<=timer_cnt+32'd1;

// end

// end

//endmodule

// 四个灯依次闪烁

module led(

input sys_clk,

input rst_n,

output reg [3:0] led

);

reg [31:0] timer_cnt;

always @(posedge sys_clk or negedge rst_n)

begin

if(!rst_n)//复位

begin

led<=4'd0;

timer_cnt<=32'd0;

end

else if (timer_cnt>=32'd49_999_999)//计数记到1秒

begin

led=led+1'b1;//如果计数到1s,+1

timer_cnt<=32'd0;

end

else

begin

led<=led;

timer_cnt<=timer_cnt+32'd1;

end

end

endmodule

四个灯左移,

//module led(

// input sys_clk,

// input rst_n,

// output reg [3:0] led

// );

// reg [31:0] timer_cnt;

// always @(posedge sys_clk or negedge rst_n)

// begin

// if(!rst_n)//复位

// begin

// led<=4'd0001;

// timer_cnt<=32'd0;

// end

// else if (timer_cnt>=32'd49_999_999)//计数记到1秒

// begin

// led<={led[2:0],led[3]}; //左移

// timer_cnt<=32'd0;

// end

// else

// begin

// led<=led;

// timer_cnt<=timer_cnt+32'd1;

// end

// end

//endmodule

4、添加约束文件

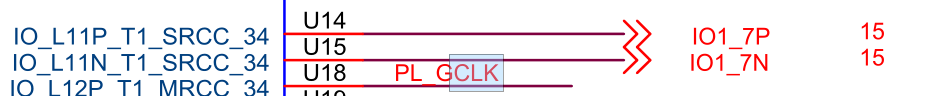

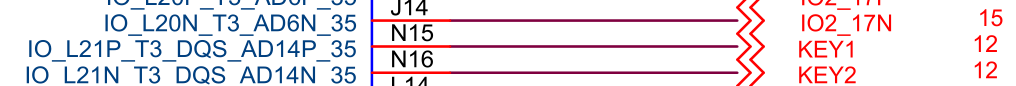

open Elaborated Design-------OK---------Window----------

I/O ports ----------根据原理图添加管脚约束

需要注意的是,这里的复位按键用原理图的key1实现。

--------保存-----file name为led---------OK

打开led.XDC可以看到约束文件。

也可以按照如何格式进行编写约束文件

5、添加时钟约束

run synthesis--------OK-------waiting…--------点击 cancel ----------点击 open synthesis design-----constrains wizard -----------next-------频率选择50MHz

-----skip to finish-----finish----返回到led.XDC ------Reload (多了一行时钟约束)

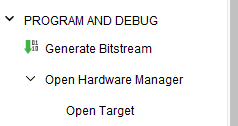

6、生成比特流文件

点击generate bitstream----YES-------OK------------cancel-----开发板上电连接----open hardwaremanager----open target

-----auto conneted

点击 program device—按照如下路径选择生成的比特流文件------OK-----program-

点击 program device—按照如下路径选择生成的比特流文件------OK-----program-

完成led的点亮实验。

2960

2960

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?